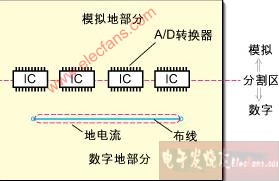

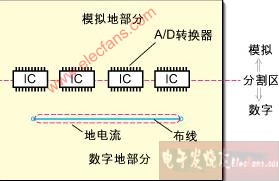

混合信號PCB的分區設計原則

混合信號電路PCB的設計很復雜,元器件的布局、布線以及電源和地線的處理

2009-03-25 11:40:23 1154

1154

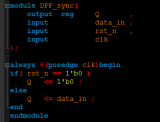

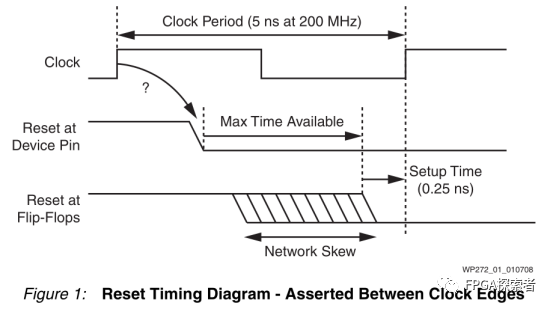

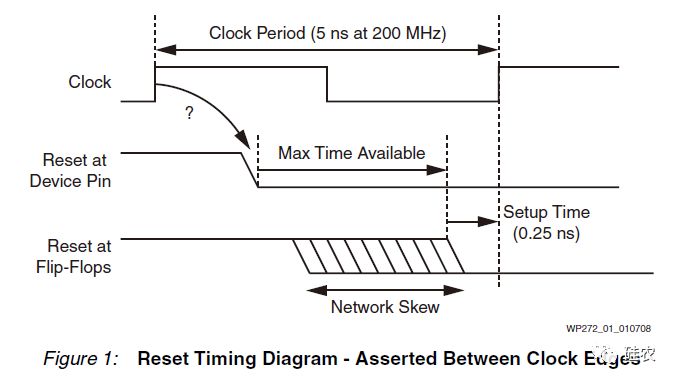

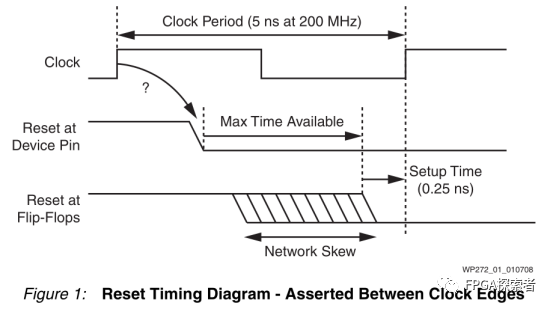

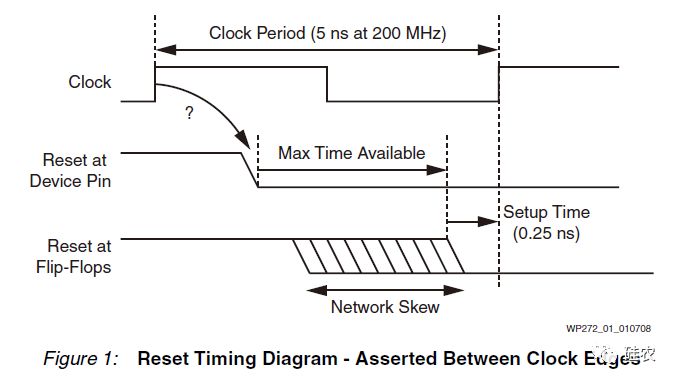

對FPGA設計中常用的復位設計方法進行了分類、分析和比較。針對FPGA在復位過程中存在不可靠復位的現象,提出了提高復位設計可靠性的4種方法,包括清除復位信號上的毛刺、異步復位同步釋放、采用專用全局

2014-08-28 17:10:03 9365

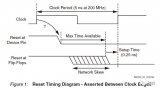

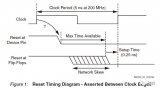

9365 異步復位信號a是異步復位信號源,異步復位信號b、c、d是到達觸發器的異步信號。我們可以看到,b信號是在本周期就撤離了復位;c信號則由于復位恢復時間不滿足,則可能導致觸發器輸出亞穩態;而d信號則由于延時太長(但是滿足了復位去除時間),在下一個周期才撤離復位。

2020-06-26 05:36:00 24583

24583

本篇文章參考Xilinx White Paper:Get Smart About Reset: Think Local, Not Global 在沒看這篇文章前,回想一下平時我們常用的復位方式

2020-11-18 17:32:38 6564

6564 內都是將復位信號作為一個I/O口,通過撥碼開關硬件復位。后來也看了一些書籍,采用異步復位同步釋放,對自己設計的改進。 不過自從我研讀了Xilinx的White Paper后,讓我對復位有了更新的認識

2020-12-25 12:08:10 3230

3230

復位信號在數字電路里面的重要性僅次于時鐘信號。 對電路的復位往往是指對觸發器的復位,也就是說電路的復位中的這個“電路”,往往是指觸發器,這是需要注意的。

2023-04-21 09:16:49 1146

1146

針對異步復位、同步釋放,一直沒搞明白在使用同步化以后的復位信號時,到底是使用同步復位還是異步復位?

2023-06-21 09:59:15 2281

2281

在前面的文章中有過對于寄存器行為的描述,而復位方面,在電路設計時建議使用帶異步復位/置位的寄存器。

2023-07-13 17:33:58 1904

1904

復位信號幾乎是除了時鐘信號外最常用的信號了,幾乎所有數字系統在上電的時候都會進行復位,這樣才能保持設計者確定該系統的系統模式的狀態,以便于更好的進行電子設計,并且在任意時刻,確保使用者總能對電路系統進行復位,使電路從初始的狀態開始工作。

2023-07-27 09:48:30 12093

12093

在前面的文章中有過對于寄存器行為的描述,而復位方面,在電路設計時建議使用帶異步復位/置位的寄存器。

2023-08-01 16:04:11 5103

5103

復位信號在數字電路里面的重要性僅次于時鐘信號。對一個芯片來說,復位的主要目的是使芯片電路進入一個已知的,確定的狀態。

2023-08-27 10:18:51 3117

3117

復位信號在數字電路里面的重要性僅次于時鐘信號。對電路的復位往往是指對觸發器的復位,也就是說電路的復位中的這個“電路”,往往是指觸發器,這是需要注意的。

2023-09-13 16:26:49 2469

2469

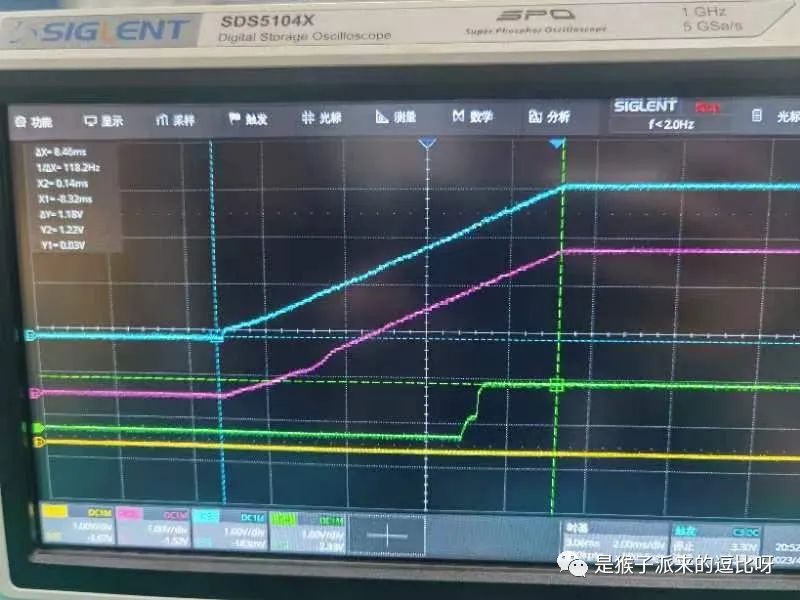

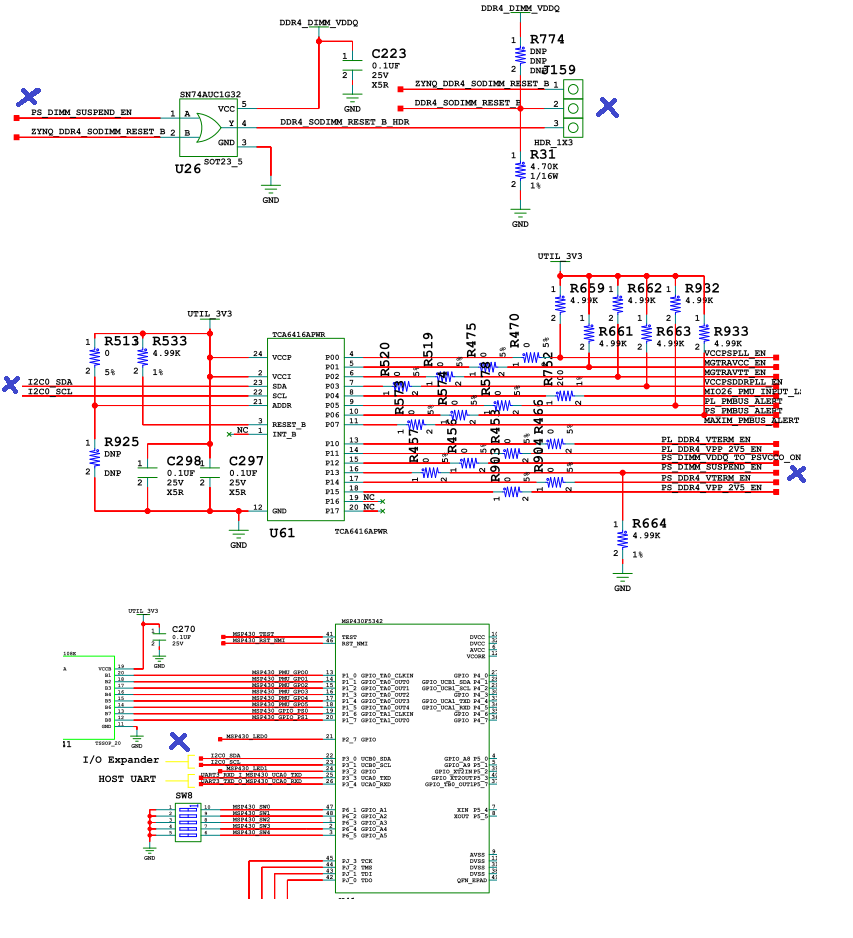

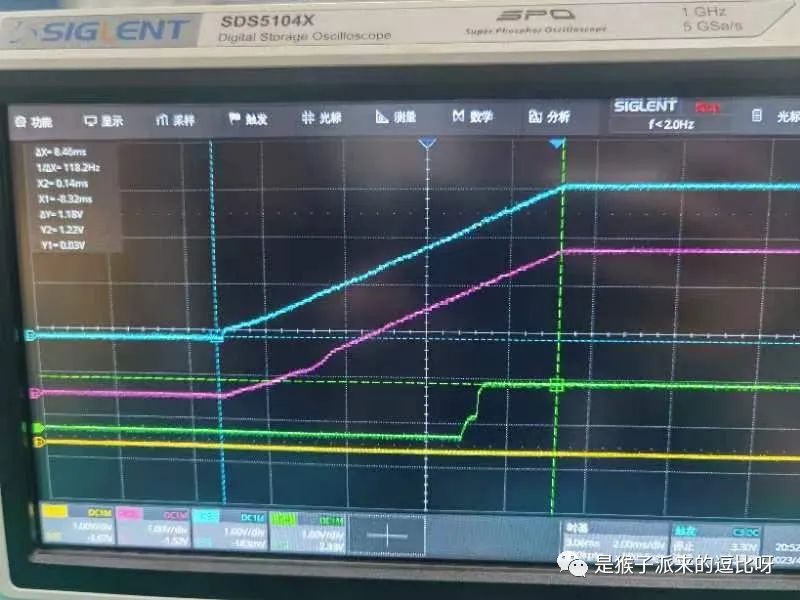

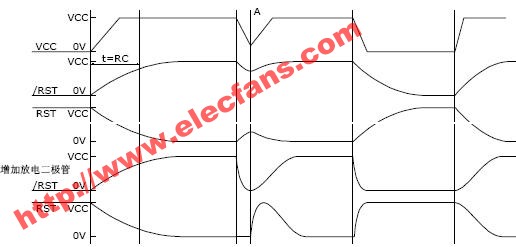

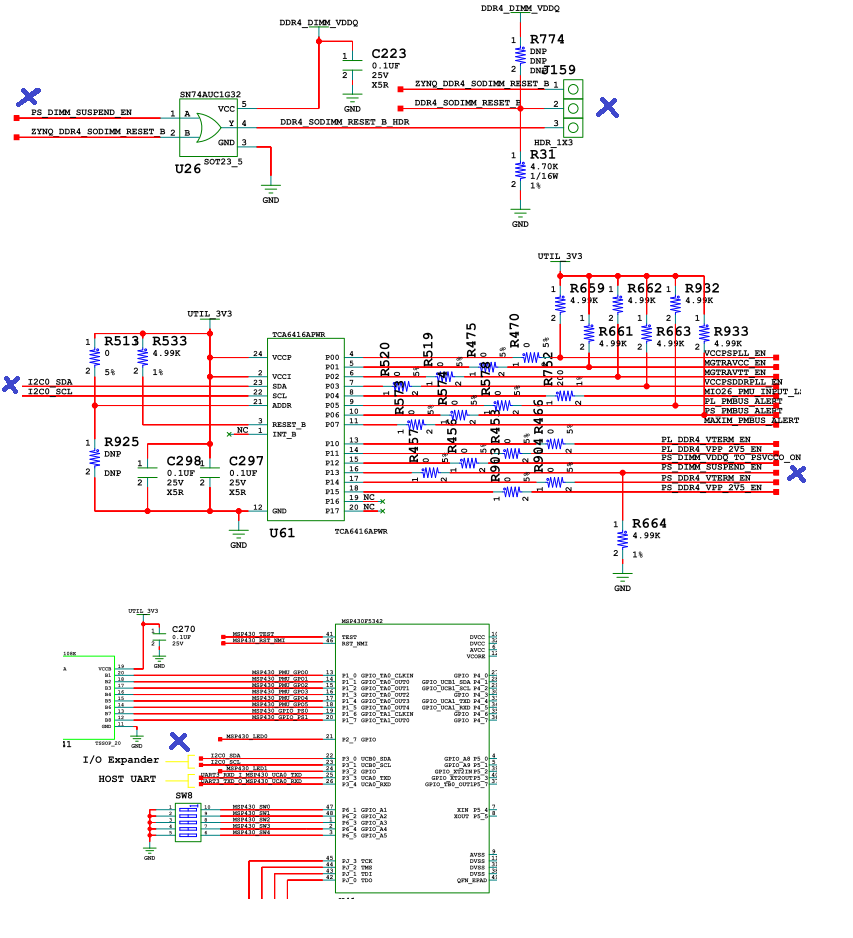

藍色的是3.3V上電信號(除個別芯片使用其他電壓外,整板使用3.3V供電),粉紅色的復位信號(此處的復位信號是低電平有效的RC接反相器之后的輸出),橫軸每格為2ms,縱軸每格為1V。復位信號的產生

2023-11-22 15:03:07 12234

12234

經常在面試時問到一個問題:對于芯片中的復位信號我們通常會有哪些特殊處理?這個時候我一般希望得到的回答包括:復位消抖、異步復位同步撤離、降頻復位、關斷時鐘復位和復位保護等處理方案。

2023-12-25 09:52:56 4468

4468

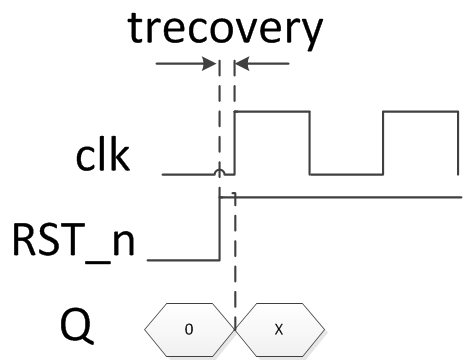

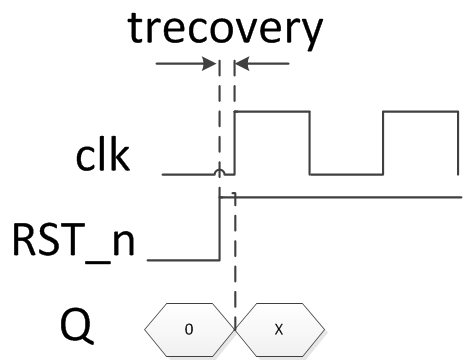

一般來說,復位信號有效后會保持比較長一段時間,確保 register 被復位完成。但是復位信號釋放時,因為其和時鐘是異步的關系,我們不知道它會在什么時刻被釋放。

2024-01-24 09:32:15 2670

2670

Xilinx Artix7 DEVB_124X92MM 6~16V

2023-03-28 13:05:55

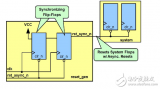

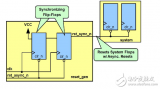

Xilinx-ZYNQ7000系列-學習筆記(3):系統復位與啟動一、復位ZYNQ-7000 SoC系統中的復位可以由硬件、看門狗定時器、JTAG控制器或軟件產生,可用于驅動系統中每個模塊的復位信號

2022-01-25 06:49:13

Xilinx-ZYNQ7000系列-學習筆記(3):系統復位與啟動一、復位ZYNQ-7000 SoC系統中的復位可以由硬件、看門狗定時器、JTAG控制器或軟件產生,可用于驅動系統中每個模塊的復位信號

2022-01-25 07:05:36

個MUX。利用這種2+1的組合可以產生DDR操作,Xilinx稱之為ODDR2。每個存儲單元都有6個接口信號:時鐘+時鐘時能,數據輸入+輸出,置位復位+翻轉輸入除了這些信號,存儲單元還有一些屬性設置

2012-08-02 22:48:10

信號完整性處理的8個基本原則

2021-01-14 07:19:08

需要注意以下幾個要點:●盡可能使用FPGA的專用復位引腳。(特權同學,版權所有)●上電復位時間的長短需要做好考量。(特權同學,版權所有)●確保系統正常運行過程中復位信號不會誤動作。(特權同學,版權所有) Xilinx FPGA入門連載

2019-04-12 06:35:31

FPGA引腳信號指配有什么原則?

2021-04-30 07:04:56

3W原則,例如時鐘線,差分線,視頻、音頻信號線,復位信號線及其他系統關鍵電路需要遵循3W原則,而并不是板上所有的布線都要強制符合3W原則。 滿足3W原則能使信號間的串擾減少70%,而滿足10W則能使信號

2020-09-27 16:49:19

ADAPTER TC2050 FOR XILINX CABLE

2023-03-22 19:59:52

我很抱歉,如果這是一個愚蠢的問題,因為似乎答案應該在我面前,但我無法弄清楚。Xilinx VC707評估板中的復位信號在哪里?它沒有在主約束文件中列出,我似乎無法在示例VC707項目中找到它。人們如何將電路重置為此電路板上的已知狀態?提前致謝

2020-04-01 08:54:50

圖中,可看到啟動轉換前送入一個復位信號,搞不清這個復位信號是內部產生的,還是外部操作復位引腳產生的,因在手冊中數字復位與同步信號章節,提到SYNC_IN加入一脈沖,會使得數字模塊發生內部復位,該復位與圖中復位時同一個復位信號嗎!實際開啟采集,需每次給這個信號嗎?

2023-12-11 06:15:17

大家好我有一個關于如何處理virtex 5中的復位信號的問題。用于復位整個設計的同步復位信號。復位信號的時序很難滿足,因為扇出很大。如果我減少synplify pro中的扇出限制。我為其余的東西留下了很多復雜的線條。這需要很多邏輯。應該有更好的解決方案。有人可以幫助嗎?問候小東宇

2020-06-03 08:18:11

的時候,其間距應該遵循3W原則,例如時鐘線,差分線,視頻、音頻信號線,復位信號線及其他系統關鍵電路需要遵循3W原則,而并不是板上所有的布線都要強制符合3W原則。20H原則:由于電源層與地層之間的電場是變化

2019-05-08 08:30:00

`手機Layout中信號布線原則介紹 ,整個文檔內容如下,非常不錯的資料,在這里跟大家分享了[hide] [/hide]`

2011-12-20 11:21:38

設備,直接威脅鐵路正常的安全生產。所以,加強信號設備防雷工作尤為重要。鐵路信號綜合防雷整治的原則鐵路信號設備本身的電磁兼容性應符合《鐵道信號電氣設備電磁兼容性試驗及其限制》(TB/T3073-2003

2012-02-03 14:05:25

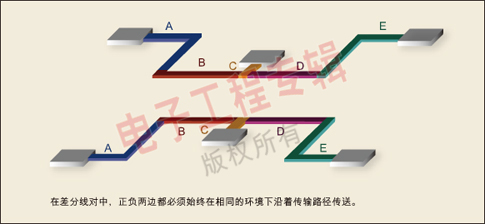

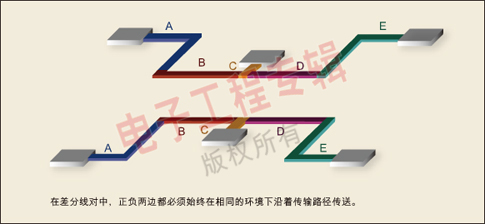

差分信號走線原則

差分線對的工作原理是使接收到的信號等于兩個互補并且彼此互為參考的信號之間的差值,因此可以極大地降低信

2008-05-09 10:00:36 40672

40672

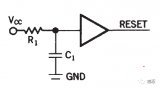

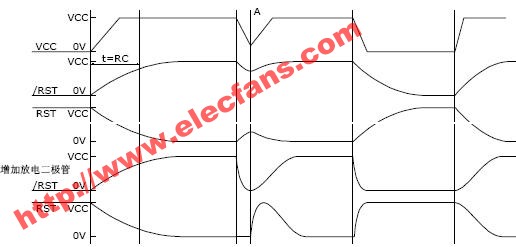

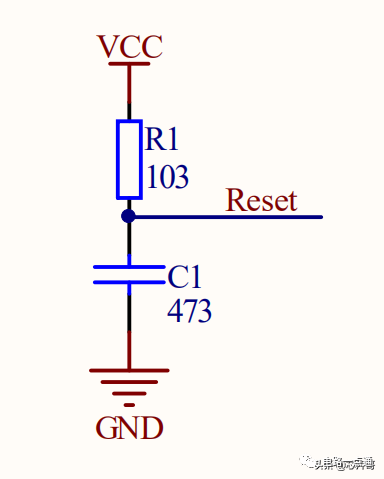

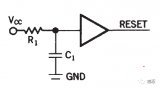

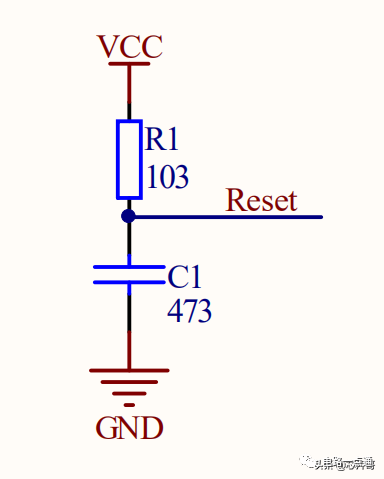

RC復位電路

復位電路的基本功能是:系統上電時提供復位信號,直至系統電源穩定后,撤銷復位信號。為可靠起見,電

2008-10-24 15:30:29 3778

3778

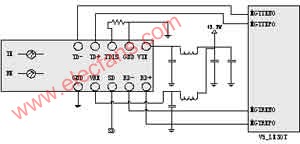

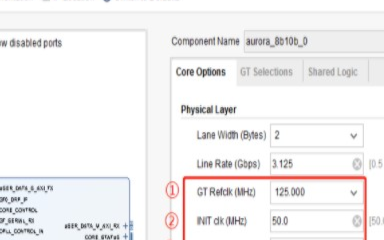

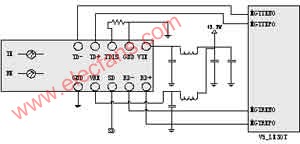

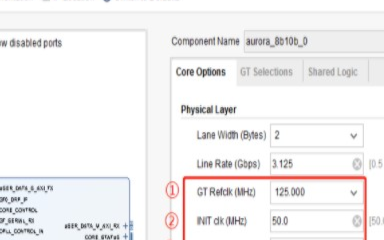

本文設計的基于Xilinx FPGA的千兆位以太網及E1信號的光纖傳輸系統采用Xilinx XC5VLX30T芯片,通過以太網測試儀和數據誤碼儀對本系

2010-07-06 09:09:10 3060

3060

本實用新型公開了一種復位電路及具有所述復位電路的電視機。本實用新型通過采用分立元器件組建復位電路為電視機內部控制系統提供上電復位信號

2011-11-11 17:25:54 45

45 上一篇寫了基于Xilinx FPGA的通用信號發生器的案例,反響比較好,很多朋友和我探討相關的技術,其中就涉及到信號的采集,為了使該文更有血有肉,我在寫一篇基于Xilinx FPGA的通用信號采集器,望能形成呼應,以解答大家的疑問。

2017-02-11 03:11:37 2134

2134

在Xilinx 的FPGA器件中,全局的復位/置位信號(Global Set/Reset (GSR))(可以通過全局復位管腳引入)是幾乎絕對可靠的,因為它是芯片內部的信號。

2017-02-11 11:46:19 1232

1232

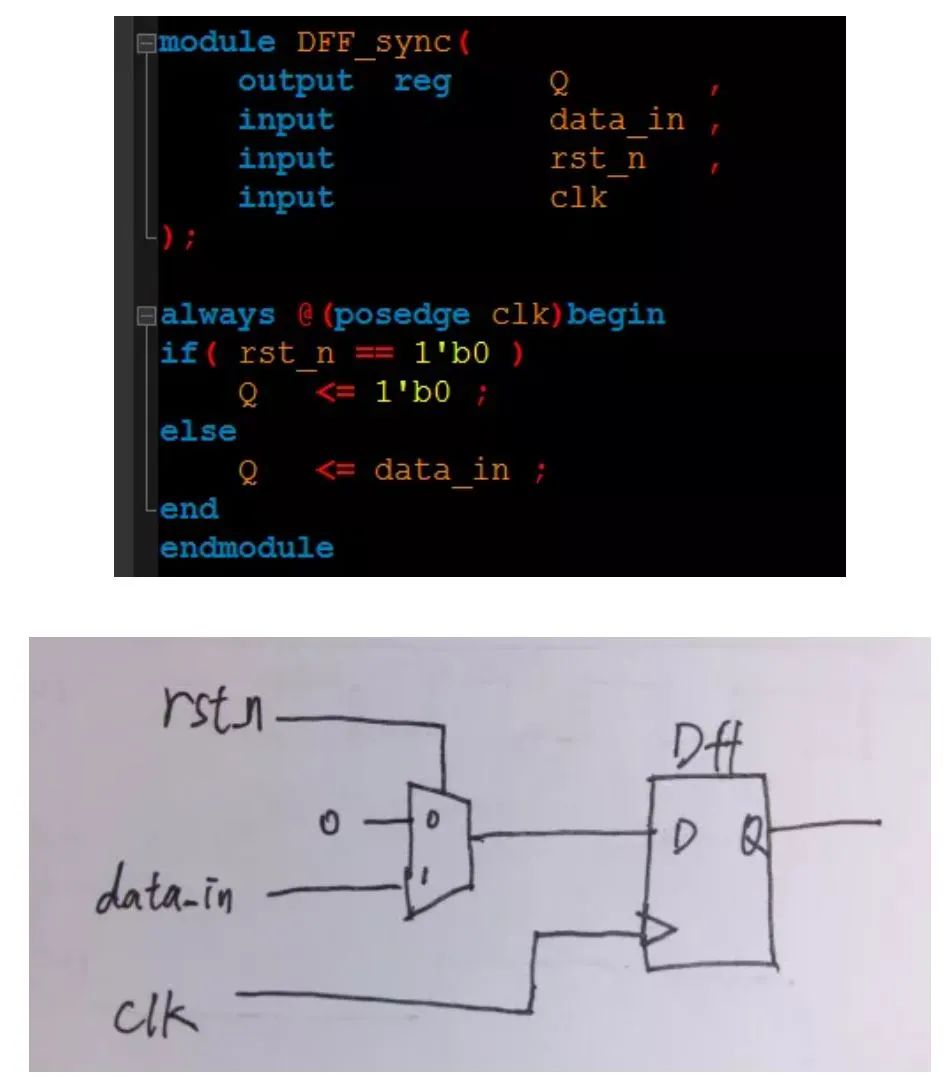

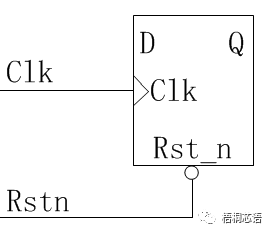

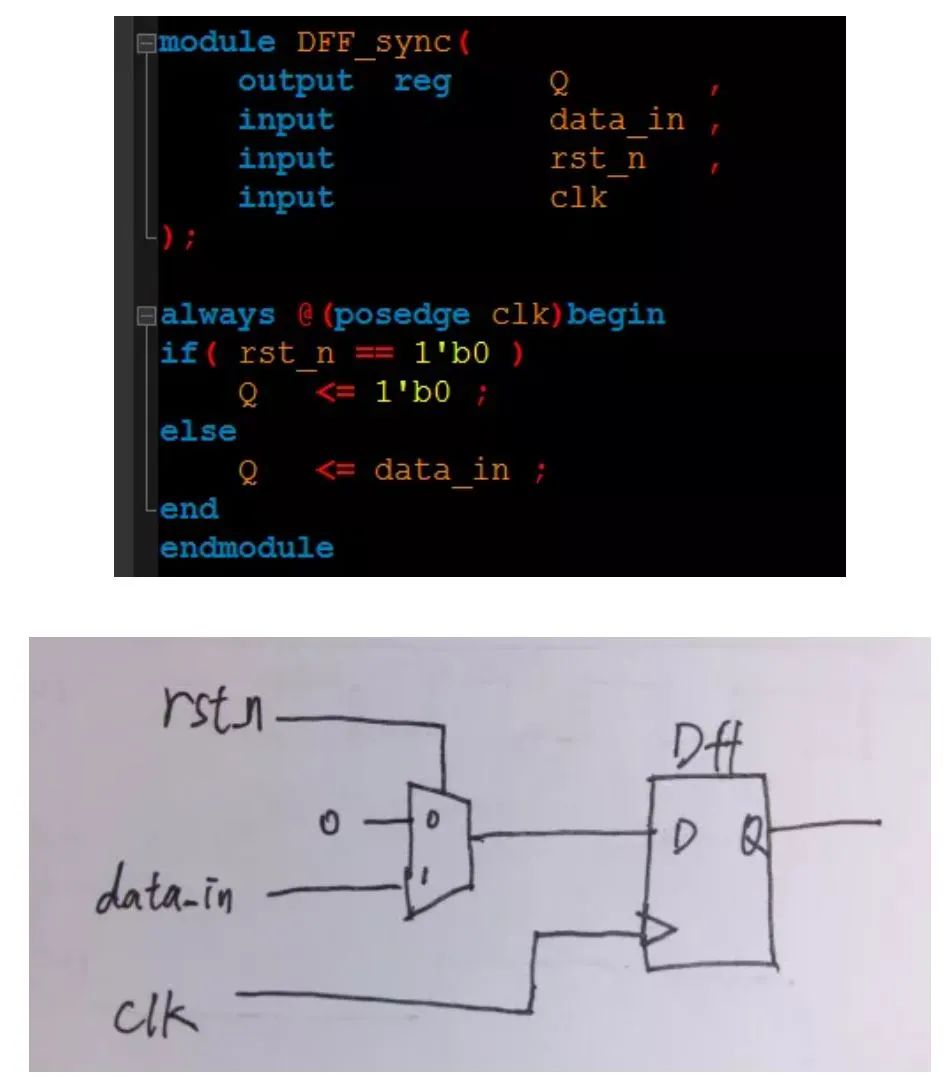

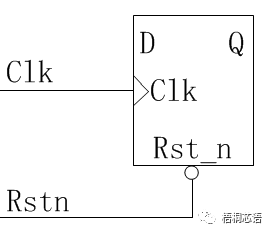

顧名思義,同步復位就是指復位信號只有在時鐘上升沿到來時,才能有效。否則,無法完成對系統的復位工作。

2017-02-11 12:40:11 8741

8741

系統的復位系統由POR和PUC信號驅動,各種不同的事件能觸發產生這些復位信號,而根據不同的復位信號會產生不同的初始化狀態。

2017-09-21 15:59:59 1

1 在FPGA設計中,復位起到的是同步信號的作用,能夠將所有的存儲元件設置成已知狀態。在數字電路設計中,設計人員一般把全局復位作為一個外部引腳來實現,在加電的時候初始化設計。全局復位引腳與任何其它輸入

2017-11-22 17:03:45 6340

6340

異步復位原理:異步復位只要有復位信號系統馬上復位,因此異步復位抗干擾能力差,有些噪聲也能使系統復位,因此有時候顯得不夠穩定,要想設計一個好的復位最好使用異步復位同步釋放。

2017-11-30 08:45:46 99838

99838

是指復位信號是異步有效的,即復位的發生與clk無關。后半句“同步釋放”是指復位信號的撤除也與clk無關,但是復位信號是在下一個clk來到后起的作用(釋放)。

2017-11-30 08:58:14 25411

25411

在帶有復位端的D觸發器中,當reset信號“復位”有效時,它可以直接驅動最后一級的與非門,令Q端“異步”置位為“1”or“0”。這就是異步復位。當這個復位信號release時,Q的輸出由前一級的內部輸出決定。

2017-11-30 09:15:37 12892

12892

POR是上電復位信號,它只在以下兩個事件發生時產生:1、芯片上電。2、RST/NMI設置成復位模式,在RST/NMI引腳上出現低電平信號。

2018-04-10 16:15:32 7694

7694 Xilinx公司將講述:靈活混合信號處理技術演示。

2018-06-01 11:47:00 4225

4225 對于xilinx 7系列的FPGA而言,flip-flop支持高有效的異步復/置位和同步復位/置位。對普通邏輯設計,同步復位和異步復位沒有區別,當然由于器件內部信號均為高有效,因此推薦使用高有效的控制信號,最好使用高有效的同步復位。輸入復位信號的低有效在頂層放置反相器可以被吸收到IOB中。

2018-07-13 09:31:00 7577

7577 通常情況下,復位信號的異步釋放,沒有辦法保證所有的觸發器都能在同一時間內釋放。觸發器在A時刻接收到復位信號釋放是最穩定的,在下一個時鐘沿來臨被激活,但是如果在C時刻接收到復位信號釋放無法被激活,在B時刻收到復位信號釋放,則會引起亞穩態。

2018-11-19 10:34:01 10313

10313

嵌入式世界2012的Xilinx 7系列模擬混合信號評估平臺演示

2018-11-22 06:24:00 3726

3726 xilinx推薦盡量不復位,利用上電初始化,如果使用過程中需要復位,采用同步高復位。

2019-02-14 14:29:49 6928

6928 在普通印制電路板的布線中由于信號是低速信號,所以在3W原則的基本布線規則下按照信號的流向將其連接起來,一般都不會出現問題。但是如果信號是100M以上的速度時,布線就很有講究了。由于最近布過速度高達300M的DDR信號,所以仔細說明一下DDR信號的布線原則和技巧。

2019-03-24 10:00:06 8668

8668

異步復位同步釋放是指復位信號是異步有效的,即復位的發生與clk無關。后半句“同步釋放”是指復位信號的撤除也與clk無關,但是復位信號是在下一個clk來到后起的作用(釋放)。

2019-11-20 07:06:00 4715

4715 同步復位和異步復位都是狀態機的常用復位機制,圖1中的復位電路結合了各自的優點。同步復位具有時鐘和復位信號之間同步的優點,這可以防止時鐘和復位信號之間發生競爭條件。但是,同步復位不允許狀態機工作在直流時鐘,因為在發生時鐘事件之前不會發生復位。與此同時,未初始化的I/O端口可能會遇到嚴重的信號爭用。

2019-08-12 15:20:41 8229

8229

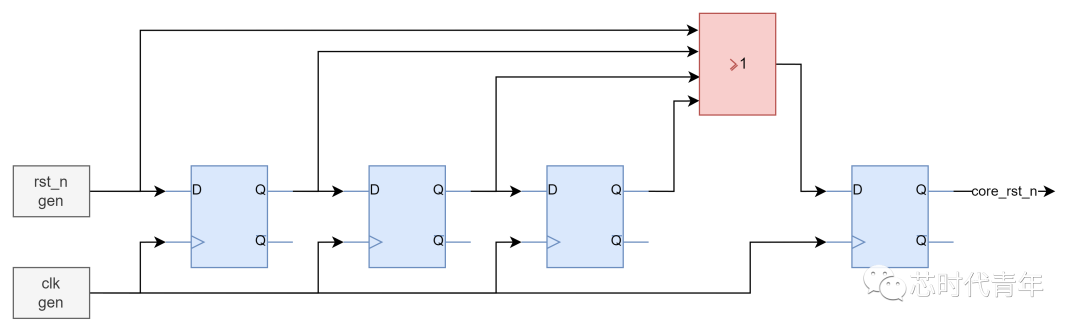

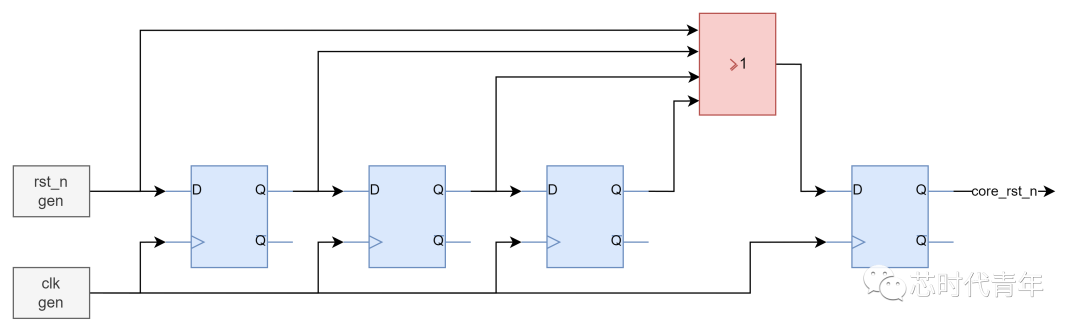

先用FPGA的外部輸入時鐘clk將FPGA的輸入復位信號rst_n做異步復位、同步釋放處理,然后這個復位信號輸入PLL,同時將clk也輸入PLL。設計的初衷是在PLL輸出有效時鐘之前,系統的其他部分都保持復位狀態。

2020-03-29 17:19:00 3320

3320

同步復位:顧名思義,同步復位就是指復位信號只有在時鐘上升沿到來時,才能有效。否則,無法完成對系統的復位工作。用Verilog描述如下:異步復位:它是指無論時鐘沿是否到來,只要復位信號有效,就對系統進行復位。用Verilog描述如下:

2020-09-14 08:00:00 0

0 Xilinx的開發板ZCU102支持休眠到內存(suspend-to-ram)。休眠到內存時,DDR進入自刷新,MPSoC被關電,完全不耗電。喚醒時,MPSoC根據外部輸入信號判斷出不是上電啟動而是

2020-11-04 17:02:46 3389

3389

線的時候,其間距應該遵循3W原則,例如時鐘線,差分線,視頻、音頻信號線,復位信號線及其他系統關鍵電路需要遵循3W原則,而并不是板上所有的布線都要強制符合3W原則。 滿足3W原則能使信號間的串擾減少70%,而滿足10W則能使信號間的串擾減少近

2022-12-26 09:35:56 2103

2103 最近看 advanced fpga 以及 fpga 設計實戰演練中有講到復位電路的設計,才知道復位電路有這么多的門道,而不是簡單的外界信號輸入系統復位。 流程: 1. 異步復位: 優點:⑴大多數

2020-10-30 12:17:55 951

951 ,其間距應該遵循 3W 原則,例如時鐘線,差分線,視頻、音頻信號線,復位信號線及其他系統關鍵電路需要遵循 3W 原則,而并不是板上所有的布線都要強制符合 3W 原則。 滿足 3W 原則能使信號間的串擾減少 70%,而滿足 10W 則能使信號間的串擾減少近 98%。 3W 原則

2023-02-01 16:53:07 6055

6055 遵循 3W 原則,例如時鐘線,差分線,視頻、音頻信號線,復位信號線及其他系統關鍵電路需要遵循 3W 原則,而并不是板上所有的布線都要強制符合 3W 原則。

2020-12-16 14:49:00 23

23 本文檔的主要內容詳細介紹的是如何使用Xilinx的FPGA對高速PCB信號實現優化設計。

2021-01-13 17:00:59 26

26 針對異步復位、同步釋放,一直沒搞明白在使用同步化以后的復位信號時,到底是使用同步復位還是異步復位?

2021-04-27 18:12:10 5626

5626

有客戶在產品的設計中,使用外部IC的GPIO通過連接NRST引腳來對STM32MCU進行復位控制時,會遇到以下問題:IC可以對MCU進行復位控制,但是芯片內部的復位信號(如看門狗等)不能對MCU進行復位,甚至影響引腳功能

2021-04-28 15:16:41 19

19 一、復位電路概述 復位信號在數字電路里面的重要性僅次于時鐘信號。對電路的復位往往是指對觸發器的復位,也就是說電路的復位中的這個“電路”,往往是指觸發器,這是需要注意的。有的電路需要復位信號,就像

2021-06-28 09:49:22 7534

7534 產品在設計中某些狀態下需要MCU進行復位,華大MCU包含了7個復位信號來源,每個復位信號都可以讓 CPU 重新運行,絕大多數寄存器會被復位到復位值,程序計數器 PC 會被復位指向 00000000。

2021-10-12 11:24:40 2436

2436 對于硬件設計來說,復位電路是必不可少的一部分,為了確保微機系統中電路穩定可靠工作,復位電路的第一功能是上電復位。在 FPGA 設計中,復位起到的是同步信號的作用,能夠將所有的存儲元件設置成已知狀態

2021-11-06 09:20:57 20

20 MSP430的復位信號有2種: 文檔: 上電清除信號(PUC)、 上電復位信號(POR)。 個人理解: POR是第一次上電復位,PUC是在帶電的情況下發生復位,冷啟動和熱啟動

2021-12-16 16:56:51 12

12 MSP430的復位信號有2種: 文檔: 上電清除信號(PUC)、 上電復位信號(POR)。 個人理解: POR是第一次上電復位,PUC是在帶電的情況下發生復位,冷啟動和熱啟動

2021-12-16 16:57:09 11

11 第二篇文章——STM32電源、復位、時鐘電源管理電源電壓調節器可編程電壓監測器(PVD: Programmable voltage detector )低功耗模式復位Cortex-M3的復位信號

2022-01-05 14:25:10 10

10 對于我們使用Xilinx或其他的成熟IP而言,IP相當于一個黑匣子,內部實現的邏輯功能我們知道,但是控制不了,只能默認OK;一般而言,成熟IP都是經過反復驗證和使用,確實沒有什么問題。所以,IP能不能用,首先要做的就是確保時鐘和復位。

2022-02-19 18:30:07 8249

8249

復位信號在數字電路里面的重要性僅次于時鐘信號。對電路的復位往往是指對觸發器的復位,也就是說電路的復位中的這個“電路”,往往是指觸發器,這是需要注意的。

2022-03-22 08:53:24 9923

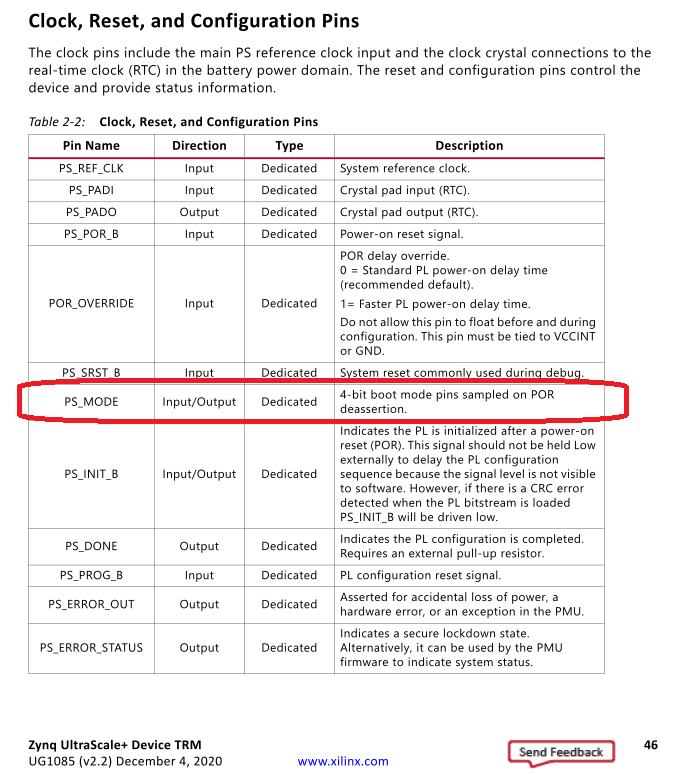

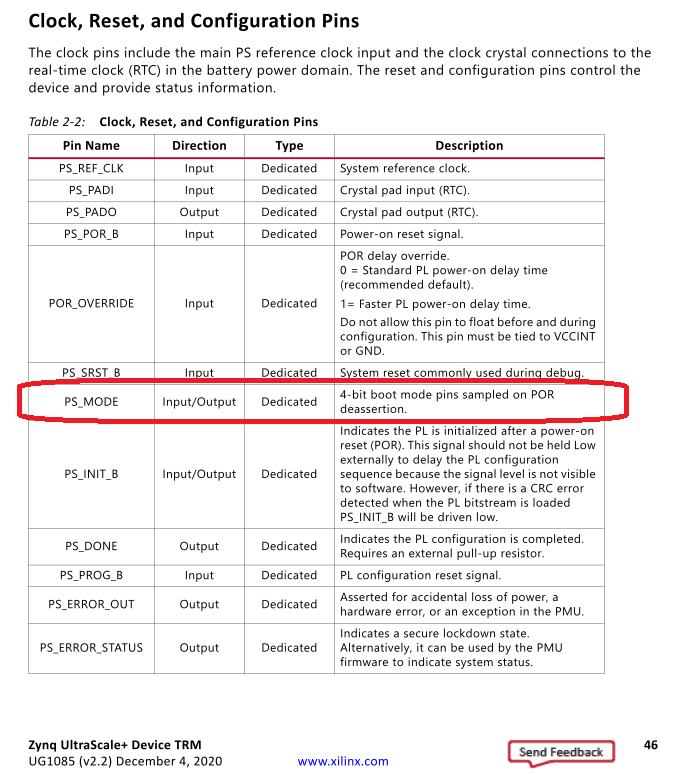

9923 在Xilinx的ZCU102和ZCU106單板設計中,使用了管腳PS_MODE1作為外部USB Phy的復位信號。在MPSoC的文檔ug1085和ug1087中,關于PS_MODE1的信息比較少。下面是更詳細的描述。

2022-08-02 09:38:51 3180

3180

對于很多新入門工程師來講,很少會評估是否需要復位信號,絕大所數都是使用提供的模板,對所有的信號進行復位,盡管可能不是那么必要,如果是這樣會增加資源,對復位時序也會產生影響,所以評估是否需要復位是很有必要的。

2022-09-05 14:50:15 1807

1807 復位信號在數字電路里面的重要性僅次于時鐘信號。對一個芯片來說,復位的主要目的是使芯片電路進入一個已知的,確定的狀態。主要是觸發器進入確定的狀態。在一般情況下,芯片中的每個觸發器都應該是可復位的。

2022-09-19 10:07:20 35609

35609 FPGA設計中幾乎不可避免地會用到復位信號,無論是同步復位還是異步復位。我們需要清楚的是復位信號對時序收斂、資源利用率以及布線擁塞都有很大的影響。

2023-03-30 09:55:34 1882

1882 1、定義 復位信號是一個脈沖信號,它會使設計的電路進入設定的初始化狀態,一般它作用于寄存器,使寄存器初始化為設定值;其脈沖有效時間長度必須大于信號到達寄存器的時延,這樣才有可能保證復位的可靠性

2023-04-06 16:45:02 2170

2170 現在的FPGA正變得越來越復雜,向引腳分配信號的任務曾經很簡單,現在也變得相當繁復。下面這些用于向多用途引腳指配信號的指導方針有助于設計師根據最多到最少的約束信號指配原則提前考慮信號指配,并減少反復的次數。

2023-05-04 17:38:53 1487

1487 復位信號在數字電路里面的重要性僅次于時鐘信號。 對電路的復位往往是指對觸發器的復位,也就是說電路的復位中的這個“電路”,往往是指觸發器,這是需要注意的。

2023-05-18 09:08:08 3611

3611

復位信號在數字電路里面的重要性僅次于時鐘信號。對電路的復位往往是指對觸發器的復位,也就是說電路的復位中的這個“電路”,往往是指觸發器,這是需要注意的。

有的電路需要復位信號,就像是有的電路需要時鐘信號那樣,而有的電路是不需要復位信號的。

2023-05-25 14:31:21 1154

1154

jtag端口的復位信號jtag_trst用于復位TAP狀態機模塊,該復位信號可選。

2023-05-25 15:09:43 1568

1568

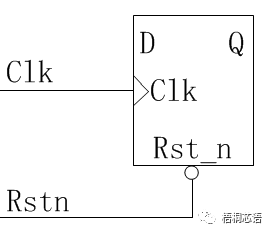

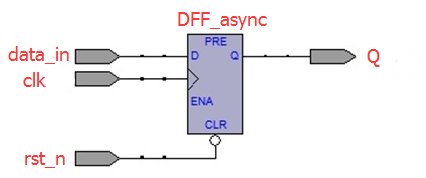

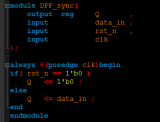

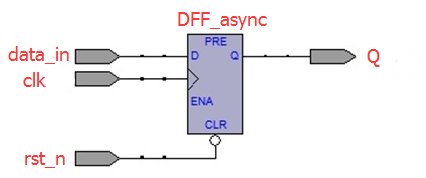

異步復位觸發器則是在設計觸發器的時候加入了一個復位引腳,也就是說**復位邏輯集成在觸發器里面**。(一般情況下)低電平的復位信號到達觸發器的復位端時,觸發器進入復位狀態,直到復位信號撤離。帶異步復位的觸發器電路圖和RTL代碼如下所示:

2023-05-25 15:57:17 1867

1867

復位信號幾乎是除了時鐘信號外最常用的信號了,幾乎所有數字系統在上電的時候都會進行復位,這樣才能保持設計者確定該系統的系統模式的狀態,以便于更好的進行電子設計,并且在任意時刻,確保使用者總能對電路系統進行復位,使電路從初始的狀態開始工作。

2023-06-02 15:11:58 2986

2986

盡量少使用復位,特別是少用全局復位,能不用復位就不用,一定要用復位的使用局部復位;

2023-06-21 09:55:33 3471

3471

對于復位信號的處理,為了方便我們習慣上采用全局復位,博主在很長一段時間內都是將復位信號作為一個I/O口,通過撥碼開關硬件復位。

2023-06-21 10:39:25 1904

1904

能不復位盡量不用復位,如何判斷呢?如果某個模塊只需要上電的時候復位一次,工作中不需要再有復位操作,那么這個模塊可以不用復位,用上電初始化所有寄存器默認值

2023-06-28 14:44:46 1754

1754

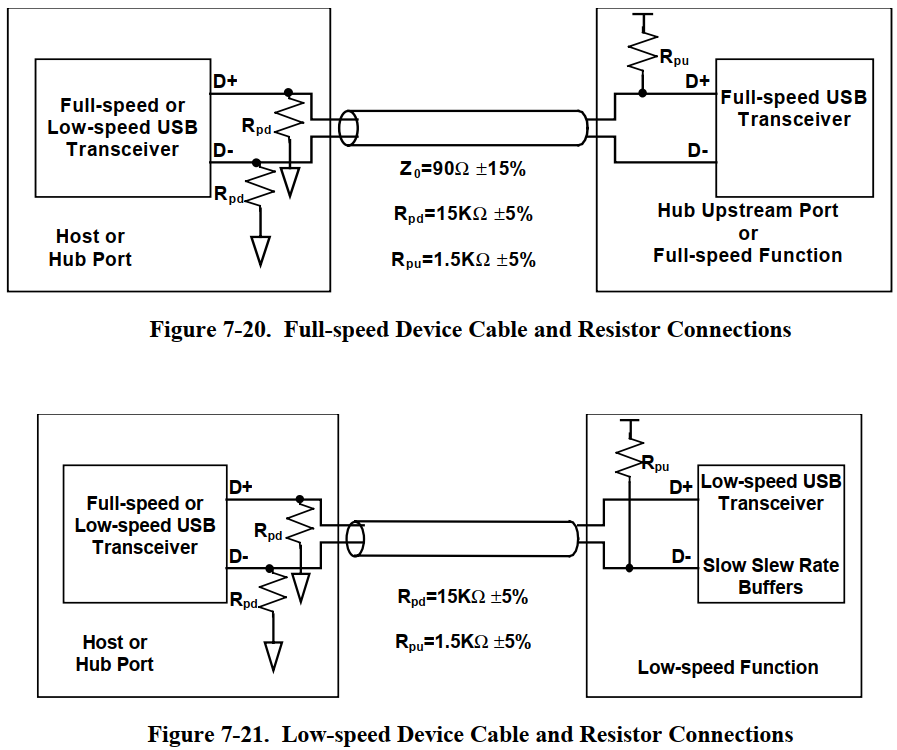

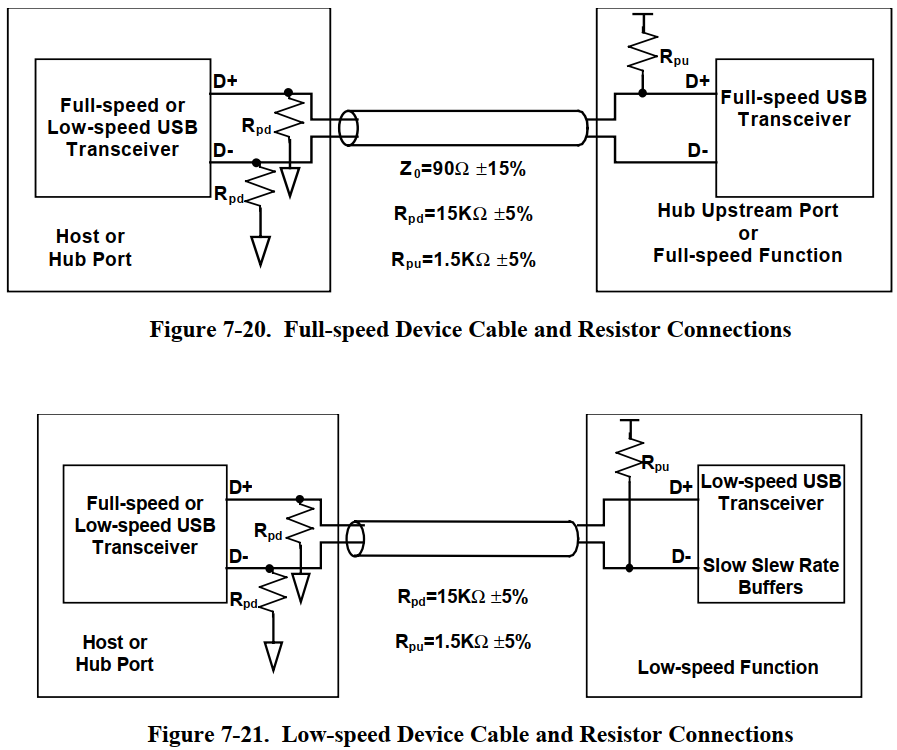

復位 從狀態切換圖上看,一個 USB 設備連接后,它將會被供電,然后被復位。當軟件出錯時,我們也可以發出復位信號重新驅動設備。 那么,USB Hub 端口或 USB 控制器端口如何發出復位信號?發出

2023-07-20 10:05:47 3035

3035

。 2. 外部復位:這種方式是通過外部信號觸發,例如按下復位按鈕,或者給RESET管腳輸入一個低電平信號來觸發復位。 3. 獨立看門狗復位:通過獨立看門狗電路計時到達一定時間而觸發復位。 4. 監控電路復位:當單片機芯片內部幾個重要信號無

2023-10-17 16:44:55 4903

4903 如果FPGA沒有外部時鐘源輸入,可以通過調用STARTUP原語,來使用FPGA芯片內部的時鐘和復位信號,Spartan-6系列內部時鐘源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

2023-10-27 11:26:56 3484

3484

電子發燒友網站提供《數混合信號器件的一般接地原則.pdf》資料免費下載

2023-11-29 10:45:30 1

1 HT7044A 的復位原理,包括其工作原理、電路結構和操作方式。 HT7044A 的復位原理基于外部復位引腳(RESET)和內部復位邏輯電路。當 RESET 引腳接收到外部復位信號時,復位邏輯電路會檢測到這個信號,并執行相應的復位操作,使系統中的各個模塊和寄

2024-01-04 11:24:41 3069

3069 電源監測芯片復位電路:這是最常見的復位電路類型,使用專用的電源監測芯片來監測電源電壓,并在電壓低于或高于預設閾值時觸發復位信號。

2024-01-16 16:04:14 2262

2262 復位方式具有精確控制的特點,因為復位信號與時鐘信號同步工作,所以可以保證復位信號與時鐘信號的相位精確匹配。同步復位的優勢主要有以下幾點: 1. 精確控制:同步復位可以確保復位信號和時鐘信號的相位一致,避免由于信號

2024-01-16 16:25:52 2718

2718 復位信號存在亞穩態,有危險嗎? 復位信號在電子設備中起著重要的作用,它用于使設備回到初始狀態,以確保設備的正常運行。然而,我們有時會發現復位信號存在亞穩態,這意味著信號在一定時間內未能完全復位,并

2024-01-16 16:25:56 1170

1170 或者外部信號等。 復位電路負責生成使單片機進入復位狀態的信號。對于大多數單片機而言,它們的復位(Reset)引腳響應于邏輯低電平信號,這意味著當復位電路提供低電平信號時,單片機便會啟動復位程序。如果復位電路不輸出低

2024-02-16 10:14:00 2778

2778

在信息技術的快速發展中,信號分析與信號處理作為信息科學的重要組成部分,扮演著至關重要的角色。無論是通信、控制、圖像處理還是生物醫學等領域,信號分析與處理都發揮著不可或缺的作用。因此,深入探討信號分析與信號處理必須遵循的原則,對于提高信號處理的效率與準確性、推動相關領域的進步具有重要意義。

2024-05-17 14:19:43 2222

2222 在電子工程領域,復位信號是確保系統穩定、可靠運行的關鍵因素之一。復位信號通常用于在系統出現故障或異常時,將系統恢復到初始狀態,以便重新開始工作。因此,準確測量和分析復位信號對于電子系統的設計和調試

2024-05-17 17:14:19 3400

3400 復位信號,確保單片機在上電后能夠立即進入初始化狀態。其中上拉電阻可以確保在未按下按鈕時輸入引腳上具有高電平狀態,避免輸入信號的浮動和噪音干擾。在選擇上拉電阻時,根據具體需求和電路設計合理參數可以提高電路穩定性、

2024-10-19 14:56:45 1390

1390

前言 最近看advanced fpga 以及fpga設計實戰演練中有講到復位電路的設計,才知道復位電路有這么多的門道,而不是簡單的外界信號輸入系統復位。 流程: 1.同步復位: 優點:⑴大多數DFF

2024-11-15 11:13:55 911

911

在 FPGA 設計中,復位起到的是同步信號的作用,能夠將所有的存儲元件設置成已知狀態。在數字電路設計中,設計人員一般把全局復位作為一個外部引腳來實現,在加電的時候初始化設計。全局復位引腳與任何

2024-11-16 10:18:13 1804

1804

電子發燒友App

電子發燒友App

評論