復(fù)位概述

復(fù)位作為電子系統(tǒng)中最常見的信號(hào)同時(shí)也是最重要的信號(hào),它對(duì)工程師整體的設(shè)計(jì)表現(xiàn)有著極大的影響。復(fù)位信號(hào)可能深刻影響設(shè)計(jì)的性能表現(xiàn),功耗,面積等等。對(duì)于一個(gè)優(yōu)秀的系統(tǒng)設(shè)計(jì),很難不把復(fù)位信號(hào)當(dāng)成一個(gè)關(guān)鍵信號(hào)來設(shè)計(jì)。

同步的代碼可能會(huì)綜合出LUTs,Registers,SRLs,Block or LUT memory,DSP48 registers。對(duì)復(fù)位方式的不同選擇以及對(duì)復(fù)位的使用不同會(huì)影響基本元件的選擇。可能會(huì)引入更多或者更少的資源,影響整體設(shè)計(jì)的表現(xiàn),功耗,甚至?xí)?dǎo)致系統(tǒng)運(yùn)行異常。

什么時(shí)候什么地方使用復(fù)位?

對(duì)于很多新入門工程師來講,很少會(huì)評(píng)估是否需要復(fù)位信號(hào),絕大所數(shù)都是使用提供的模板,對(duì)所有的信號(hào)進(jìn)行復(fù)位,盡管可能不是那么必要,如果是這樣會(huì)增加資源,對(duì)復(fù)位時(shí)序也會(huì)產(chǎn)生影響,所以評(píng)估是否需要復(fù)位是很有必要的。

對(duì)賽靈思器件而言,廠家對(duì)FPGA提供了專用的全局復(fù)位(GSR)。這個(gè)信號(hào)在配置結(jié)束會(huì)把所有的時(shí)序元件都設(shè)置為一個(gè)初始的值。如果這個(gè)初始值沒有被指定,大多數(shù)情況下都會(huì)被設(shè)置為0。每個(gè)器件都會(huì)在配置結(jié)束設(shè)置為一個(gè)定值,因此,有些上電時(shí)單一目的復(fù)位必要性不是很大。下面代碼初始化registers和latches的指定初始值。

// Verilog代碼

reg register1 = 1’b0; // specifying regsiter1 to start as a zero

reg register2 = 1’b1; // specifying register2 to start as a one

reg [3:0] register3 = 4’b1011; //specifying INIT value for 4-bit register

-- VHDL代碼

signal reg1 : std_logic := '0'; -- specifying register1 to start as a zero

signal reg2 : std_logic := ‘1’; -- specifying register2 to start as a one

signal reg3 : std_logic_vector(3 downto 0):="1011"; -- specifying INIT value for 4-bit register

所以像之前所訴述,工程師應(yīng)該仔細(xì)考慮和評(píng)估什么時(shí)候,什么地方需要復(fù)位。因?yàn)椴槐匾膹?fù)位可能會(huì)導(dǎo)致諸多的問題。限制復(fù)位的使用可能具備的優(yōu)勢:

-

限制全局復(fù)位網(wǎng)絡(luò)的扇出

-

減少復(fù)位路徑的互聯(lián)

-

簡化復(fù)位路徑的時(shí)序分析

-

提升整體設(shè)計(jì)的性能表現(xiàn),面積,功耗等

功能性的仿真是可以容易區(qū)分復(fù)位是否需要,所以建議去評(píng)估每一個(gè)同步模塊是否需要復(fù)位,盡量減少在未評(píng)估真實(shí)需要復(fù)位的情況下就引入復(fù)位。

同步復(fù)位異步復(fù)位

同步復(fù)位就是復(fù)位信號(hào)在時(shí)鐘觸發(fā)邊沿才有效,簡單講敏感列表中沒有復(fù)位信號(hào),異步復(fù)位在復(fù)位信號(hào)被置位后即有效,簡單說敏感列表中存在復(fù)位信號(hào)。如下面兩段Verilog代碼:

// 同步復(fù)位

module sync_resetFFstyle (

output reg q,

input d, clk, rst_n);

always @(posedge clk)

if (!rst_n)

q <= 1'b0;

else

q <= d;

endmodule

// 異步復(fù)位

module async_resetFFstyle (

output reg q,

input d, clk, rst_n);

always @(posedge clk or negedge rst_n)

if (!rst_n)

q <= 1'b0;

else

q <= d;

endmodule

同步復(fù)位相比較異步復(fù)位有以下的特點(diǎn):

-

同步復(fù)位可以映射更多種類的資源單元

-

全局的異步復(fù)位會(huì)增加設(shè)計(jì)元件的布線復(fù)雜度(每個(gè)register都要連接復(fù)位信號(hào))

-

如果需要提高電路的集成密度或者對(duì)電路進(jìn)行調(diào)優(yōu)布局,同步復(fù)位更加靈活

-

有些資源僅提供提供同步復(fù)位,如DSP48和RAM模塊,如果使用異步復(fù)位,很難在不影響模塊功能的前提下將異步信號(hào)正確施加在這些模塊。(Xilinx)

同步復(fù)位特點(diǎn):

-

電路是百分之百同步化的

-

時(shí)鐘可以充當(dāng)同步復(fù)位信號(hào)的一個(gè)毛刺濾波,但如果毛刺發(fā)生在時(shí)鐘觸發(fā)邊沿,flip-flop仍然可能出現(xiàn)亞穩(wěn)態(tài)。

-

同步復(fù)位可能需要一個(gè)計(jì)數(shù)器來保障復(fù)位信號(hào)的寬度足夠?qū)拋韺?shí)現(xiàn)有效的復(fù)位。

-

因?yàn)橥綇?fù)位需要時(shí)鐘來復(fù)位,有些極少數(shù)的情況下,如某些低功耗設(shè)計(jì),時(shí)鐘可能在復(fù)位前就被無效,那么同步復(fù)位也無效,這里可能只有異步復(fù)位有效。

異步復(fù)位優(yōu)點(diǎn)

只要具有可復(fù)位的觸發(fā)器,那么異步復(fù)位就可以生效

異步復(fù)位不會(huì)在數(shù)據(jù)路徑引入其他邏輯

異步復(fù)位缺點(diǎn)

反斷言階段,即復(fù)位移除階段,復(fù)位信號(hào)沿如果距離時(shí)鐘觸發(fā)沿很近,則可能發(fā)生亞穩(wěn)態(tài),那么復(fù)位狀態(tài)可能會(huì)丟失,也就是常說的符合Recovery Time以及Removal Time(類似Setup Time和Hold Time)

板子的毛刺和噪聲可能引起虛假復(fù)位。

其他的一些缺點(diǎn)已經(jīng)在(同步復(fù)位相比較異步復(fù)位有以下特點(diǎn))上面小節(jié)闡述。

注意:異步復(fù)位都應(yīng)該同步釋放,以處理可能出現(xiàn)的亞穩(wěn)態(tài)和異常情況,如下面所示代碼:

// 異步復(fù)位同步釋放

module sync_reset #

(

// depth of synchronizer

parameter N = 2

)

(

input wire clk,

input wire rst,

output wire out

);

(* srl_style = "register" *)

reg [N-1:0] sync_reg = {N{1'b1}};

assign out = sync_reg[N-1];

always @(posedge clk or posedge rst) begin

if (rst) begin

sync_reg <= {N{1'b1}};

end else begin

sync_reg <= {sync_reg[N-2:0], 1'b0};

end

end

endmodule

// 代碼來自開源項(xiàng)目AlexForencich

如何去除不必要復(fù)位信號(hào)?

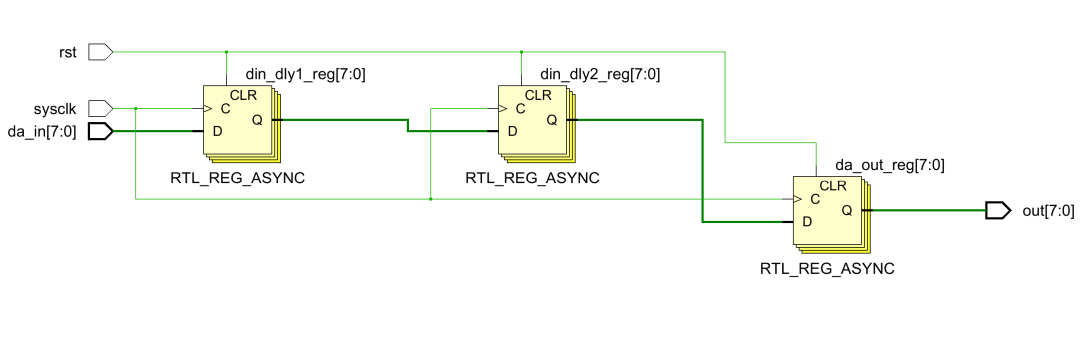

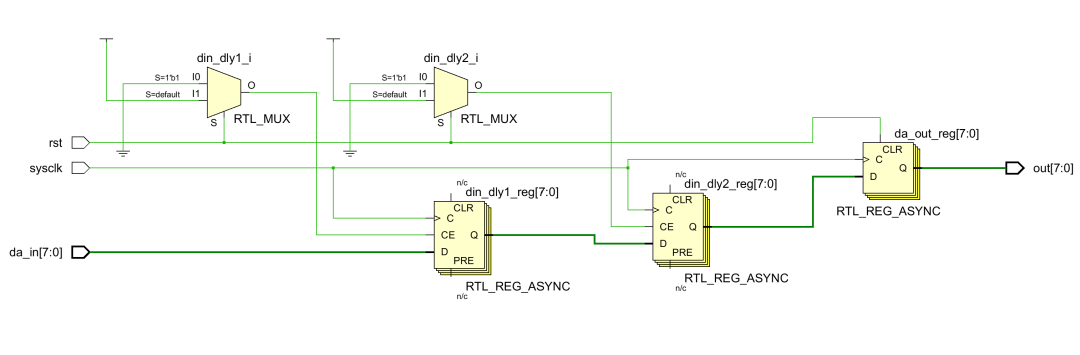

當(dāng)需要去除一些復(fù)位信號(hào)時(shí),直接注釋掉相關(guān)的代碼是不合適并且會(huì)引入非預(yù)期的結(jié)構(gòu)以及會(huì)導(dǎo)致異常問題。如下面的代碼,注釋掉復(fù)位代碼塊里的din_dly1和din_dly2會(huì)讓復(fù)位信號(hào)成為寄存器的使能信號(hào),顯然屬于引入無關(guān)邏輯,可能會(huì)引起設(shè)計(jì)的問題。如圖一為未注釋代碼前綜合出的異步復(fù)位電路,圖二為直接注釋掉復(fù)位區(qū)域信號(hào)的代碼。產(chǎn)生這種問題也很容易理解,代碼邏輯就是非復(fù)位狀態(tài)din_dly1和din_dly2才能工作。

always@(posedge sysclk or posedge rst)

begin

if(rst)

begin

// din_dly1 <= 8'b0;

// din_dly2 <= 8'b0;

da_out <= 8'b0;

end

else

begin

din_dly1 <= da_in;

din_dly2 <= din_dly1;

da_out <= din_dly2;

end

end

圖一:未注釋掉復(fù)位信號(hào)的代碼

圖二:注釋掉復(fù)位信號(hào)的代碼(引入非期望的電路)

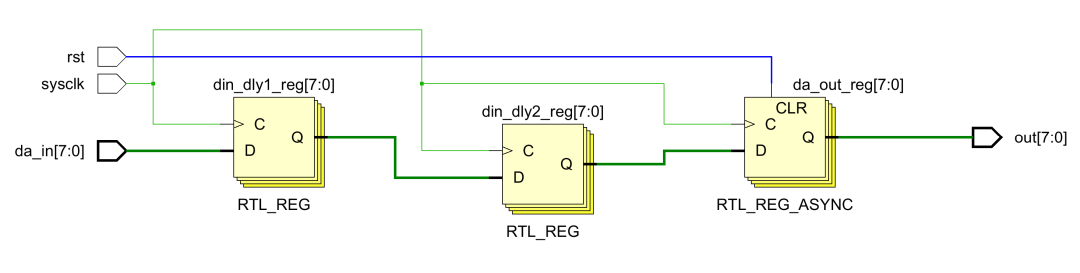

當(dāng)遇到需要去除一些寄存器的復(fù)位信號(hào)時(shí),記住一個(gè)基本原則:一個(gè)時(shí)序模塊不可以混合不同復(fù)位類型的寄存器,簡單講就是不能出現(xiàn)不復(fù)位的寄存器和復(fù)位的寄存器,只要使用復(fù)位信號(hào),那么時(shí)序模塊的寄存器都應(yīng)該復(fù)位。那么需要去除一些寄存器的復(fù)位信號(hào)應(yīng)該怎么辦?同樣功能的代碼如下,將復(fù)位的寄存器放入一個(gè)always塊中,不需要復(fù)位的寄存器放入另一個(gè)always塊中。圖三是實(shí)際綜合出的電路也是實(shí)際期望的電路,沒有引入其他邏輯。

always @(posedge sysclk) begin

din_dly1 <= da_in;

din_dly2 <= din_dly1;

end

always @(posedge sysclk or posedge rst) begin

if(rst)

da_out <= 8'b0;

else

da_out <= din_dly2;

end

圖三:不同復(fù)位類型區(qū)分綜合出的電路

總結(jié):本篇文章主要總結(jié)復(fù)位類型和其優(yōu)缺點(diǎn),在不同的情形下對(duì)復(fù)位類型選擇進(jìn)行權(quán)衡,尤其要評(píng)估一些不需要復(fù)位的情況,以實(shí)現(xiàn)設(shè)計(jì)的更優(yōu)性能表現(xiàn)。具體的內(nèi)容還可以查閱參考文獻(xiàn)所列內(nèi)容。

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1660文章

22411瀏覽量

636271 -

復(fù)位

+關(guān)注

關(guān)注

0文章

179瀏覽量

25045 -

異步復(fù)位

+關(guān)注

關(guān)注

0文章

47瀏覽量

13684

原文標(biāo)題:FPGA復(fù)位信號(hào)設(shè)計(jì)討論

文章出處:【微信號(hào):IP與SoC設(shè)計(jì),微信公眾號(hào):IP與SoC設(shè)計(jì)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

JH7110 什么時(shí)候支持 Vulkan API?

用于穩(wěn)定電源設(shè)計(jì)的復(fù)位IC應(yīng)用實(shí)例

配置了串口DMA,現(xiàn)在是接收可以,發(fā)送不行,是什么地方沒有設(shè)置對(duì)嗎?

超級(jí)法拉電容都用在什么地方

快問快答:什么時(shí)候需要多通道氣密性檢測設(shè)備?選擇幾個(gè)通道合適

法拉超級(jí)電容用在什么地方

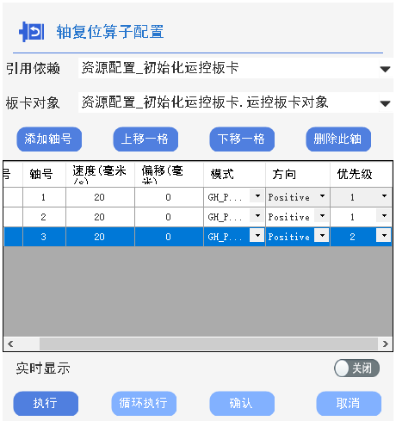

GraniStudio:軸復(fù)位例程

GraniStudio零代碼平臺(tái)軸復(fù)位算子支持多少個(gè)軸同時(shí)復(fù)位,有哪些回零模式?

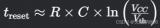

復(fù)位電路的核心功能和主要類型

兩個(gè)關(guān)于PMG1 PoR的問題求解

將DMACB寄存器中的RC位設(shè)置為1來在DMA傳輸結(jié)束時(shí)重新加載計(jì)數(shù)器,什么時(shí)候將需要重新加載的值存儲(chǔ)在FM3中?

為什么adc芯片不寫輸入時(shí)鐘范圍,實(shí)際使用中應(yīng)該怎么給?什么時(shí)候與處理器同源?

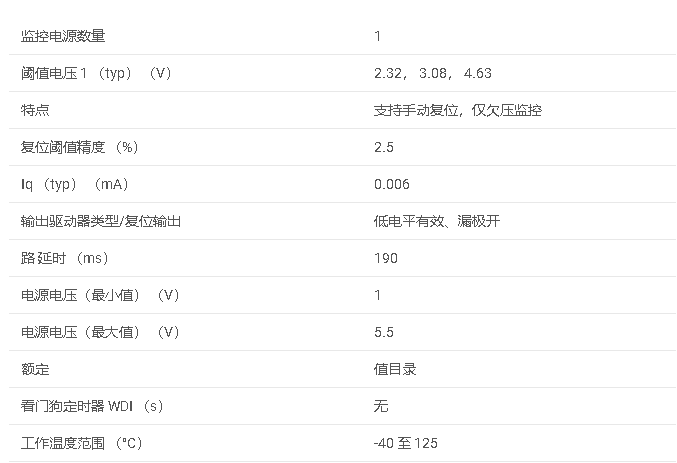

LM3724系列 低功率電壓監(jiān)控和復(fù)位IC,帶手動(dòng)復(fù)位功能數(shù)據(jù)手冊(cè)

復(fù)位電路的作用、控制方式和類型

什么時(shí)候什么地方使用復(fù)位?

什么時(shí)候什么地方使用復(fù)位?

評(píng)論