最近在做一個項目時,我不得不對幾組電子電線進行重新布線,讓它們遠離越野車的發(fā)電機,因為電容耦合產(chǎn)生的噪聲可從發(fā)電機進入電線。這個項目讓我想起了在通過電線、帶狀線纜或板對板連接器布線相互之間相鄰信號時所遇到的類似情況。

2014-09-03 11:53:27 2447

2447

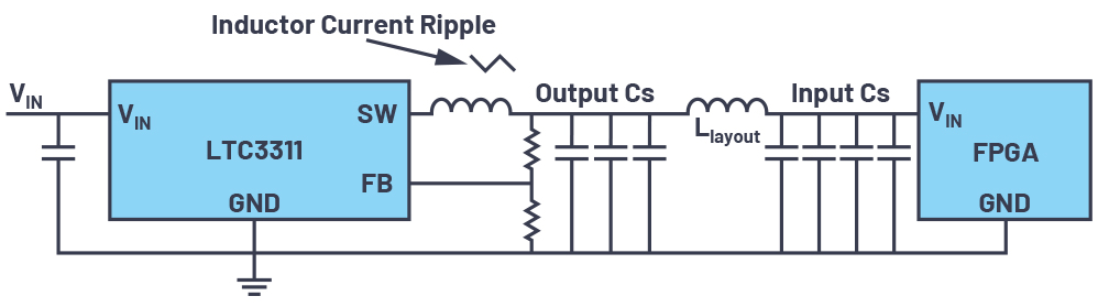

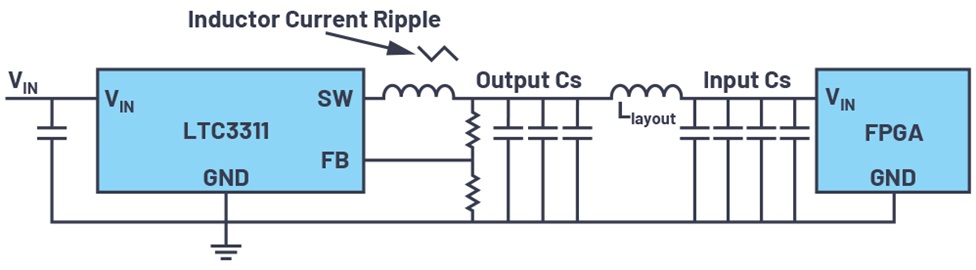

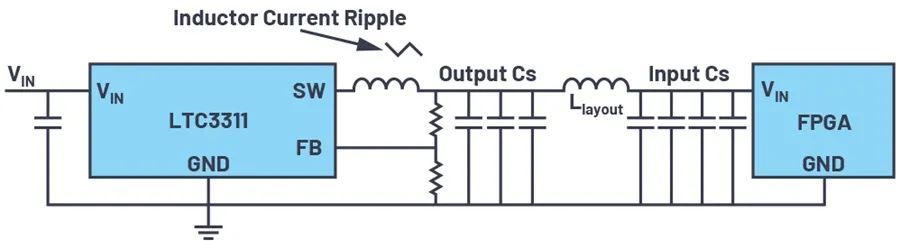

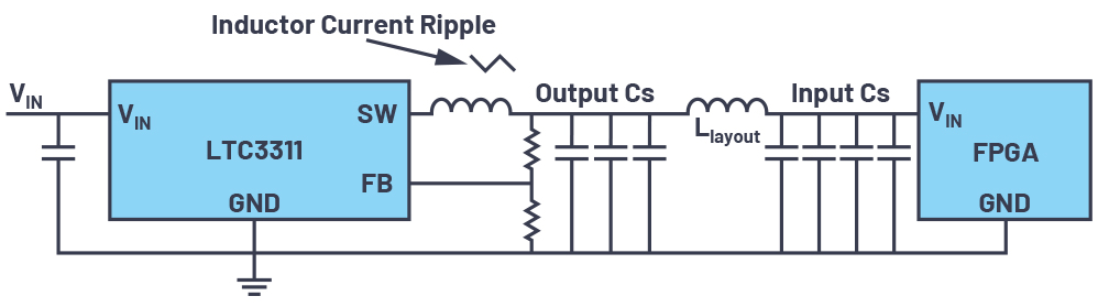

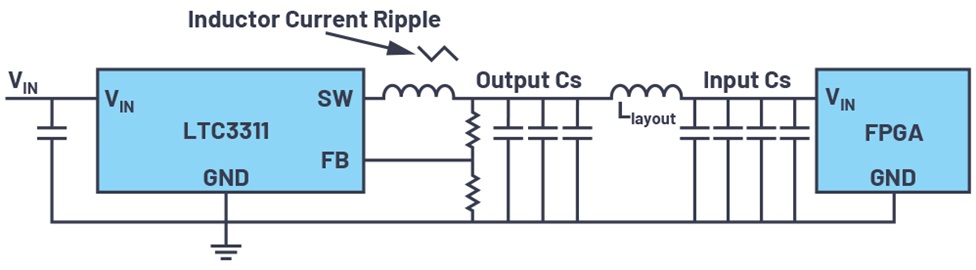

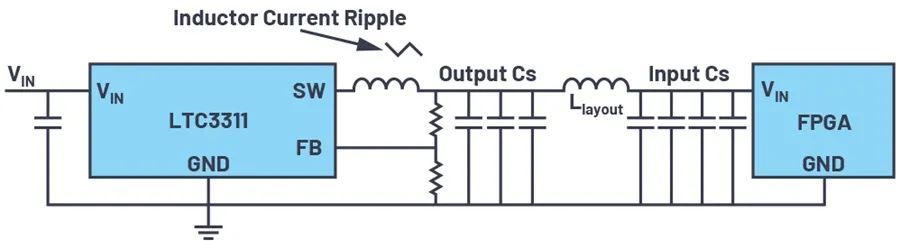

電源輸出電容一般是100 nF至100 μF的陶瓷電容,它們耗費資金,占用空間,而且,在遇到交付瓶頸的時候還會難以獲得。所以,如何最大限度減小輸出電容的數(shù)量和尺寸,這個問題反復被提及。

2022-03-18 11:14:52 3031

3031

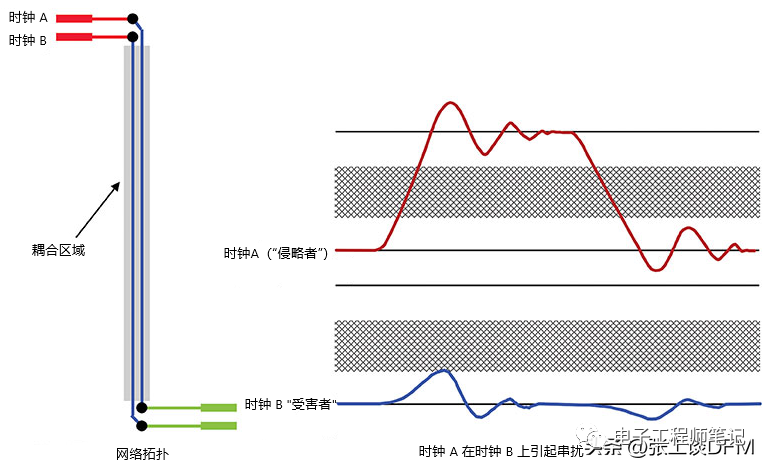

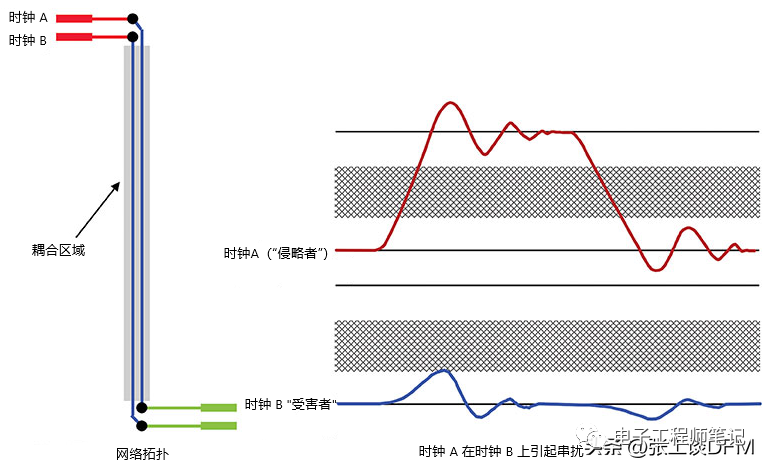

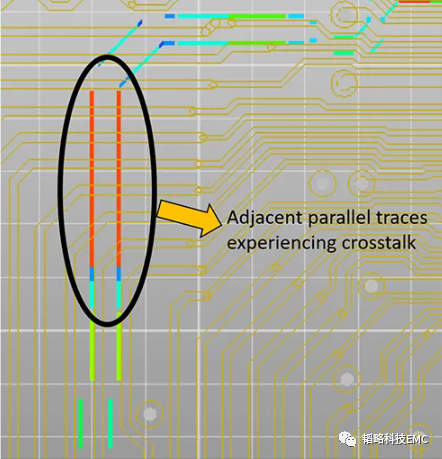

通常以斷斷續(xù)續(xù)或不易重現(xiàn)的方式發(fā)生,對于工程師來說, 盡早解決 PCB 上串擾發(fā)生的所有原因非常重要。 串擾會對時鐘信號、周期和控制信號、數(shù)據(jù)傳輸線和 I/O 產(chǎn)生不良影響。通常來講, 串擾是無法完全消除的,只能盡量減少串擾。 02 . 串擾的機制 ? 1、耦合

2023-05-23 09:25:59 8732

8732

串擾在電子產(chǎn)品的設計中普遍存在,通過以上的分析與仿真,了解了串擾的特性,總結(jié)出以下減少串擾的方法。

2023-06-13 10:41:52 2372

2372

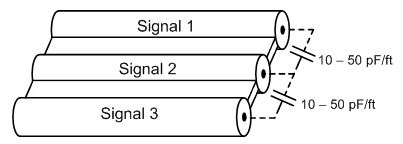

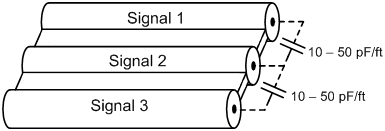

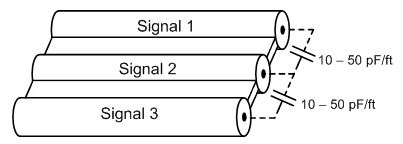

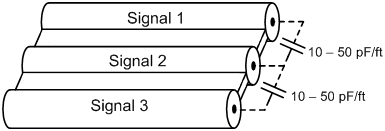

之間產(chǎn)生 10 至 50 pF/ft 的電容,如下圖 1 所示。圖1. 帶狀線纜中相鄰電線間的電容由于信號會相互干擾,兩條信號線之間的電容會引起信號延遲、噪聲耦合或瞬態(tài)電壓。圖 2 是電纜電容在通用雙線

2018-09-19 10:55:31

請問如何最大限度的減小在汽車環(huán)境中的EMI?

2021-04-13 06:57:09

隨著現(xiàn)代微控制器和SoC變得越來越復雜,設計者面臨著最大化能源效率,同時實現(xiàn)更高水平的集成。最大限度地提高能量在低功耗SoC市場中,多個功率域的使用被廣泛采用。在

同時,為了解決更高級別的集成,許多

2023-08-02 06:34:14

DN249-LTC1628-SYNC最大限度地減少多輸出,大電流電源中的輸入電容

2019-06-17 08:42:47

6mil,線間距為12mil,滿足3W原則。圖7為當RT=0.3ns 各個電路的串擾圖形。攻擊線1V的驅(qū)動信號,受害線中微帶線最大近端串擾為11mv,微帶線最大遠端串擾為12mv,帶狀線最大近端串擾為

2014-10-21 09:52:58

在交流耦合輸入的情況下,將 BTL 模式下的輸出失調(diào)電壓指定為高達 150mV。這對PBTL 模式是否同樣適用?如何才能最大限度地減少電壓失調(diào),或者調(diào)節(jié)為 0?

2024-11-08 08:02:19

DN186- 優(yōu)化的DC / DC轉(zhuǎn)換器環(huán)路補償最大限度地減少了大輸出電容器的數(shù)量

2019-08-06 07:09:13

使用DMM和交換機系統(tǒng)時最大限度地縮短總體測試時間的技術(shù)

2019-08-15 14:35:47

DN247- 雙相高效移動CPU電源,可最大限度地減小尺寸和熱應力

2019-07-29 11:00:26

描述 此項 25W 的設計在反激式拓撲中使用 UCC28740 來最大限度降低空載待機功耗,并使用 UCC24636同步整流控制器來最大限度減少功率 MOSFET 體二極管傳導時間。此設計還使用來

2022-09-23 06:11:58

在數(shù)字無線通信產(chǎn)品測試中最大限度地降低電源瞬態(tài)電壓......

2019-08-19 07:42:24

在設計fpga的pcb時可以減少串擾的方法有哪些呢?求大神指教

2023-04-11 17:27:02

的電容,如下圖 1 所示。圖 1. 帶狀線纜中相鄰電線間的電容由于信號會相互干擾,兩條信號線之間的電容會引起信號延遲、噪聲耦合或瞬態(tài)電壓。圖 2 是電纜電容在通用雙線開漏通信總線中引起大量瞬態(tài)電壓的實例

2022-11-23 07:51:41

電源輸出電容一般是100 nF至100 μF的陶瓷電容,它們耗費資金,占用空間,而且,在遇到交付瓶頸的時候還會難以獲得。所以,如何最大限度減小輸出電容的數(shù)量和尺寸,這個問題反復被提及。輸出電容造成

2022-06-14 10:19:20

電源輸出電容一般是100 nF至100 μF的陶瓷電容,它們耗費資金,占用空間,而且,在遇到交付瓶頸的時候還會難以獲得。所以,如何最大限度減小輸出電容的數(shù)量和尺寸,這個問題反復被提及。 輸出電容造成

2022-03-21 14:42:45

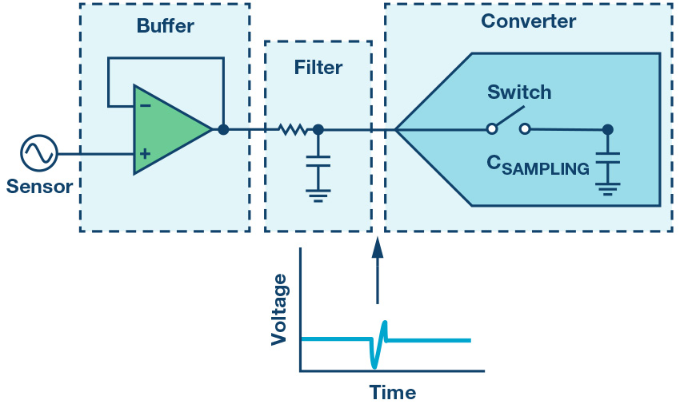

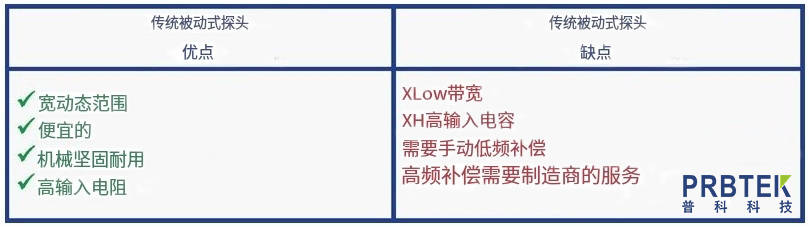

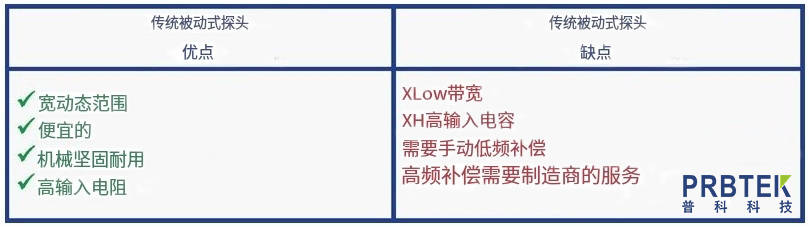

在測量電源噪聲中我們會面臨各種挑戰(zhàn),包括RF干擾和信噪比(SNR),接下來我們來看如何在測量中實現(xiàn)高帶寬,同時最大限度地減少DUT上的電流負載?鑒于DUT是電源軌,我們不希望從它汲取太多電流。但是

2021-12-30 06:19:45

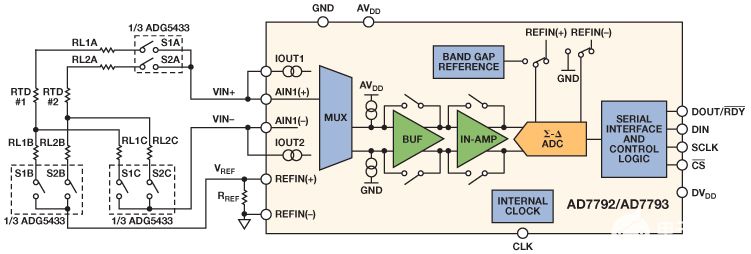

最大限度提高Σ-Δ ADC驅(qū)動器的性能

2021-01-06 07:05:10

如何最大限度的去實現(xiàn)LTE潛力?

2021-05-25 06:12:07

1394物理層所具備的優(yōu)勢是什么?如何采用1394技術(shù)最大限度地優(yōu)化安全攝像頭網(wǎng)絡?

2021-05-25 06:25:20

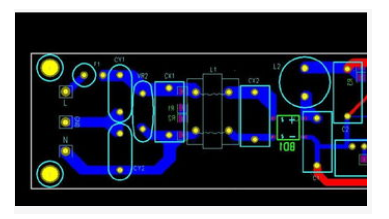

布局電源板以最大限度地降低EMI:第3部分

2019-08-16 06:13:31

布局電源板以最大限度地降低EMI:第1部分

2019-09-05 15:36:07

布局電源板以最大限度地降低EMI:第2部分

2019-09-06 08:49:33

許多高速數(shù)據(jù)采集應用,如激光雷達或光纖測試等,都需要從嘈雜的環(huán)境中采集小的重復信號,因此對于數(shù)據(jù)采集系統(tǒng)的設計來說,最大的挑戰(zhàn)就是如何最大限度地減少噪聲的影響。利用信號平均技術(shù),可以讓您的測量

2019-07-03 07:01:20

在我的應用程序中,HSPDM 觸發(fā) EVADC 同時對兩個通道進行采樣。

我應該如何配置 EVADC 以最大限度地減少采樣抖動并最大限度地提高采樣率?

在用戶手冊中,它提到 SSE=0,USC=0

2024-01-18 07:59:23

外部之間的干擾,不得不說,串擾讓線纜結(jié)構(gòu)越來越復雜。在工程施工中,如何提高串擾呢?首先,在原材料上把好關。要對購買的整箱雙絞線進行驗貨,只有通過驗貨測試,我們才能避免購買不合格的線纜或假線。而在驗貨環(huán)節(jié)

2018-01-19 11:15:04

DN468- 通過精心的IF信號鏈設計最大限度地提高16位,105Msps ADC的性能

2019-09-04 14:09:04

簡單的校準電路最大限度地提高了鋰離子電池管理系統(tǒng)中的準確度

在鋰離子電池系統(tǒng)中,為了實現(xiàn)電池組性能和使用壽命的最大化,使每節(jié)電池的充電狀態(tài)相互匹配是很重

2009-12-20 21:09:29 57

57 最大限度地減少組件的

2009-04-25 11:00:05 1099

1099

最大限度地減少組件的

2009-05-05 11:13:30 591

591

最大限度地減少組件的

2009-05-07 09:13:49 788

788

筆記本最大限度延長電池的使用壽命

本文將討論如何有效地使用電池,以及最大限度地延長電池的使用壽命。本文將只討論最新的XTRA這幾個使用了鋰電池的系列,對于較

2010-04-19 09:20:34 1230

1230 機器監(jiān)測:通過性能測量,最大限度提高生產(chǎn)質(zhì)量。

2016-03-21 16:34:53 0

0 Plunify?基于機器學習技術(shù)的現(xiàn)場可編程門陣列(FPGA)時序收斂和性能優(yōu)化軟件供應商,今天推出了Kabuto?,可最大限度地減少和消除性能錯誤。

2018-07-04 12:24:00 3335

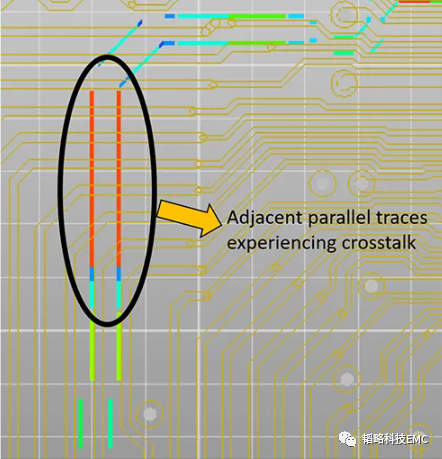

3335 PCB布局上的串擾可能是災難性的。如果不糾正,串擾可能會導致您的成品板完全無法工作,或者可能會受到間歇性問題的困擾。讓我們來看看串擾是什么以及如何減少PCB設計中的串擾。

2019-07-25 11:23:58 3989

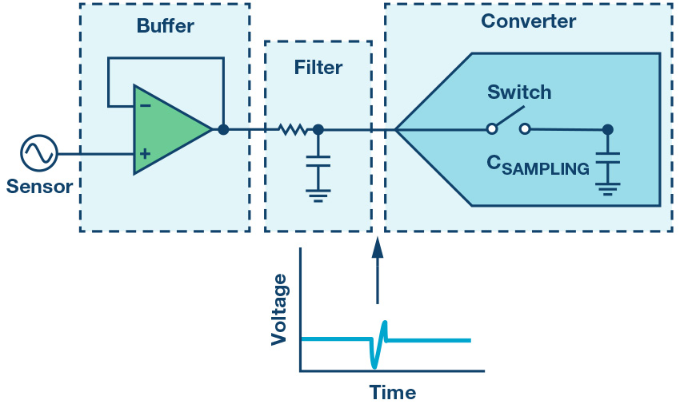

3989 放大器級的設計由兩個彼此相關的不同級組成,因此問題變得難以在數(shù)學上建模,特別是因為有非線性因素與這兩級相關。第一步是選擇用來緩沖傳感器輸出并驅(qū)動ADC輸入的放大器。第二步是設計一個低通濾波器以降低輸入帶寬,從而最大限度地減少帶外噪聲。

2019-07-29 11:29:37 2090

2090

串擾在電子產(chǎn)品的設計中普遍存在,通過以上的分析與仿真,了解了串擾的特性,總結(jié)出以下減少串擾的方法:

2019-08-14 11:50:55 20421

20421 串擾在電路板設計中無可避免,如何減少串擾就變得尤其重要。在前面的一些文章中給大家介紹了很多減少串擾和仿真串擾的方法。

2020-03-07 13:30:00 4390

4390 在新冠肺炎疫情防控期間,要最大限度阻止病毒傳播,關鍵是減少人與人之間的接觸。旨在解決“最后一公里”配送問題的各大電商平臺和無人配送公司紛紛加入戰(zhàn)“疫”,無人配送車、無人機、配送機器人輪番上陣,在疫情

2020-03-13 08:53:07 3768

3768 當電路板上出現(xiàn)串擾時,電路板可能無法正常工作,并且在那里也可能會丟失重要信息。為了避免這種情況, PCB 設計人員的最大利益在于找到消除其設計中潛在串擾的方法。讓我們談談串擾和一些不同的設計技術(shù)

2020-09-19 15:47:46 3330

3330 用于網(wǎng)絡的RF板、高速處理器的板以及許多其他系統(tǒng)對串擾強度有嚴格的要求。信號標準中并不總是規(guī)定最大串擾強度,而且在設計中串擾最強烈的地方也不總是很明顯。盡管您可能會嘗試對設計進行正確的布局規(guī)劃,但

2021-01-13 13:25:55 3420

3420 文章——串擾溯源。 提到串擾,防不勝防,令人煩惱。不考慮串擾,仿真波形似乎一切正常,考慮了串擾,信號質(zhì)量可能就讓人不忍直視了,于是就出現(xiàn)了開頭那驚悚的一幕。下面就來說說串擾是怎么產(chǎn)生的。 所謂串擾,是指有害信號從一

2021-03-29 10:26:08 4155

4155 對于高層建筑物來說,在消防設計中充分考慮建筑物的火災事故隱患,最大限度的減少火災事故造成的人員傷亡和財產(chǎn)損失,是一項及其重要的任務。高層建筑物一旦發(fā)證火災事故,對人員生命威脅最大的是大量的有毒有害

2020-11-09 15:03:24 759

759 義: 攻擊者=高振幅+高頻+短上升時間 受害者=低振幅+高阻抗? 某些信號由于其性質(zhì)或在電路中的功能而對串擾特別敏感,這些信號是潛在的串擾受害者?,如: 模擬信號:與數(shù)字信號相比,它們對噪聲更敏感,尤其是在振幅較低的情況下。 高阻

2020-12-25 15:12:29 3169

3169 理想二極管橋控制器最大限度地減少整流器發(fā)熱量和電壓損失

2021-03-19 09:54:08 3

3 最大限度地減小汽車 DDR 電源中的待機電流

2021-03-20 17:22:52 1

1 DN186優(yōu)化的DC/DC變換器環(huán)路補償最大限度地減少了大輸出電容器的數(shù)量

2021-04-30 09:20:03 3

3 電子發(fā)燒友網(wǎng)站提供《最大限度地提高高壓轉(zhuǎn)換器的功率密度.doc》資料免費下載

2023-12-06 14:39:00 308

308 及電線會在電線之間產(chǎn)生 10 至 50 pF/ft 的電容,如下圖 1 所示。

圖 1. 帶狀線纜中相鄰電線間的電容

由于信號會相互干擾,兩條信號線之間的電容會引起信號延遲、噪聲耦合或瞬態(tài)電壓

2021-11-21 16:30:13 2950

2950

每年消耗 25 萬億千瓦時的電力,其中 53% 是由傳統(tǒng)電動機消耗的。因此,在減少碳足跡的同時最大限度地提高效率是一項強制性任務。

2022-08-04 17:22:02 4318

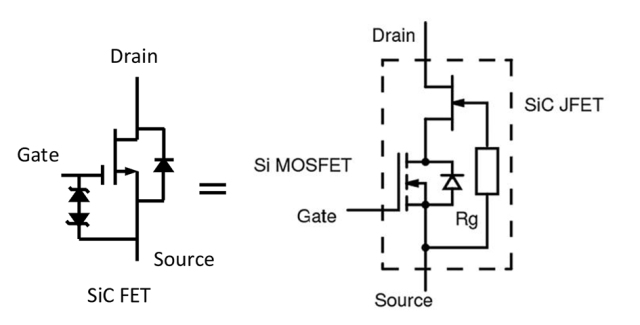

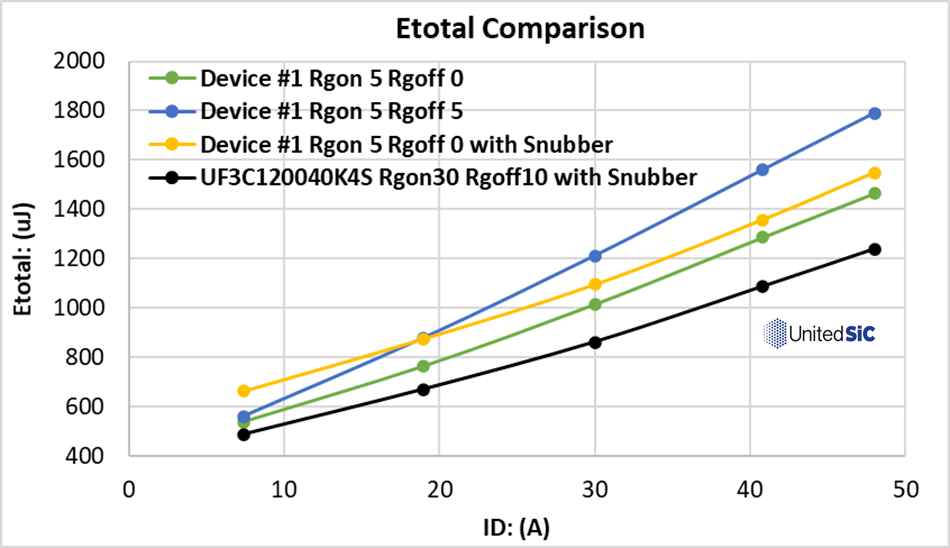

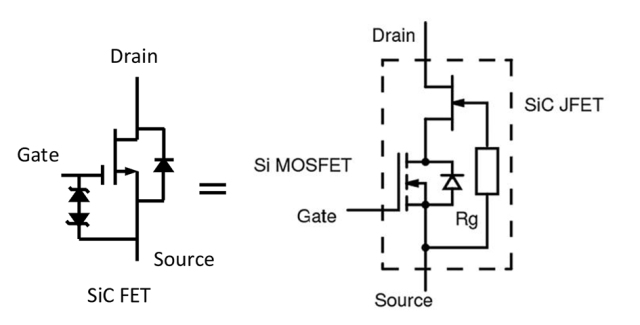

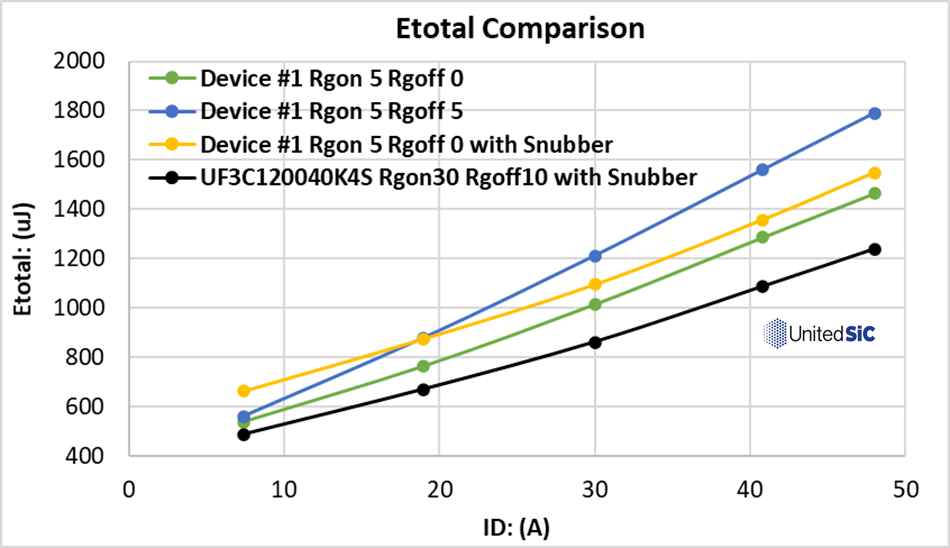

4318 SiC FET 速度極快,邊緣速率為 50 V/ns 或更高,這對于最大限度地減少開關損耗非常有用,但由此產(chǎn)生的 di/dt 可能達到每納秒數(shù)安培。這會通過封裝和電路電感產(chǎn)生高電平的電壓過沖和隨后

2022-08-04 09:30:05 1991

1991

智慧家庭系列文章 | 如何最大限度地減少智能音箱和智能顯示器的輸入功率保護

2022-10-31 08:23:54 0

0 一次性按鈕開關幫助最大限度延長閑置時間

2022-11-04 09:52:06 0

0 時鐘采樣系統(tǒng)最大限度減少抖動

2022-11-04 09:52:12 0

0 如何最大限度減少線纜設計中的串擾

2022-11-07 08:07:26 1

1 在硬件系統(tǒng)設計中,通常我們關注的串擾主要發(fā)生在連接器、芯片封裝和間距比較近的平行走線之間。但在某些設計中,高速差分過孔之間也會產(chǎn)生較大的串擾,本文對高速差分過孔之間的產(chǎn)生串擾的情況提供了實例仿真分析和解決方法。

2022-11-07 11:20:35 2558

2558 AN2014_設計者如何最大限度使用ST單片機

2022-11-21 17:07:41 0

0 如何最大限度地提高電子設備中能量收集的效率

2022-12-30 09:40:14 1926

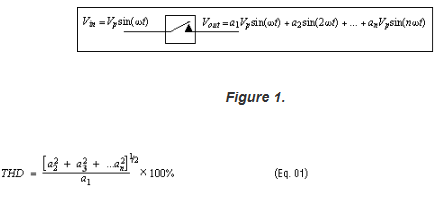

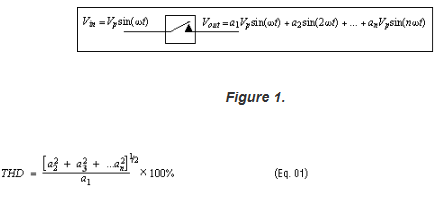

1926 THD規(guī)格在確定通過音頻系統(tǒng)或由音頻系統(tǒng)生成的音頻信號的質(zhì)量或保真度方面起著至關重要的作用。因此,在設計音頻系統(tǒng)時,必須重視選擇合適的元件和電路板布局,以最大限度地降低THD。

2023-01-16 15:55:45 2969

2969

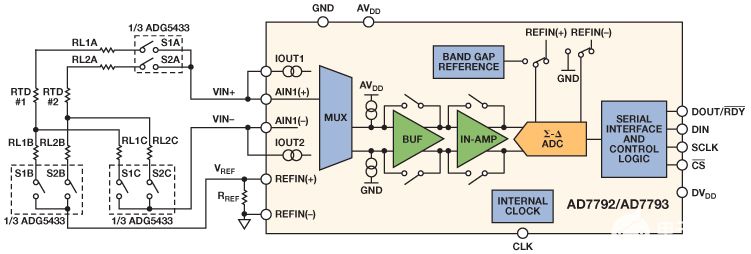

電路和ADC時,將獲得最佳精度,但數(shù)據(jù)采集模塊將很大、價格昂貴且耗電。多路復用可實現(xiàn)更小、成本更低、功耗更低的模塊,但可能會損失一些精度。本文討論如何最大限度地減少多路復用系統(tǒng)中的錯誤。

2023-01-30 14:44:23 2881

2881

使用直角齒輪電機最大限度地減少機器占地面積

2023-03-09 15:16:36 1741

1741

串擾是 PCB 的走線之間產(chǎn)生的不需要的噪聲 (電磁耦合)。

2023-05-22 09:54:24 5606

5606

電子發(fā)燒友網(wǎng)站提供《最大限度地利用太陽能讓您的家保持溫暖.zip》資料免費下載

2023-06-13 15:20:06 0

0 電源輸出電容一般是100 nF至100 μF的陶瓷電容,它們耗費資金,占用空間,而且,在遇到交付瓶頸的時候還會難以獲得。所以,如何最大限度減小輸出電容的數(shù)量和尺寸,這個問題反復被提及。

2023-06-16 10:25:19 1196

1196

開關穩(wěn)壓器,使用戶能夠在短短幾分鐘內(nèi)查看大多數(shù)開關穩(wěn)壓器的波形。 ? 精密的圖形用戶界面 LTspice是一種易于理解的電子電路模擬器,它使用戶不僅可以查看數(shù)值數(shù)據(jù),還可以查看模擬結(jié)果的圖形波形。 通過與LTspice 鏈接最大限度地減少設計重新設計并加速您的仿真 Quadcept允許用戶為

2023-06-26 16:04:18 1873

1873

當信號通過電纜發(fā)送時,它們面臨兩個主要的通信影響因素:EMI和串擾。EMI和串擾嚴重影響信噪比。通過容易產(chǎn)生EMI 和串擾的電纜發(fā)送關鍵數(shù)據(jù)是有風險的。下面,讓我們來看看這兩個問題。

2023-07-06 10:07:03 3408

3408 串擾是 PCB 的走線之間產(chǎn)生的不需要的噪聲(電磁耦合)。

2023-07-20 09:57:08 3937

3937

電子發(fā)燒友網(wǎng)站提供《最大限度地提高數(shù)據(jù)庫效率和性能VMware環(huán)境使用32G NVMe光纖渠道.pdf》資料免費下載

2023-08-07 10:10:18 0

0 空間中耦合的電磁場可以提取為無數(shù)耦合電容和耦合電感的集合,其中由耦合電容產(chǎn)生的串擾信號在受害網(wǎng)絡上可以分成前向串擾和反向串擾Sc,這個兩個信號極性相同;由耦合電感產(chǎn)生的串擾信號也分成前向串擾和反向串擾SL,這兩個信號極性相反。

2023-08-21 14:26:46 700

700 電子發(fā)燒友網(wǎng)站提供《切換以最大限度地利用SAN.pdf》資料免費下載

2023-09-01 11:23:25 0

0 最大限度地減少SIC FETs EMI和轉(zhuǎn)換損失

2023-09-27 15:06:15 1055

1055

一站式PCBA智造廠家今天為大家講講pcb設計布線解決信號串擾的方法有哪些?PCB設計布線解決信號串擾的方法。信號之間由于電磁場的相互而產(chǎn)生的不期望的噪聲電壓信號稱為信號串擾。串擾超出一定的值將可

2023-10-19 09:51:44 2514

2514 電子發(fā)燒友網(wǎng)站提供《最大限度提高∑-? ADC驅(qū)動器的性能.pdf》資料免費下載

2023-11-22 09:19:34 0

0 如何減少PCB板內(nèi)的串擾

2023-11-24 17:13:43 1382

1382

最大限度保持系統(tǒng)低噪聲

2023-11-27 16:58:00 1062

1062

如何最大限度減小電源設計中輸出電容的數(shù)量和尺寸?

2023-12-15 09:47:18 1023

1023

空間中耦合的電磁場可以提取為無數(shù)耦合電容和耦合電感的集合,其中由耦合電容產(chǎn)生的串擾信號在受害網(wǎng)絡上可以分成前向串擾和反向串擾Sc,這個兩個信號極性相同;由耦合電感產(chǎn)生的串擾信號也分成前向串擾和反向串擾SL,這兩個信號極性相反。

2023-12-28 16:14:19 718

718

串擾是PCB(Printed Circuit Board)中走線之間產(chǎn)生的不需要的噪聲(電磁耦合)。串擾會對時鐘信號、周期和控制信號、數(shù)據(jù)傳輸線以及I/O產(chǎn)生不利影響。串擾無法完全消除,但可以通過

2024-01-17 15:02:12 3269

3269

在PCB設計中,如何避免串擾? 在PCB設計中,避免串擾是至關重要的,因為串擾可能導致信號失真、噪聲干擾及功能故障等問題。 一、了解串擾及其原因 在開始討論避免串擾的方法之前,我們首先需要

2024-02-02 15:40:30 2902

2902 探測電路總是會對信號產(chǎn)生一定的影響。探頭負載會改變被探測的信號,可能導致測量問題,甚至可能導致電路執(zhí)行不同的操作。減少電容負載可以幫助最大限度地減少這些影響。在本應用中,您將了解低電容探頭如何改進

2024-03-25 10:51:30 1156

1156

德索工程師說道要減少M9航空接口3芯的串擾,首先需要深入了解串擾產(chǎn)生的原因。串擾通常是由于電磁耦合、電容耦合和互感耦合等效應引起的。在航空電氣系統(tǒng)中,這些效應可能由于接口設計不合理、布線不當、屏蔽措施不到位等因素而加劇。

2024-04-26 16:11:37 942

942

電子發(fā)燒友網(wǎng)站提供《通過優(yōu)化補償最大限度地減少導通時間抖動和紋波.pdf》資料免費下載

2024-08-26 11:34:45 0

0 電子發(fā)燒友網(wǎng)站提供《如何在C2000設備中最大限度地利用GPIO.pdf》資料免費下載

2024-09-19 13:40:04 2

2 電子發(fā)燒友網(wǎng)站提供《利用智能eFuses最大限度地縮短系統(tǒng)停機時間.pdf》資料免費下載

2024-09-25 10:25:04 0

0 電子發(fā)燒友網(wǎng)站提供《最大限度地減少UCC287XX系列的待機消耗.pdf》資料免費下載

2024-09-25 09:35:07 0

0 電子發(fā)燒友網(wǎng)站提供《最大限度地提高GSPS ADC中的SFDR性能:雜散源和Mitigat方法.pdf》資料免費下載

2024-10-10 09:16:46 0

0 電子發(fā)燒友網(wǎng)站提供《最大限度地減少TPS53355和TPS53353系列器件的開關振鈴.pdf》資料免費下載

2024-10-15 11:17:00 0

0 電子發(fā)燒友網(wǎng)站提供《最大限度地提高MSP430? FRAM的寫入速度.pdf》資料免費下載

2024-10-18 10:09:58 1

1 電子發(fā)燒友網(wǎng)站提供《最大限度地減少TRF7964A和TRF7970A省電模式下的電流消耗.pdf》資料免費下載

2024-10-26 10:57:19 0

0 電子發(fā)燒友網(wǎng)站提供《AN101-最大限度地減少線性穩(wěn)壓器輸出中的開關穩(wěn)壓器殘留.pdf》資料免費下載

2025-01-09 14:19:48 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評論