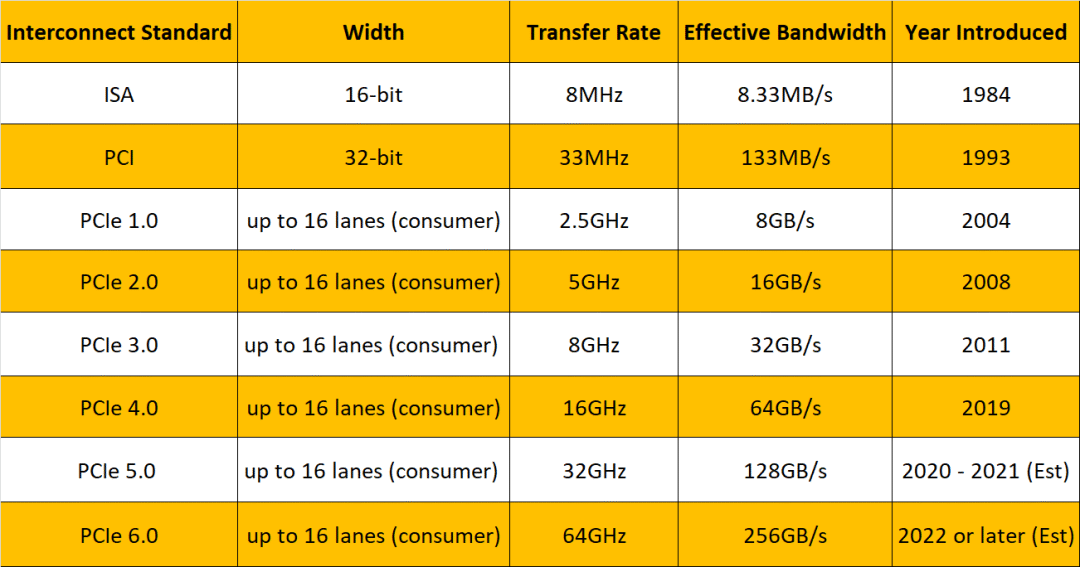

今天這篇文章,我們來聊聊PCIe Bus(PCIe總線)。 Bus在國內(nèi)被理解成汽車,在國內(nèi)還有一種解釋是總線的意思。其實(shí)這兩種翻譯還是有共通之處。以我們生活中例子來說,Bus是兩個城市中溝通的重要連通方式,而總線則是計算機(jī)之間聯(lián)通的重要方式。 我們想從天津去北京辦點(diǎn)事,那么可以乘坐長途大巴,電腦則需要通過PCIe的Bus。簡單來說,Bus總線是多個硬件之間的一條通信公路。 ? 與公路相對應(yīng)的是,PCIe也有不同的規(guī)范,就像高速一樣,不同的道路也有不同的限速,比如國道和高速,寬度和最高行駛速度都不同。這個就對應(yīng)著PCIe1.0、PCIe2.0、PCIe3.0、PCIe4.0這些規(guī)范。 ? 但即使是同一條公務(wù),行駛在不同的線路上也有不同的限速,這個就是跟PCIe1.0不同擴(kuò)展槽的性能類似,例如PCIE x16/x8/x4/x1四種擴(kuò)展方式能夠支持的最大傳輸速度也是不一樣的。 可以說,PCIe總線是計算機(jī)設(shè)備樹的重要組成部分,幾乎所有外圍硬件的擴(kuò)展都需要PCIe上,今天我們就來聊聊PCIe發(fā)展史。 ?

01?挖挖PCIe的祖先們

在多年以前,計算機(jī)主板上不同的設(shè)備所使用的的總線接口是完全不一樣的,硬盤有硬盤對應(yīng)的總線接口,網(wǎng)卡有網(wǎng)卡對應(yīng)的總線接口。 這樣好處是每個設(shè)備都有對應(yīng)的總線接口,優(yōu)化性能簡單。但對于個人來說,隨著擴(kuò)展設(shè)備的逐漸增多,如果都在主板上擴(kuò)展對應(yīng)的總線接口,有點(diǎn)得不償失,同時造成了主板拓展的局限性,也對硬件規(guī)格的統(tǒng)一帶來很多的不便。 為了解決這個瓶頸,IBM和Intel聯(lián)手,在1981年第一代IBM PC XT機(jī)型上采用了第一代ISA插槽,作為現(xiàn)代PC的開山之作,當(dāng)時8位的ISA提供了4.77MB/s的帶寬(或傳輸率)。 ? 由于兼容性好,一經(jīng)推出,ISA總線就受到了各個廠商的歡迎,成為了上個世紀(jì)80年代最廣泛使用的系統(tǒng)總線。但由于ISA使用的是并行總線,當(dāng)時的抗干擾技術(shù)也不成熟,就導(dǎo)致ISA總線的帶寬不能設(shè)計的很高,只能達(dá)到8MB/s的速率。 這個傳輸速度對于在90年代逐漸出現(xiàn)的像圖像這種大數(shù)據(jù)傳輸需求來說還是有點(diǎn)"不夠勁兒"。 除了速度慢這個缺點(diǎn),還有就是ISA總線接口上的設(shè)備不能自動配置,無法即插即用。再加上IBM自作聰明在PS/2產(chǎn)品線上引入了MCA總線,迫使其他幾家PC兼容機(jī)廠商聯(lián)合起來搗鼓出來EISA。這些都導(dǎo)致了ISA總線最終被淘汰。 在1992年,Intel搞出了自己的殺招,提出PCI(Peripheral Component Interconnect)總線協(xié)議,并靠著自己在PC領(lǐng)域的強(qiáng)大影響力,召集了一堆小伙伴組成了名為 PCI-SIG (PCI Special Interest Group)(PCI 特殊興趣組J)的企業(yè)聯(lián)盟。從那以后這個組織就負(fù)責(zé)PCI總監(jiān)的標(biāo)準(zhǔn)制定和推廣。

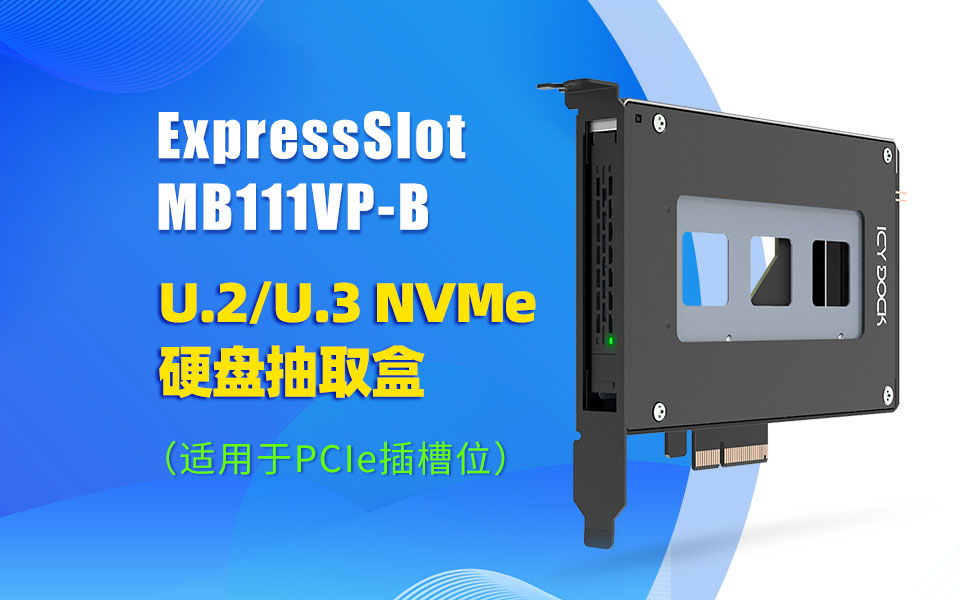

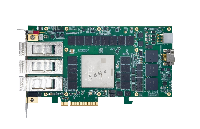

? 不得不點(diǎn)贊下Intel這種先見之明,在90年代就開始建立自己的"朋友圈",相比于封閉的IBM,英特爾合作共贏的心態(tài)讓PCI標(biāo)準(zhǔn)得到了廣泛推廣和使用。統(tǒng)一的標(biāo)準(zhǔn)也有利于外圍設(shè)備制造商的創(chuàng)新,從那以后各種各樣的PCI設(shè)備應(yīng)運(yùn)而生,豐富了PC的整個生態(tài)環(huán)境。 相比ISA總線,PCI總線帶寬升級到了132MB/s,速度提升非常明顯。再就是支持自動配置,即插即用。 但PCI總線也并不是完美的,PCI總線跟ISA總線都是使用了并行總線設(shè)計,所以傳輸速度也受到了影響。再就是PCI總線的帶寬共享機(jī)制,在高負(fù)載下,其他設(shè)備可能會出現(xiàn)搶帶寬的現(xiàn)象,也不支持熱插拔。 于是為了解決PCI總線的缺陷,技術(shù)再一次進(jìn)行了升級革新,2004年,Intel再一次帶領(lǐng)小伙伴革了PCI的命也就是本篇文章要說的PCI Express(簡稱PCIe)總線了。如今計算機(jī)已經(jīng)開始是第五代(gen5,5.0),而且在計算機(jī)中更是更為了不可或缺的存在。 ? 如今,PCIe可以支持的設(shè)備非常多,常見的有顯卡、固態(tài)硬盤(PCIe接口形式)、無線網(wǎng)卡、有線網(wǎng)卡、聲卡、視頻采集卡、PCIe轉(zhuǎn)接M.2接口、PCIe轉(zhuǎn)接USB接口、PCIe轉(zhuǎn)接Tpye-C接口等。

02?PCIe的傳輸速度和寬度

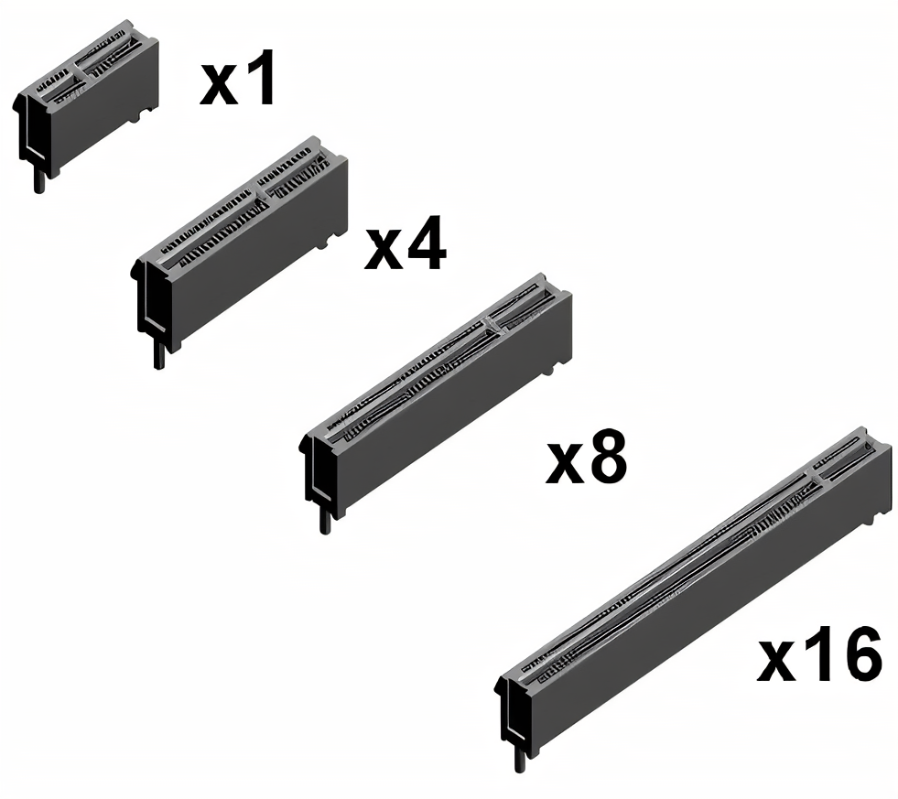

PCIe總線有兩種存在形式,一種是接口、一種是通道。當(dāng)PCIe以接口形式存在的時候,就是主板上橫著的長槽。有人可能會問,這長槽有啥作用,為啥我的主板上的長槽長短不一呢?

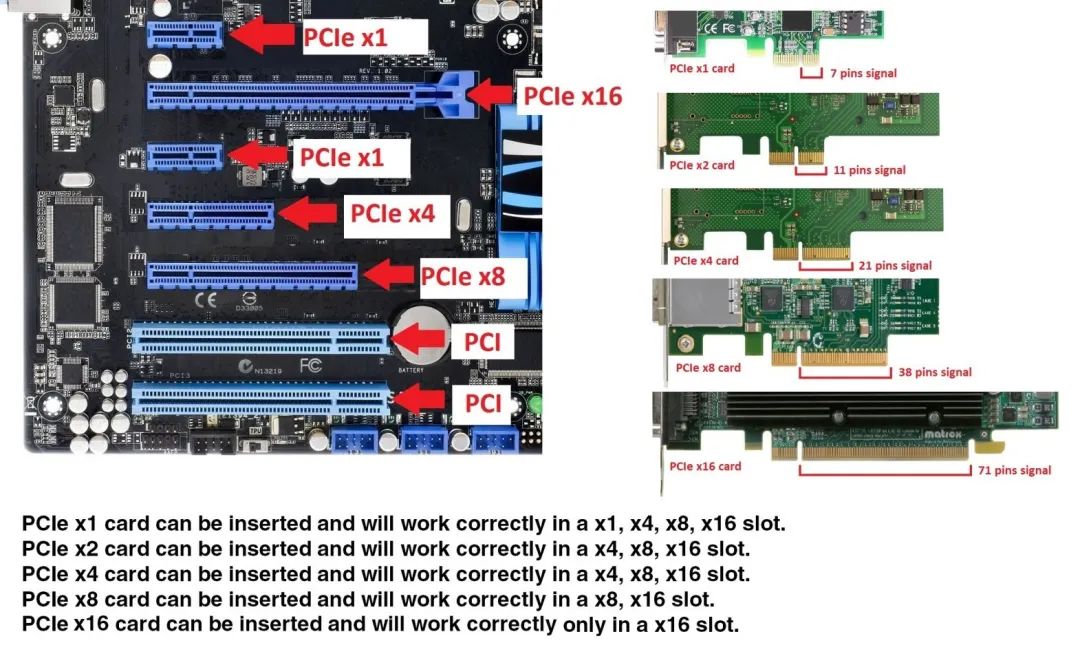

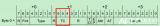

這些長槽其實(shí)是PCIe不同的接口,常見的PCIe接口主要有四種尺寸,X1、X4、X8、X16,一般情況下四種尺寸的插槽最大帶寬是不同的。它們的速度是不一樣的,X16的PCIe速度就是X8的兩倍,X8就是X4的兩倍。當(dāng)然,上面這段話都是建立在同一代PCIe總線之上的。

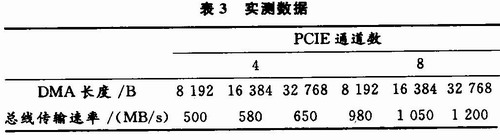

那么PCIe的吞吐量是怎么算出來的呢?首先我們來看下不同PCIe接口尺寸的計算公式:吞吐量=傳輸速率*編碼方案*物理信道Lane 以PCIe4.0x4為例,該系列為4.0版本的PCIe,包含4個物理信道Lane,每個通道的吞吐量為: 16GT/s x 128b/130b =1.969GB/s 所以PCIe4.0x4的吞吐量為:1.969GB/s x 4 = 7.877GB/s,如果是PCIe4.0x16,吞吐量最大就是64GB/s。

除了吞吐量不同,不同的PCIe的尺寸的應(yīng)用有啥不同呢?我們就來詳細(xì)看下X1、X4、X8、X16的應(yīng)用情況。

PCIe x16插槽:如上圖所示,PCIe x16插槽全長89mm,有164根針腳,靠主板外側(cè)端有一卡口,將16x分為前后兩組,較短的插槽有22根針腳,這個是用于供電,每個尺寸的插槽都有這個22根針腳的供電設(shè)計。較長的插槽142根,主要用于數(shù)據(jù)傳輸,具有16通道所帶來的高帶寬。 目前來看,PCIe x16插槽,主要用于GPU顯卡以及RAID陣列卡等,這個插槽擁有優(yōu)良的兼容性,可以向下兼容x1/x4/x8級別的設(shè)備,而且具有更強(qiáng)的傳輸性能,可以說是PCIE x16插槽是PCIE的萬能插槽。 由于PCIe x16插槽常用于顯卡,與CPU處理器直接相通,在物理位置上直接靠近CPU,這樣顯卡與處理器之間的數(shù)據(jù)交換就可以減少延遲,讓系統(tǒng)的性能可以得到充分的發(fā)揮。 PCIe x8插槽:全長56mm,有98根針腳,與PCIe x16比較,主要是數(shù)據(jù)針腳減少至76根,短的供電針腳仍然是22針腳。 為了兼容性,PCIe x8插槽通常加工成PCIE x16插槽的形式,但數(shù)據(jù)針腳只有一半是有效的,也就是說實(shí)際帶寬只有真正的PCIE x16插槽的一半。可以觀察主板布線,x8的后半段沒有線路連接,甚至針腳也沒有焊接。 實(shí)際上除了旗艦級或服務(wù)器的主板,能提供多條真正的PCIex16插槽外,大多數(shù)的主板,只會提供一條真正的PCIe x16插槽,就是最靠近CPU的那條。而第二條和第三條PCIe x16插槽,則多數(shù)是PCIe x8甚至是x4級別的。

PCIe x4插槽:長度為39mm,同樣是在PCIE x16插槽的基礎(chǔ)上,以減少數(shù)據(jù)針腳的方式實(shí)現(xiàn),主要用于PCIe SSD固態(tài)硬盤,或者是通過PCIE轉(zhuǎn)接卡安裝的M.2 SSD固態(tài)硬盤。 PCIe x4插槽通常由主板芯片擴(kuò)展而來,不過隨著cpu內(nèi)部PCIE通道數(shù)的增多,現(xiàn)在有部分高端主板可以開始提供直連cpu的PCIE x4插槽,用于安裝PCIE SSD固態(tài)硬盤。 不過與PCIe x8插槽一樣,PCIe x4插槽為了兼容性,現(xiàn)在多數(shù)也是做成PCIe x16插槽的形式,或是擴(kuò)展為M.2接口,用于安裝M.2 SSD、M.2無線網(wǎng)卡或者其它M.2接口設(shè)備,其余擴(kuò)展卡則留給PCIE x1插槽負(fù)責(zé)。 PCIE x1插槽:長度僅有25mm,相比PCIE x16插槽,其數(shù)據(jù)針腳是大幅度減少至14個。PCIE x1插槽的帶寬通常由主板芯片提供,主要用途是獨(dú)立網(wǎng)卡、獨(dú)立聲卡、USB 3.0/3.1擴(kuò)展卡等都會用到PCIE x1插槽,甚至可以通過轉(zhuǎn)接線給PCIE x1插槽裝上顯卡,用來挖礦或者實(shí)現(xiàn)多屏輸出。 X1的另外一個重要作用就是是用來替代原來的PCI設(shè)備的。 ?

03?PCIe未來會怎樣?

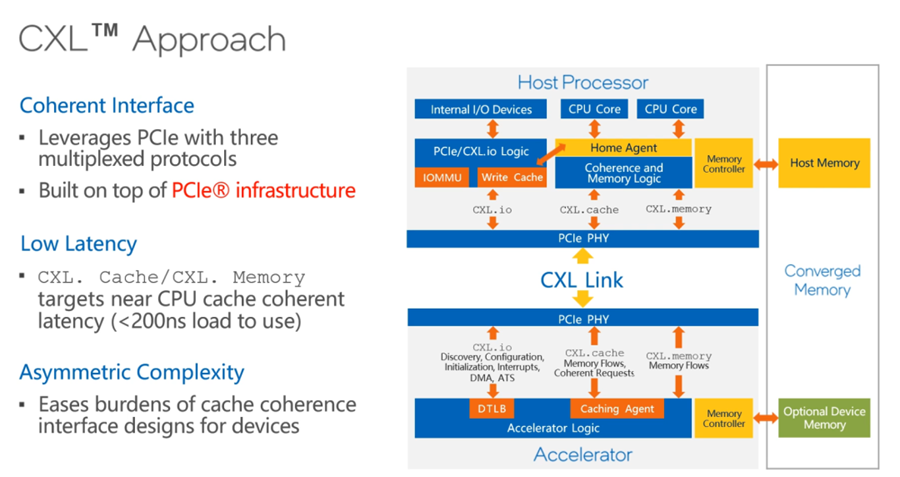

PCIe接口從2001年發(fā)展至今,在協(xié)議的完整性上已經(jīng)建立足夠高的"護(hù)城河",重新定義一個接口協(xié)議在性能上超越PCIe,短期內(nèi)一方面沒有企業(yè)會有這個動力,另一方面技術(shù)的維度,也沒有可預(yù)期的雛形創(chuàng)新。 但"成"也Intel ,"阻礙"也在Intel。 我們都知道,Intel在CPU發(fā)展方面一直以"擠牙膏"著稱,其實(shí)在PCIe方面,Intel擠牙膏那是更嚴(yán)重。 一般來說,規(guī)范確定到商品化需要1~2年的時間,就像摩爾定律估算的差不多,每過1~2年,其實(shí)產(chǎn)品就需要升級進(jìn)化。 但是靠著英特爾靠著自己的壟斷優(yōu)勢,在PCIe升級方面則是亦步亦趨。從2004年發(fā)布PCIe1.0以后,到2023年新一代服務(wù)器的發(fā)布,PCIe5.0才開始逐漸出現(xiàn)在主板上。 而且可以說,PCIe 5.0是PCIe發(fā)展的重要分水嶺,這是因為人算不如天算,Intel沒想到大數(shù)據(jù)AI、視覺渲染、基因分析以及EDR仿真等需求的突然爆發(fā),讓PCIe的數(shù)據(jù)傳輸已經(jīng)趕不上GPU的需求。 ? 為了解決PCIe在數(shù)據(jù)傳輸?shù)南拗疲缭趲啄昵埃袌錾蠋追N不同的傳輸和內(nèi)存語義協(xié)議逐漸出現(xiàn)--IBM的OpenCAPI內(nèi)存接口協(xié)議、Xilinx的CCIX協(xié)議、NVIDIA的NVLink協(xié)議、惠普企業(yè)版的Gen-Z協(xié)議,都是為了解決PCIe4.0傳輸過慢的問題。 眼看著大家都在革PCIe的"命",在2019年3月份Intel推出了CXL(Compute Express Link)協(xié)議接口,將CXL協(xié)議封裝到PCIE鏈路層數(shù)據(jù)包中傳送,并在CPU端的PCIE總控后端按照事務(wù)標(biāo)識分流CXL專屬事務(wù)給CXL處理邏輯處理。 Intel希望能夠讓CPU與GPU、FPGA或其他加速器之間實(shí)現(xiàn)高速高效的互聯(lián),從而滿足高性能異構(gòu)計算的要求。最值得注意的是CXL標(biāo)準(zhǔn)的接口規(guī)格與PCIe 5.0是兼容的,從而讓CXL協(xié)議讓PCIe5.0上可以運(yùn)行,進(jìn)一步鞏固PCIe在計算機(jī)里的影響力。

Intel的策略是,既然CPU等需求趨勢已經(jīng)來襲,堵不如疏,不如把GPU、DPU等用作一把刀,來與NVIDIA形成某種制衡,如今,NVIDIA也加入了CXL聯(lián)盟,對Intel來說,反正我建了通往內(nèi)存的"高速路",你GPU怎么走都得聽我的。 ? 通過這種方式,也能進(jìn)一步制衡GPU的發(fā)展,一顆CPU想支持幾個GPU,還得通過Intel說了算。 值得注意的是,第四代英特爾至強(qiáng)可擴(kuò)展處理器每一顆處理器支持最多4個CXL設(shè)備,支持CXL Type1和CXL Type2。)這些將提升服務(wù)器的綜合能力,為內(nèi)存密集型和IO密集型場景提供更高價值。

04?最后

2022年1月,PCI-SIG 組織今日正式發(fā)布了 PCIe 6.0 標(biāo)準(zhǔn)。作為CXL 3.0軟件棧協(xié)議規(guī)范的物理連接承載平臺,PCIe 6.0主要用于CPU與GPU(AI加速器)、CPU與DPU(智能萬卡NIC)、以及CXL內(nèi)存模塊(可以理解為其他CPU DDR內(nèi)存)的連接,對應(yīng)的應(yīng)用場景,如大內(nèi)存、以及不同外設(shè)緩存之間的直接數(shù)據(jù)交換。 對于這些場景而言,PCIe 6.0接口子系統(tǒng)高達(dá)64GT/s的數(shù)據(jù)傳輸速率,對于異構(gòu)計算架構(gòu)的影響意義重大。

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論