PCIe是一種高速串行計算機(jī)擴(kuò)展總線標(biāo)準(zhǔn),自2003年推出以來,已經(jīng)成為服務(wù)器(Server)和PC上的重要接口。今天為大家簡單介紹一下PCIe的發(fā)展歷史以及它的工作原理。

一、PCIe的由來

PCIe接口的全稱是Peripheral Component Interconnect Express,原來的名字是“3GIO”,由Intel在2001年提出。PCIe的前身是PCI,PCI 使用的是并行傳輸方式,有較多的限制,并使用數(shù)據(jù)包(Packet)進(jìn)行數(shù)據(jù)傳輸,數(shù)據(jù)報文在發(fā)送和接收過程中需要經(jīng)過事務(wù)層、數(shù)據(jù)鏈路層和物理層多個層次。

PCIe串行總線標(biāo)準(zhǔn)被推出時,旨在替代舊的PCI、PCI-X和AGP總線標(biāo)準(zhǔn),以實(shí)現(xiàn)更高的數(shù)據(jù)速率并簡化系統(tǒng)設(shè)計。在交由PCI-SIG(PCI特殊興趣組織)認(rèn)證發(fā)布后改名為“PCI-Express”,簡稱“PCI-e”。此后,隨著時間的推移PCIe不斷改進(jìn)以適應(yīng)現(xiàn)代計算機(jī)的最新帶寬需求。

圖1

2021年,PCIe 6.0 規(guī)范發(fā)布。每通道數(shù)據(jù)傳輸速率從PCIe 5.0的32 GT/s翻番至64 GT/s,PCIe 6.0*16通道的帶寬高達(dá)256 GB/s,除了帶寬和效率的提升外,PCIe 6.0還具有更低的延遲,是PCIe技術(shù)的又一大飛躍。

二、PCIe鏈路的常見設(shè)備

PCIe采用的是樹型拓?fù)浣Y(jié)構(gòu), 一般由根復(fù)合體(Root Complex),中繼器(Repeater),終端設(shè)備(Endpoint)等類型的PCIe設(shè)備組成。

接下來將講述PCIe如何通過下圖突出顯示的典型鏈路進(jìn)行初始化和傳輸。

圖2

Root Complex:根復(fù)合體是CPU和PCIe總線連接的接口。主要負(fù)責(zé)存儲器域到PCIe總線域的地址轉(zhuǎn)換,隨著虛擬化技術(shù)的引入,根復(fù)合體的功能也越來越復(fù)雜。根復(fù)合體把來自CPU的request轉(zhuǎn)化成PCIe的4類request(configuration、memory、I/O、message)并發(fā)送給下面的設(shè)備。

Repeater:中繼器是一種信號調(diào)節(jié)裝置,可分為兩類:Retimers和Redriver,兩者都是常用的PCIe組件,Retimer通過內(nèi)部時鐘重構(gòu)信號,再恢復(fù)后發(fā)送出去;Redriver則是通過信號均衡化和預(yù)加強(qiáng)等技術(shù),重新加強(qiáng)再發(fā)送出去。在圖示中,我們將使用PCIe 4.0兼容的Retimers舉例。

PCIe Endponit: PCIe終端設(shè)備,是PCIe樹型結(jié)構(gòu)的末端節(jié)點(diǎn)。比如SSD,網(wǎng)卡、GFX卡等等。

圖3

三、PCIe鏈路初始化

在了解PCIe鏈路是如何建立以及數(shù)據(jù)如何通過PCIe協(xié)議傳輸之前,我們先了解一下常見PCIe控制信號的功能。

圖4

PERST#信號為全局復(fù)位信號,由處理器系統(tǒng)提供。處理器系統(tǒng)需要為PCIe插槽和PCIe設(shè)備提供該復(fù)位信號。PCIe設(shè)備使用該信號復(fù)位內(nèi)部邏輯,當(dāng)該信號有效時,PCIe設(shè)備將進(jìn)行復(fù)位操作。

WAKE#和CLKREQ#信號都用于在本文討論范圍之外的低功率狀態(tài)之間轉(zhuǎn)換。

REFCLK#是PCIe設(shè)備開始數(shù)據(jù)傳輸?shù)南葲Q條件,PCIe設(shè)備通過使用REFCLK#提供的100 MHz外部參考時鐘(Refclk),用于協(xié)調(diào)在兩個PCIe設(shè)備間的數(shù)據(jù)傳輸。

PCIe鏈路在初始狀態(tài)時,需要檢測對端設(shè)備是否存在,然后才能進(jìn)行鏈路訓(xùn)練。所有PCIe設(shè)備通電并提供參考時鐘信號后在每個通道上將擁有接收器檢測(Receiver Detection)電路,該電路將允許PCIe設(shè)備確定是否有要配對的鏈路伙伴。假設(shè)PCIe Rx檢測電路檢測到另一個設(shè)備,則每個通道將開始以2.5 GT/s的速度進(jìn)行傳輸串行數(shù)據(jù)。

圖5

2.5 GT/s是PCIe 1.0采用的數(shù)據(jù)速率,另外由于PCIe 1.0與任何PCIe設(shè)備兼容,因此每個PCIe鏈路都以相同的鏈路初始化過程開始。以下圖為例,Root Complex、Retimer和Endpoint都以PCIe 1.0的速度開始傳輸。

圖6

在經(jīng)過PCIe鏈路初始化后,每個器件開始接收數(shù)據(jù)并做出響應(yīng)。PCIe連接開始鏈路訓(xùn)練過程并進(jìn)入配置階段,在該階段中,由于通道長度變化而導(dǎo)致數(shù)據(jù)中的任何偏差都能得到校準(zhǔn),PCIe鏈路的寬度、鏈路速率、鏈路翻轉(zhuǎn)和鏈路極性也在此階段確定。

圖7

當(dāng)存在多條鏈路時,則PCIe連接稱為PCIe分叉。在示例中,有一個非分叉連接,即所有通道都分配給編號為0的鏈路。由于Retimer鏈路分為兩部分,其兩側(cè)的鏈路分別進(jìn)行鏈路初始化。在確定鏈路和通道號后,PCIe鏈路可以進(jìn)入多種狀態(tài)。

圖8

以進(jìn)入L0狀態(tài)舉例,這是發(fā)送和接收數(shù)據(jù)與數(shù)據(jù)包的正常操作狀態(tài)。到達(dá)L0后Root Complex和Endpoint可相互通信,PCIe鏈路也可轉(zhuǎn)換為多種低功耗狀態(tài)或另一種鏈路訓(xùn)練狀態(tài)。在此不做過多闡述。

圖9

四、PCIe鏈路均衡

當(dāng)PCIe設(shè)備支持PCIe Gen2時,鏈路速度也會隨之提高。如果數(shù)據(jù)速率為PCIe Gen3或以上,PCIe鏈路將需要經(jīng)歷額外鏈路優(yōu)化過程(稱為鏈路均衡)。

鏈路均衡以建立設(shè)備間穩(wěn)定的連接為目的。通過調(diào)節(jié)Tx (傳輸端)和Rx (接收端)的設(shè)置,提高信號質(zhì)量,使PCIe鏈路以最穩(wěn)定且更快的速率傳輸。由于PCIe在Gen3及以上的每一代均需優(yōu)化連接,因此鏈路均衡過程可能發(fā)生多次。

例如:若所有PCIe設(shè)備為Gen5,則有3次鏈路均衡過程(第1次:Gen1-Gen3;第2次:Gen3-Gen4;第3次:Gen4-Gen5)。鏈路均衡通過PCIe 規(guī)范中定義的preset值來實(shí)現(xiàn),preset指不同的預(yù)過沖(Preshoot)和去加重(De-emphasis)的組合。對于Gen3和Gen4,有11個preset值,即preset0-preset10。對于不同的鏈路情況,系統(tǒng)要求Rx端發(fā)送Tx EQ preset設(shè)置請求給Tx端,讓其做對應(yīng)的preset均衡設(shè)置;Tx端發(fā)送Rx EQ均衡設(shè)置,要求Rx端做相應(yīng)的設(shè)置,最終獲得一個最優(yōu)的均衡組合和Rx端的眼圖。

圖10

Phase0:第1階段鏈路均衡涉及上游端口(Upstream port)和下游端口(Downstream port)之間的精確動態(tài)協(xié)商,下游端口通過向上游設(shè)備發(fā)送每個通道所需的發(fā)送器preset值來開始鏈路均衡,被稱為第0階段鏈接均衡。在接收到下游端口的請求后不久,上游端口增加到第3代(Gen3)鏈路數(shù)據(jù)速率,并開始使用所需preset將訓(xùn)練序列發(fā)送回下游端口。鏈路速度增加至Gen3(8 GT/s)后,鏈路均衡過程通過來回發(fā)送preset值來協(xié)商每個端口的preset配置,從而繼續(xù)優(yōu)化鏈路。

圖11

Phase1:為了充分優(yōu)化鏈路,以便能夠交換訓(xùn)練序列(Training Sequences)并且完成用于精調(diào)目的的剩余鏈路均衡階段,盡管有出現(xiàn)鏈路質(zhì)量差的可能性,相同的訓(xùn)練序列依然會被重復(fù)發(fā)送,來確保下游端口接收到正確的preset值。

圖12

Phase2:在第1階段鏈路的誤碼率實(shí)現(xiàn)BER≤10e-4后,進(jìn)入到Phase 2,隨后進(jìn)一步優(yōu)化上游端口的preset值,直至獲得最優(yōu)設(shè)置,鏈路的誤碼率應(yīng)滿足BER ≤ 1E-12。

Phase3:到第3階段對下游端口執(zhí)行相同的協(xié)商。上游端口通過訓(xùn)練序列發(fā)送均衡請求去調(diào)整下游端口的preset值,直至獲得最優(yōu)設(shè)置,鏈路的誤碼率應(yīng)滿足BER ≤ 1e-12。

當(dāng)Phase3完成后,鏈路均衡也已完成,此時鏈路以Gen3的速率進(jìn)入L0狀態(tài),并在該速率進(jìn)行穩(wěn)定通信。對于更高的傳輸速率,PCIe設(shè)備必須進(jìn)行多次鏈路均衡過程。

圖13

然而在某些主板設(shè)計中,尤其是那些具有長通道鏈路的主板,這種信號質(zhì)量無法實(shí)現(xiàn),可能需要另外的信號調(diào)節(jié)。在這種情況下,中繼器(如Redriver,Retimer)則被用來做信號調(diào)節(jié),并在PCIe設(shè)備和根復(fù)合體之間提供高質(zhì)量信號。

Union Memory

長按識別關(guān)注更多憶聯(lián)資訊

原文標(biāo)題:什么是PCIe?

文章出處:【微信公眾號:UnionMemory憶聯(lián)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

存儲

+關(guān)注

關(guān)注

13文章

4842瀏覽量

90184 -

SSD

+關(guān)注

關(guān)注

21文章

3135瀏覽量

122361

原文標(biāo)題:什么是PCIe?

文章出處:【微信號:UnionMemory憶聯(lián),微信公眾號:UnionMemory憶聯(lián)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

【PCIE732】光纖卡,具備PCIe接口的萬兆光纖卡

JH7110 中的 PCIE 器件有什么用途?

總線授時卡優(yōu)勢解讀 #雙模pcie授時卡 #北斗pcie授時卡 #pcie授時板卡 #總線 #同步天下

探索TS2PCIE412:高性能PCIe開關(guān)的技術(shù)剖析

PCIe 8.0規(guī)范開發(fā)更新!

PCIe 6.0 SSD主控芯片狂飆!PCIe 7.0規(guī)范到來!

嵌入式接口通識知識之PCIe接口

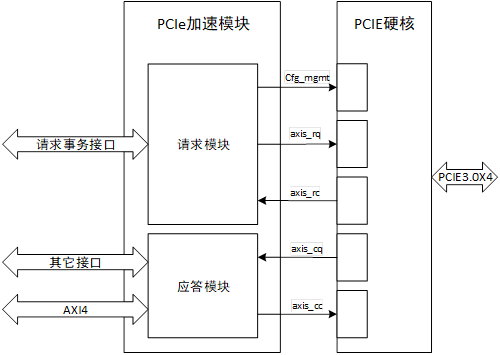

NVMe高速傳輸之?dāng)[脫XDMA設(shè)計17:PCIe加速模塊設(shè)計

PCIe協(xié)議分析儀能測試哪些設(shè)備?

什么是PCIe?

什么是PCIe?

評論