IIC(Inter-Integrated Circuit)是一個多主從的串行總線,又叫I2C,是由飛利浦公司發明的通訊總線,屬于半雙工同步傳輸類型總線。IIC總線是非常常見的數據總線,僅僅

2022-11-10 16:07:09 3169

3169

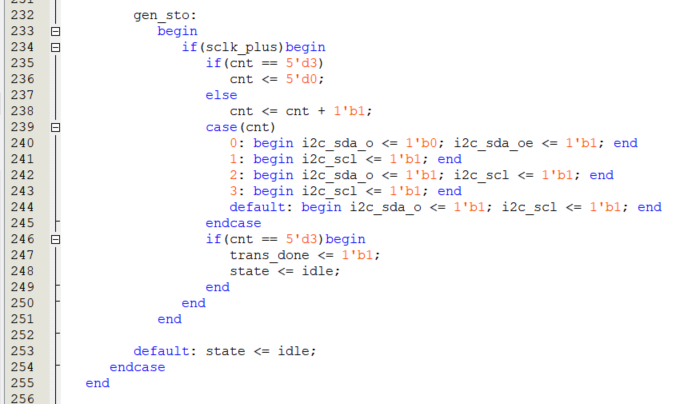

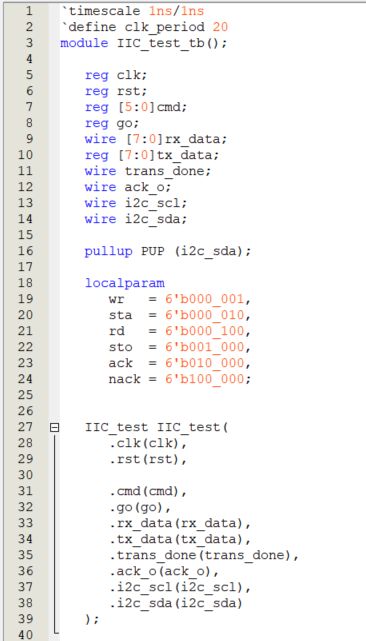

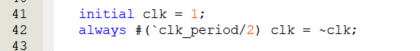

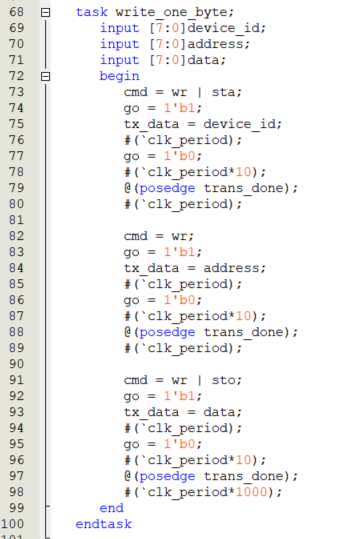

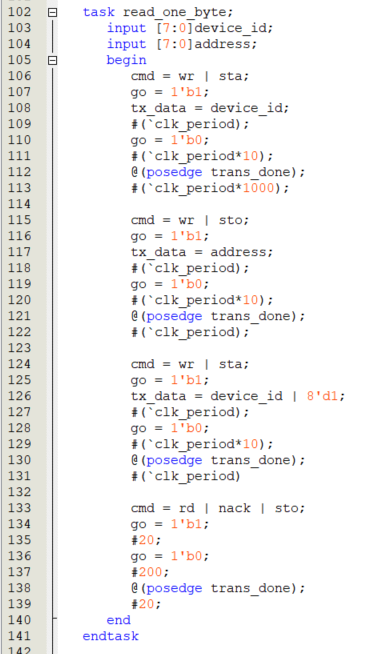

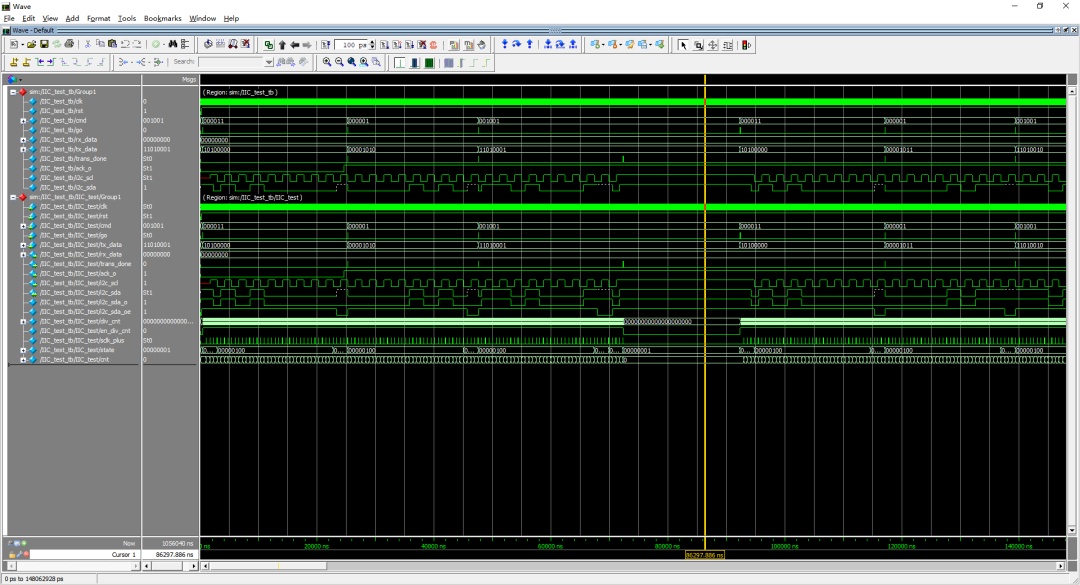

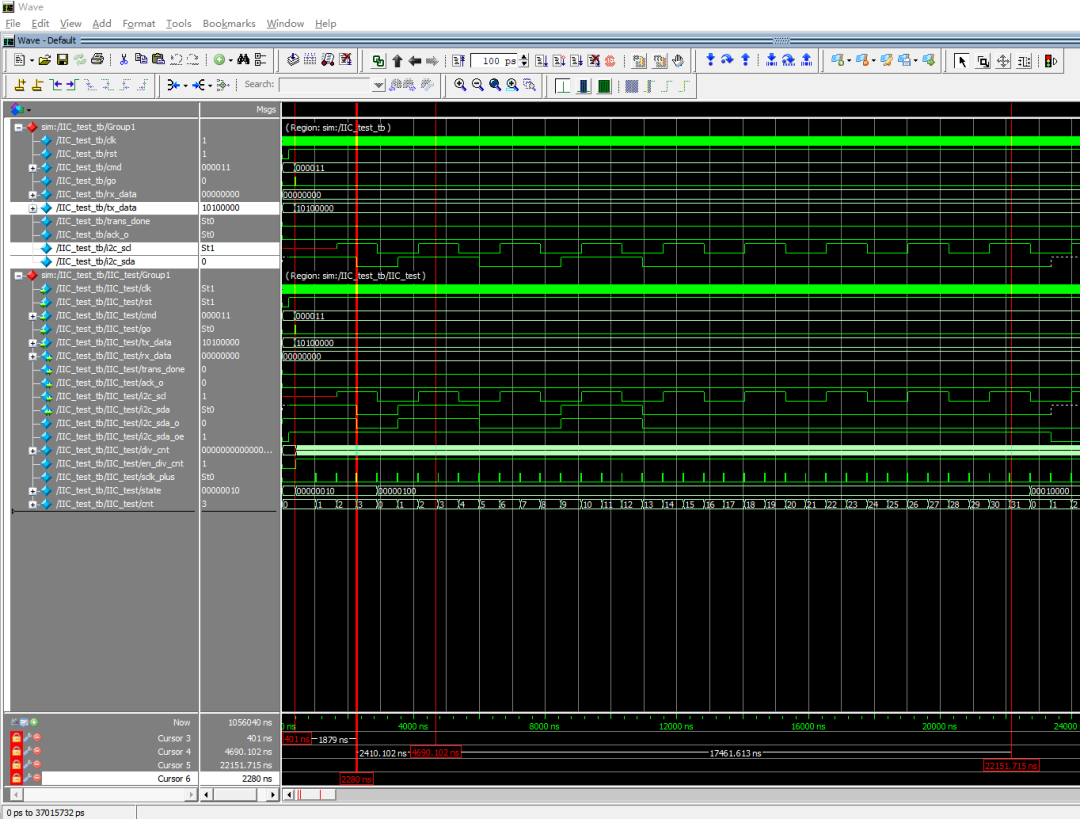

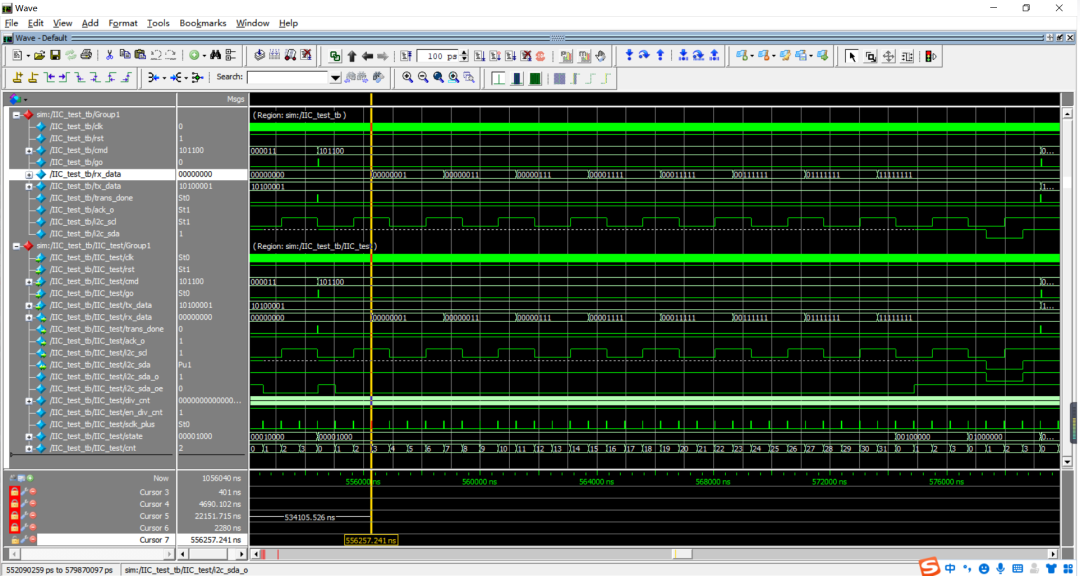

IIC總線的FPGA實現原理及過程 IIC總線概述 IIC開發于1982年,當時是為了給電視機內的CPU和外圍芯片提供更簡易的互連方式。電視機是早的嵌入式系統之一,而初的嵌入系統是使用內存映射

2023-05-15 02:35:01 3261

3261

IIC(Inter-Integrated Circuit)集成電路總線,它是一種兩線式串行通信總線,又叫I2C,使用多主從架構,由飛利浦公司在1980年推出的。多用于主控制器和從器件間的主從通信,在

2023-06-07 15:38:18 11611

11611

IIC(Inter-Integrated Circuit)是一個多主從的串行總線,又叫I2C,是由飛利浦公司發明的通訊總線,屬于半雙工同步傳輸類型總線。

2023-09-12 11:15:38 4064

4064

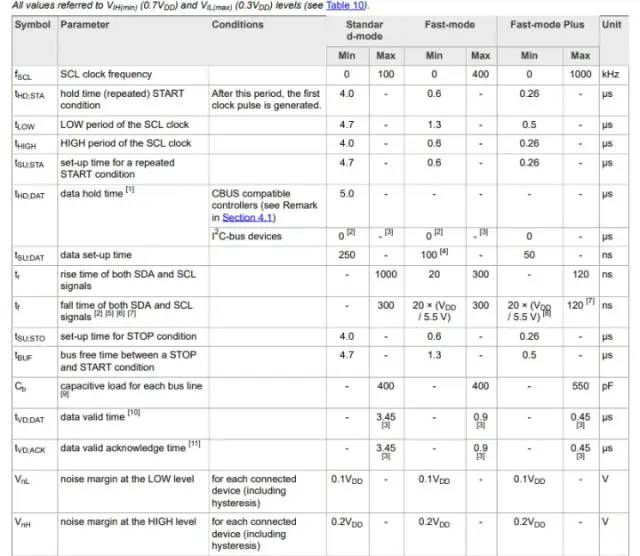

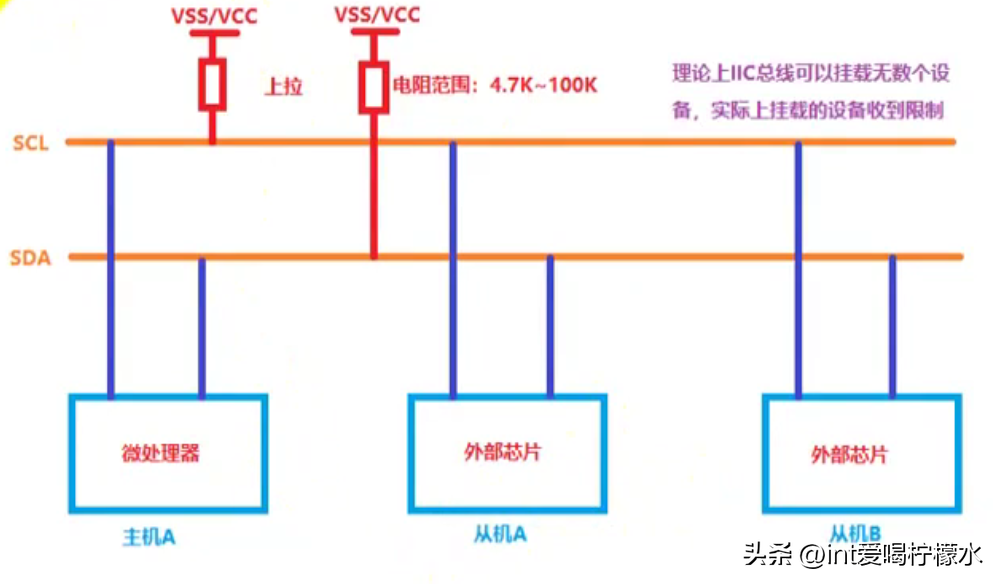

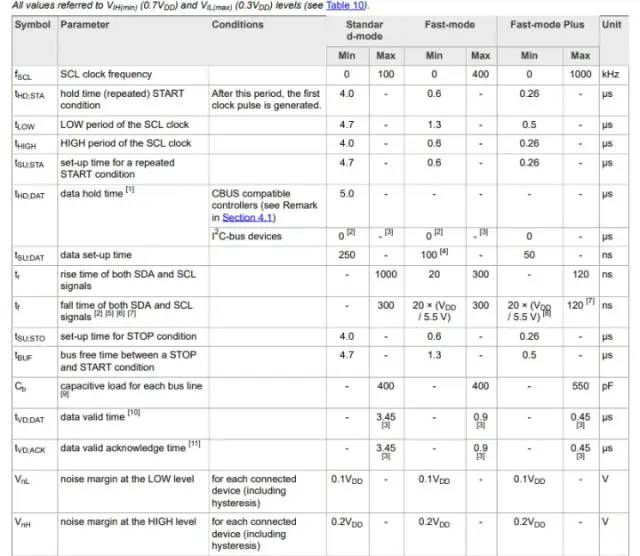

IIC是飛利浦提出的一種通信總線結構,其硬件架構比較簡單,僅包含SCL和SDA兩條線。根據最新的IIC總線標準,IIC總線包含Standard-mode(100kbit/s)、Fast-mode

2023-09-20 15:18:58 3458

3458

通信協議非常適合近距離低速芯片間通信。Philips(for IIC)和Motorola(for SPI) 出于不同背景和市場需求制定了這兩種標準通信協議。

2023-09-26 09:30:07 3659

3659

DE2_TV中,有關于寄存器的配置的部分,采用的方法是通過IIC的功能,這里對IIC總線的FPGA實現做個說明。

2024-01-05 10:16:05 1804

1804

IIC(Inter-Integrated Circuit)總線是一種半雙工的串行通信接口。在I2C總線上,主設備和從設備之間的數據傳輸是采用半雙工模式進行的。這意味著主設備和從設備在不同的時間段內交替發送和接收數據。

2024-02-02 16:37:21 6815

6815

IIC協議簡介I2C 通訊協議(Inter-Integrated Circuit)是由Phiilps公司開發的,由于它引腳少,硬件實現簡單,可擴展性強,不需要USART、CAN等通訊協議的外部收發

2021-08-20 06:12:52

STM32 IIC實驗講解,從入門到放棄。文章目錄STM32 IIC實驗講解,從入門到放棄。前言一、IICIIC是什么?IIC協議二、代碼部分IIC底層代碼分析總結前言本文參考了網上的博文,并加以

2022-01-17 08:12:41

1.IIC總線介紹第一:I2C(IIC,Inter-Integrated Circuit),兩線式串行總線,由PHILIPS公司開發用于連接微控制器及其外圍設備。第二:IIC是半雙工通信方式,只有2

2021-08-18 06:03:30

IIC總線協議

2016-10-25 14:24:25

先簡單介紹一下IIC總線協議。IIC總線是philips公司推出的新一代串行通信標準總線。它僅靠兩根線實現全雙工通信:SDA(數據線),SCL(時鐘線)。 寫時序如下

2016-08-07 12:43:01

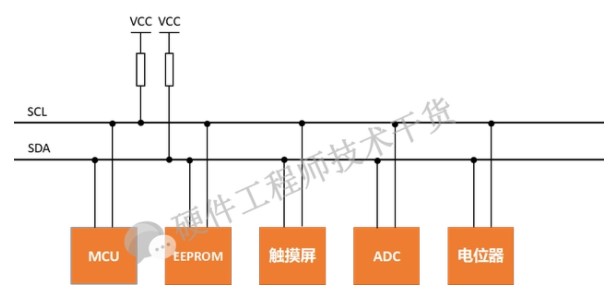

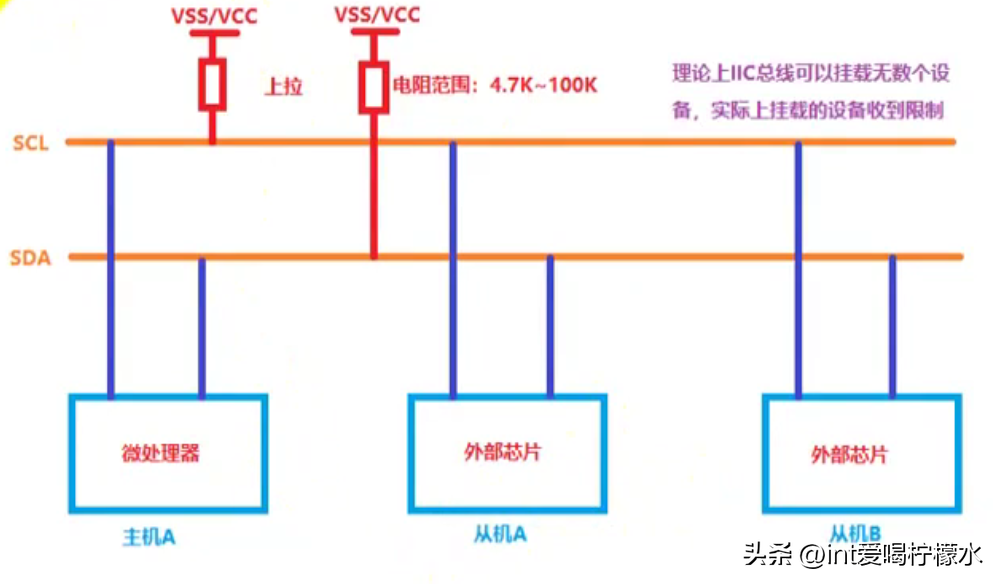

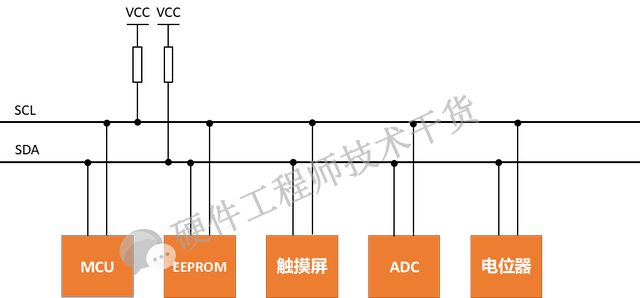

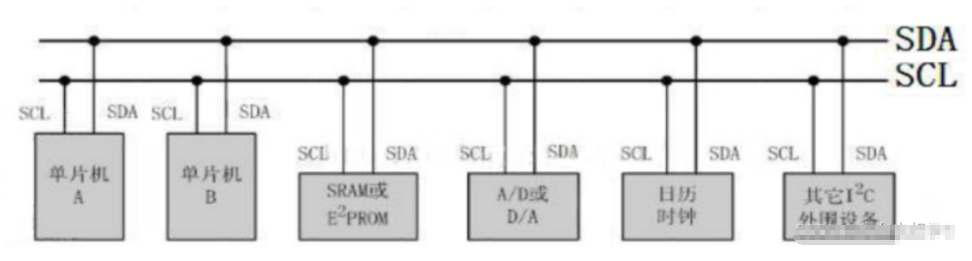

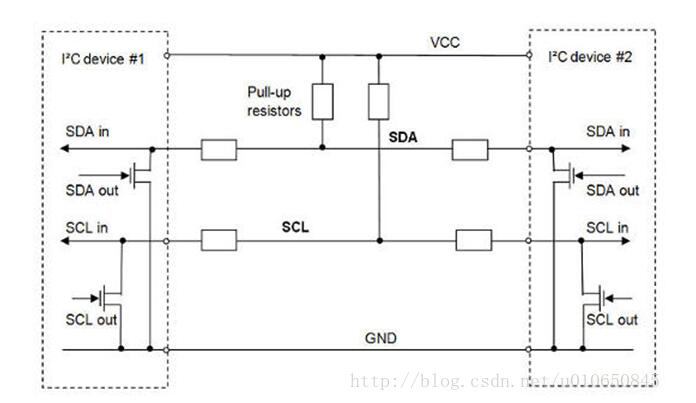

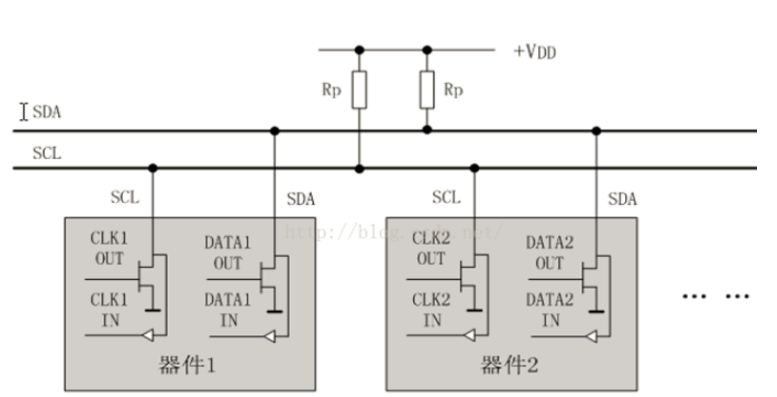

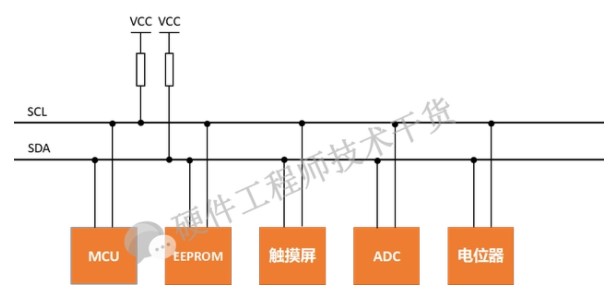

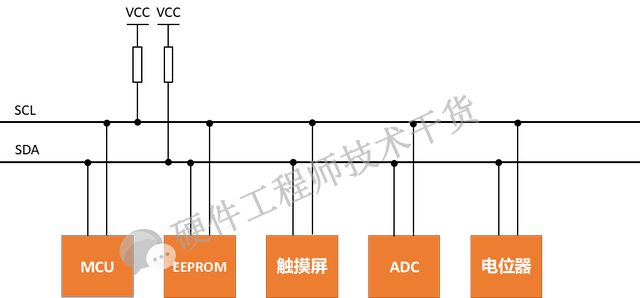

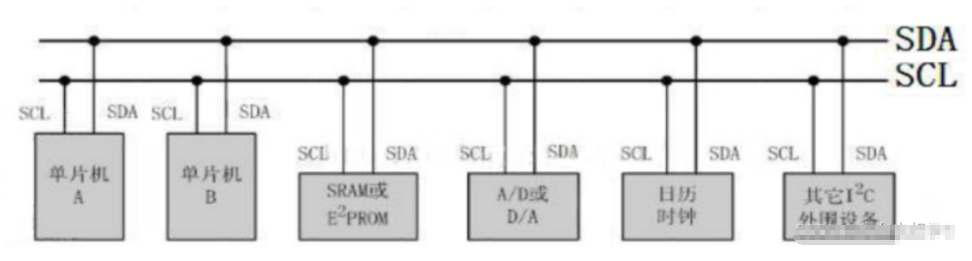

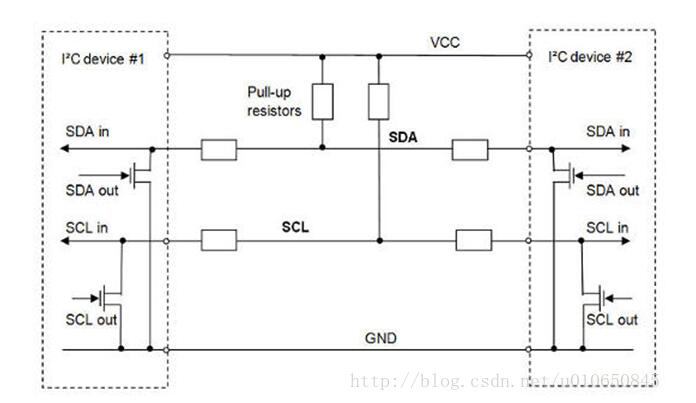

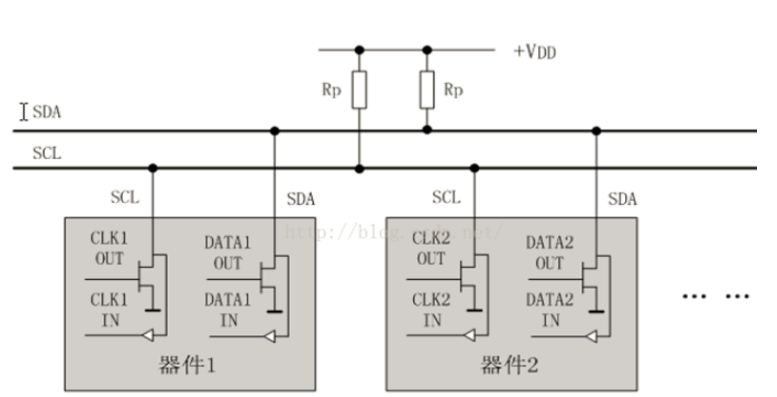

IIC總線協議及應用I2C總線知識I2C總線物理拓撲結構I2C總線特征I2C總線協議I2C總線操作IIC總線應用案例I2C總線知識I2C總線物理拓撲結構I2C 總線在物理連接上非常簡單,分別由SDA

2021-11-30 08:29:52

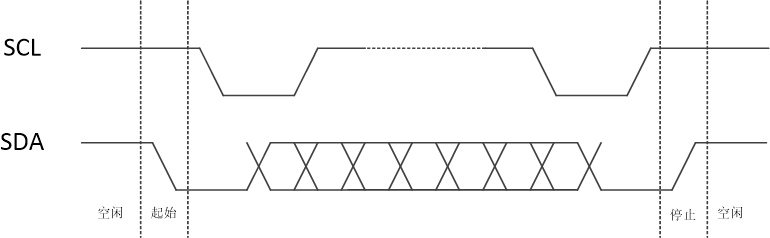

配合實現,傳輸速率包含標注準(100kps)、快速(400kps)、高速(3.4Mbps)三大類。2. IIC總線時序啟動時序:當SCL為高電平時,SDA下降沿,表示啟動。...

2021-11-29 06:20:06

IIC總線IIC總線是由數據線SDA和時鐘SCL構成的串行總線,可發送和接收數據。IIC通信多用于板內通信。PCF8591與A/D轉換PCF8591是具有IIC接口的8位A/D和D/A轉換芯片,具有

2021-12-09 07:40:31

IIC總線和SPI總線通信介紹

2020-12-23 07:02:22

設置為輸出高點片,因為總線會被自動拉高) 主機產生STOP位,終止傳輸。 EEPROM讀寫控制程序設計硬件平臺分析下面就小梅哥開發板上的EEPROM芯片編寫IIC協議讀寫EEPROM里的數據,首先

2019-03-06 03:09:52

IIC總線是什么?數據位的有效性定義是什么?IIC總線數據傳輸規范是什么?IIC總線數據幀的傳輸方式有哪幾種?

2021-07-16 06:22:49

IIC(Inter-Integrated Circuit)總線是一種由 PHILIPS 公司開發的兩線式串行線,用于連接微控制器及其外圍設備。它是由數據線 SDA 和時鐘 SCL 構成的串行總線

2022-01-24 06:19:57

IIC總線學習筆記(2020.11.8)文章目錄*IIC總線學習筆記(2020.11.8)*一、I^2^C總線背景二、I^2^C總線物理拓撲結構三、I^2^C數據傳輸3.1、起始信號3.2、終止信號

2022-01-17 08:26:37

IIC總線是怎么判斷總線是空閑的

2023-10-11 07:12:37

IIC協議是一種二線的串行總線協議。最新的IIC規范,數據傳輸率可達3.4Mbps,且提供10位尋址。常見的設備都可以與IIC總線接口,包括EPROM、FLASH存儲器、看門狗計數器和單片機等

2013-06-09 21:41:26

一.IIC簡介1.IIC總線概述IIC總線是飛利浦公司研發的兩線制串行通信總線,IIC兩線制包括:串行時鐘線(SCL)和串行數據線(SDA)。串行時鐘線(SCL)只能由主器件控制,串行數據線(SDA

2021-08-10 07:11:27

IIC總線的特點IIC總線協議詳解IIC總線的讀寫過程

2021-01-04 07:30:58

本文是本人對于IIC總線一知半解的陳述,后續在習得知識內容后會進行不斷更新,若文章中有錯誤的地方,希望各位讀者及時指正一.IIC物理層面的簡要介紹:IIC總線主要由雙向串行時鐘線SCL和串行

2022-02-28 12:40:19

IIC總線篇一、IIC總線組成兩根雙向信號線:一根數據線SDA;一根時鐘線SCL。

2021-12-13 06:28:40

1.試題所需要協調的外設有:PCF8591、數碼管、矩陣鍵盤、led、電位計RB2、AT24C02;2.難點和待解決的問題:(1)矩陣 按鍵的長按檢測和單次按鍵檢測(較難);(2)IIC總線通信協議

2022-01-19 07:56:33

藍橋杯省賽筆記之2013省賽試題模擬智能灌溉考點={ IIC總線驅動(PCF8591,EEPROM) 時鐘(DS1302) 獨立鍵盤 考點=\left\{\begin{aligned}&

2022-01-11 08:28:02

IIC時序理解IIC 的特征:兩條總線:串行數據總線(SDA)和串行時鐘總線(SCL)數據有效性規定:IIC總線在進行數據傳輸時,SCL在高電平區間,SDA上的電平必須保持穩定SDA的數據的高或者

2022-01-07 06:05:52

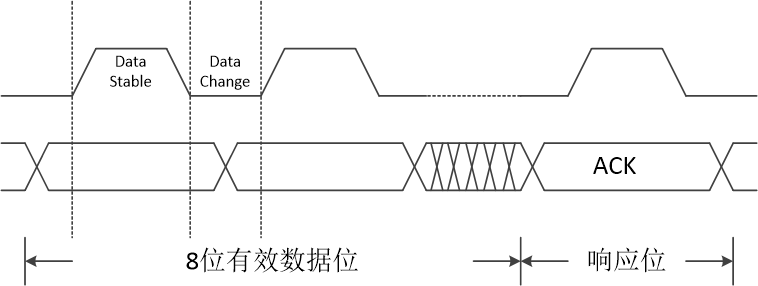

負責主動聯系從機,而從機則被動回應數據。IIC總線通過上拉電阻接正電源,總線空閑時兩根線均為高電平,連接到總線上任一器件輸出低電平都會將總線信號拉低,即各器件的SDA和SCL都是線“與”關系。2.傳輸協議2.1數據位的有效性規定SCL高電平期間SDA上的數據必須保持穩定;SCL為低電平期間SDA

2022-02-23 07:09:27

IIC是什么?IIC是一種通信是一種由 PHILIPS 公司開發的兩線式串行總線。IIC是用來傳輸數據的,也是一種通信協議。IIC的特點:IIC總線簡單而有效,占用的PCB(印制電路板)空間很小

2022-01-21 06:36:59

雙向傳送,高速IIC總線一般可達400kbps.一般在51中,沒有硬件的IIC,只能用軟件加引腳去模擬IIC的通信時序,STM32則一般都有硬件IICIIC是半雙工 通信方式2:IIC協議空閑狀態開始信號停止信號應答信號數據的有效性數據傳輸通信過程簡述空閑狀態.

2021-08-20 07:14:05

IIC通信協議詳解IIC的概述IIC分為軟件IIC和硬件IICIIC通信協議空閑狀態開始信號與停止信號開始信號程序:IIC的概述IIC:兩線式串行總線,它是由數據線SDA和時鐘線SCL構成的串行總線

2022-01-20 07:06:22

通信方式二、IIC協議1. 空閑狀態:I2C總線,總線的SDA和SCL同時處于高電平時,規定為總線的空閑狀態。2. 起始信號和停止信號:起始信號:當SCL為高期間,SDA由高到低的跳變;啟動信號是一種電平跳變時序信號,而不是一個電平信號。停止信號:當SCL為高期間,SDA由低到高的跳變;停止信

2022-01-13 07:02:55

在寫IIC總線的寫字節函數時程序為什么是這樣的void iicwr_byte(uchar dat){ucahr i;scl=0;//時鐘線拉低for(i=0;i

2012-05-08 21:28:30

SPI總線協議介紹(接口定義,傳輸時序)

2021-03-03 07:45:16

IIC簡介?IIC總線(Inter-Integrated Circuit)即集成電路總線,是Philips公司設計出來的一種簡單、雙向、二線制、同步串行總線。I2C串行總線一般有兩根信號線,一根

2022-02-23 06:48:50

,工業控制領域的X射線管配置等等。除此之外,由于IIC協議占用的IO資源特別少,連接方便,所以工程中也常選用IIC接口做為不同芯片間的通信協議。IIC協議的完成靠的是嚴緊的時序,一個周期都不能錯,這也

2019-12-04 10:36:30

串行通信中的IIC總線工作原理51本身不帶IIC總線 ,使用程序模擬IIC通信協議常用的串行總線協議UART、1-wire、I2C和SPI總線UART:是以異步方式進行通信(一條數據輸入線,一條

2021-12-08 07:52:26

1.解讀單片機IO口模擬IIC程序設計解讀單片機IO口模擬IIC程序設計2.單片機 IIC 總線協議 和 詳細例程單片機 IIC 總線協議 和 詳細例程3.主機如何確定IIC總線上的器件的地址?主機如何確定IIC總線上的器件的地址?4.這個知乎的 ;有問題,上知乎...

2022-01-18 07:11:49

- 什么是IIC總線IIC總線是同步通信的一種特殊形式,具有接線口少、控制簡單、器件封裝形式小、通信速率高等特點。在主從通信中,可以有多個IIC總線器件同時連接到IIC總線上,所有與IIC兼容的器件

2022-01-24 08:27:04

通信協議非常適合近距離低速芯片間通信。Philips(for IIC)和Motorola(for SPI) 出于不同背景和市場需求制定了這兩種標準通信協議。

2019-10-21 07:25:59

哪位大俠有關于iic總線協議的資料啊。我要具體的實例,比如24c02之類的應用

2012-07-01 15:57:50

[table][tr][td] IIC 的一些特征: 兩條總線:串行數據總線(SDA)和串行時鐘總線(SCL) 真正的多主機總線 連接到相同總線的ic數量只受到總線的最大電容400pF限制。 串行8

2018-07-19 05:33:38

代碼我放github了,還有字庫軟件。可直接運行。這里寫目錄標題IIC介紹協議起始結束等待應答字節寫封裝成寫命令和寫數據再次封裝驅動OLEDGPIO初始化OLED初始化主函數展示IIC介紹IIC:兩

2021-08-12 06:54:28

;><strong>通用IIC總線驅動程序設計及實時時鐘芯片PCF8563的控制實例<br/></strong&

2009-10-31 16:24:02

長虹G2988彩電IIC總線EEPROM數據

2009-05-26 09:01:27 24

24 長虹G2988彩電IIC總線EEPROM數據(1)

2009-05-26 09:09:55 26

26 長虹H2111K彩電IIC總線EEPROM數據

2009-05-26 09:23:36 172

172 長虹SF2166K彩電IIC總線EEPROM數據

2009-05-26 10:15:48 93

93 TCL AT25A192彩電IIC總線EEPROM數據

2009-06-12 10:37:16 28

28 介紹了IIC 總線在嵌入式WEB Server 系統中的應用,詳細講述了利用IIC 總線擴展該系統的數碼管顯示及鍵盤輸入,給出了ARM 芯片S3C4510 的IIC 總線主控器的應用方案及編程方法。關

2009-08-19 09:53:31 9

9 在多主設備IIC 總線模式下,多個S3C2440A 微處理器可以從從屬設備接收或發送串行數據。主設備S3C2440A 可以初始化和終止一個基于IIC 總線的數據傳輸。在S3C2440A 中的IIC 總線使用標準總線

2012-04-27 15:31:07 61

61 iic總線的詳細說明,協議說明,教程,學習

2015-11-16 19:05:14 0

0 1,本文給出了 linux 下使用 IIC 總線讀寫 EEPROM 的實現程序。

2 本文給出了在編程中遇到的幾種非常隱蔽的錯誤的解決方法。

3,本文的讀寫程序非常通用

2016-01-06 11:05:35 17

17 IIC總線在移動智能終端領域中的應用.....

2016-01-04 17:03:55 26

26 IIC總線的概念,及操作方法,單片機必學內容

2016-01-11 16:42:43 61

61 LESSON8_IIC總線協議 LESSON8_IIC總線協議

2016-02-18 18:23:24 0

0 iic總線通信,要的人速度下載看看哦。

2016-03-21 13:50:17 30

30 24C02中IIC總線的應答信號(ACK)時序圖分析,很好的單片機學習資料。

2016-03-21 17:30:06 94

94 HL配套C實驗例程IIC總線基本驅動程序(參考),配合開發板學習效果更好。

2016-04-11 17:04:33 6

6 iic總線協議,通訊方式,通訊工作原理!單片機入門知識

2016-06-17 16:48:12 11

11 IIC總線協議,感興趣的小伙伴們可以看看。

2016-07-26 16:29:36 60

60 IIC協議的介紹,中文版,易懂,可以在里面了解到IIC是何物,如何使用以及定義

2016-08-09 15:08:27 0

0 AT24C02是由ATMEL公司提供的,IIC總線串行EEPROM(electronic eraser programmer read only memory),其容量為2kbit(256B),工作電壓在2.7v“5.5v之間,生產工藝是CMOS。

2017-11-16 14:29:04 12630

12630

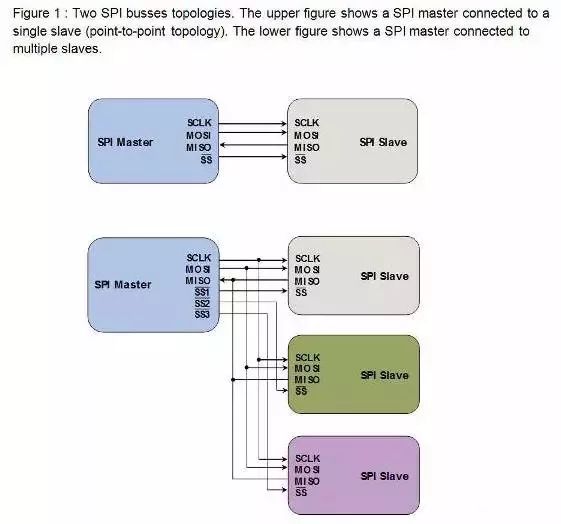

IIC vs SPI: 哪位是贏家?我們來對比一下IIC 和 SPI的一些關鍵點:

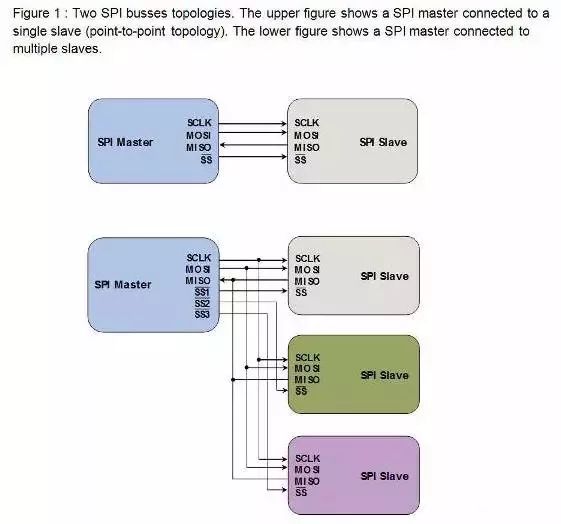

第一,總線拓撲結構/信號路由/硬件資源耗費IIC 只需兩根信號線,而標準SPI至少四根信號,如果有多個從設備,信號需要更多。

2017-12-22 16:48:22 19524

19524

通信協議非常適合近距離低速芯片間通信。Philips(for IIC)和Motorola(for SPI) 出于不同背景和市場需求制定了這兩種標準通信協議。

2018-04-24 12:41:00 6974

6974

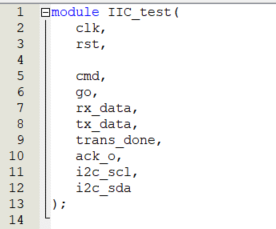

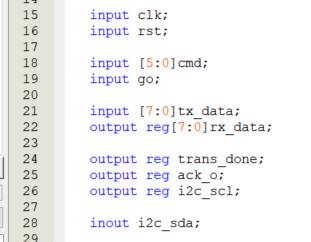

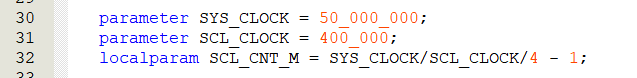

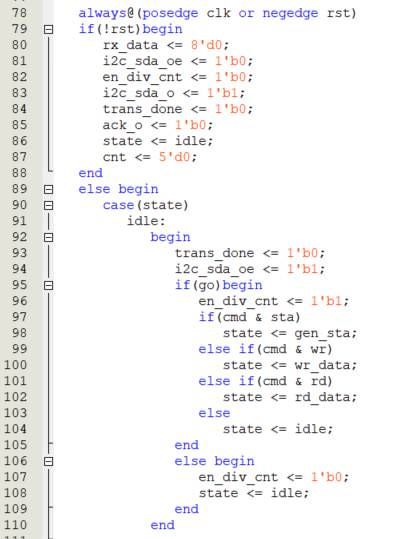

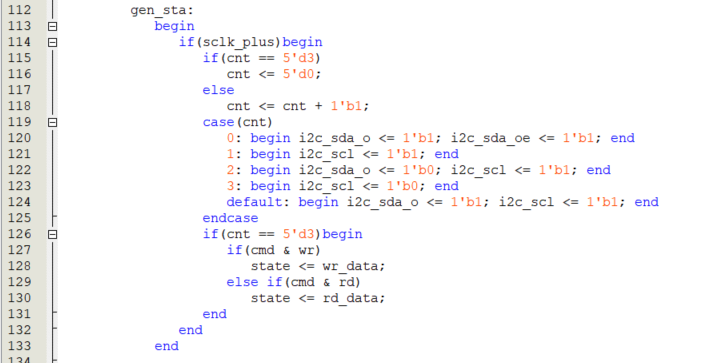

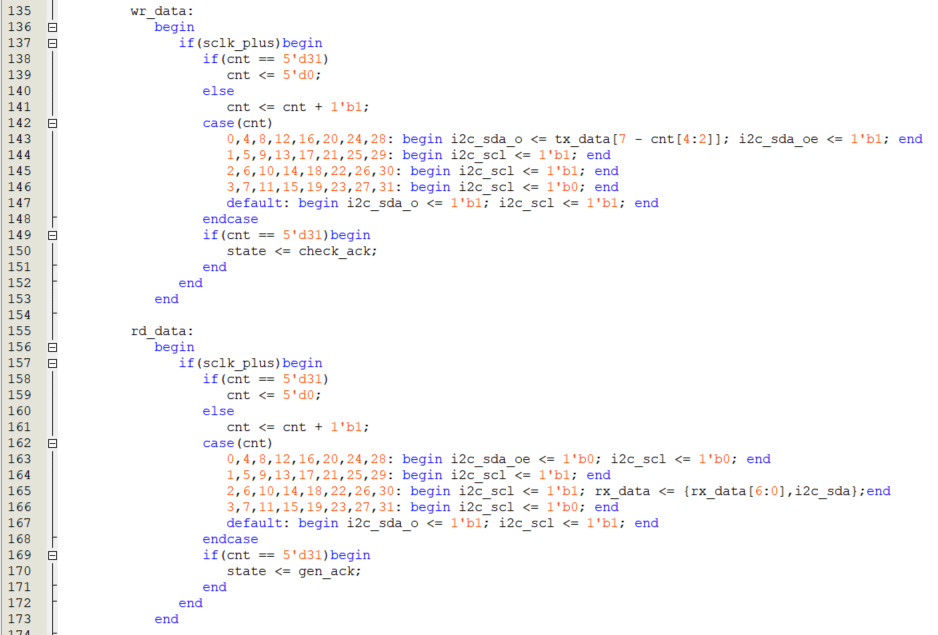

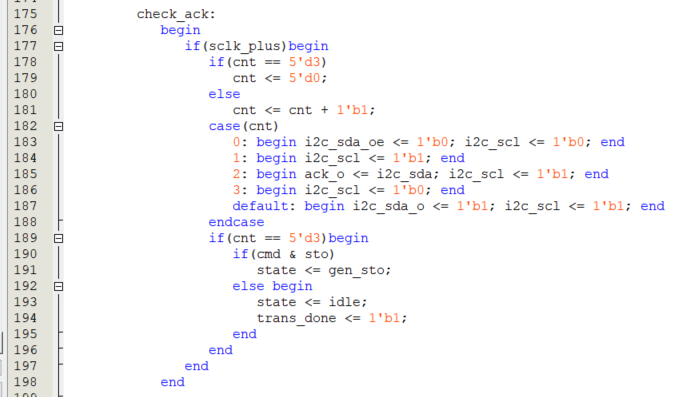

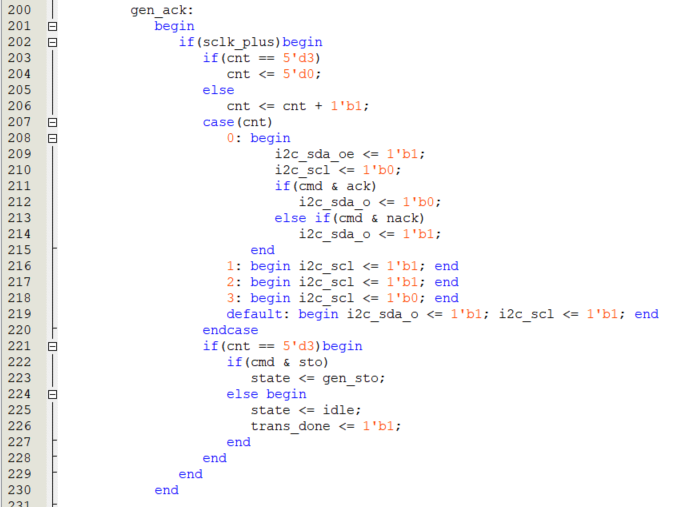

本文首先介紹了IIC總線概念和IIC總線硬件結構,其次介紹了IIC總線典型應用,最后詳細介紹了IIC總線的FPGA實現原理及實現過程。

2018-05-31 10:56:50 7184

7184

一 IIC概念及特點

1、IIC概念

2、主要特點

二 IIC時序介紹

1、IIC總線時序

2、IIC通信過程

三 編程時使用的幾個概念

1、時鐘速率

2、起始條件和停止條件

3

2018-07-02 10:07:12 6517

6517 本文檔的主要內容詳細介紹的是IIC總線初始化基本驅動參考程序應用代碼免費下載。程序功能:為IIC總線的基本驅動程序(此程序沒有寫主函數,只是一些IIC必備的子函數)

2019-01-16 08:00:00 5

5 地一系列模塊。 本來想寫篇文章簡單介紹下我對IIC總線的理解的, 但, 發現沒工夫, 所以, 放在以后有時候再來弄吧。 今天我還是只給出一個范例程序, 它能在我的51單片機機系統上工作得很好。 iic.h 列出了所有IIC總線的操作函數。 下面給出源代碼:

2019-09-27 17:15:00 3

3 S3C2440A RISC 微處理器可以支持多主設備 IIC 總線串行接口。專用串行數據線(SDA)和串行時鐘線(SCL)承載總線主設備和連接IIC總線的外圍設備之間的信息。SDA和SCL 線都是

2020-05-18 08:00:00 6

6 IIC協議是一種總線協議,是串行的,是同步的,是半雙工的。它通信速率最高就只有幾百 KB/s 。

2020-12-25 15:26:42 8807

8807

MCU_IIC總線

2021-11-16 09:36:02 20

20 IIC總線協議及應用I2C總線知識I2C總線物理拓撲結構I2C總線特征I2C總線協議I2C總線操作IIC總線應用案例I2C總線知識I2C總線物理拓撲結構I2C 總線在物理連接上非常簡單,分別由SDA

2021-11-20 15:21:01 10

10 什么是IIC 總線?IIC是Inter IC Bus的縮寫,是由PHLIPS提出的一種串行總線,具備多主機系統所需要的包括總線裁決和高低速器件同步功能的高性能串行總線。IIC總線有時稱為I2C總線

2021-11-23 16:20:36 14

14 51單片機實驗12:EEPROM(IIC總線) 應用

2021-11-23 16:36:16 21

21 串行通信中的IIC總線工作原理51本身不帶IIC總線 ,使用程序模擬IIC通信協議常用的串行總線協議UART、1-wire、I2C和SPI總線UART:是以異步方式進行通信(一條數據輸入線,一條

2021-11-25 15:51:04 11

11 一、環境介紹編程軟件: keil5操作系統: win10MCU型號: STM32F103ZET6STM32編程方式: 寄存器開發 (方便程序移植到其他單片機)IIC總線:STM32本身支持IIC硬件

2021-11-25 20:06:02 39

39 - 什么是IIC總線IIC總線是同步通信的一種特殊形式,具有接線口少、控制簡單、器件封裝形式小、通信速率高等特點。在主從通信中,可以有多個IIC總線器件同時連接到IIC總線上,所有與IIC兼容的器件

2021-11-29 11:21:08 5

5 IIC的使用IIC總線簡介IIC通信時序IIC總線尋址IIC總線簡介1、IIC總線是一種由PHILIPS公司開發的兩線式串行總線2、IIC在硬件上是時鐘總線SCL和數據總線SDA兩條線構成3、器件

2021-12-04 16:06:09 14

14 負責主動聯系從機,而從機則被動回應數據。IIC總線通過上拉電阻接正電源,總線空閑時兩根線均為高電平,連接到總線上任一器件輸出低電平都會將總線信號拉低,即各器件的SDA和SCL都是線“與”關系。2.傳輸協議2.1 數據位的有效性規定SCL高電平期間SDA上的數據必須保持穩定;SCL為低電平期間SDA

2021-12-29 19:31:11 0

0 **EEPROM芯片:**掉電不會丟失數據,可以保存數據。IIC串行總線的組成及工作原理:

2021-12-29 19:33:44 11

11 文章目錄IIC總線上掛在多個從機的程序實現IIC簡介:1、項目的硬件參考電路:2、程序實現:IIC總線上掛在多個從機的程序實現IIC簡介:1、I2C總線具有兩根雙向信號線,一根是數據線SDA,另一

2022-01-12 19:09:46 13

13 IIC總線學習筆記(2020.11.8)文章目錄*IIC總線學習筆記(2020.11.8)*一、I^2^C總線背景二、I^2^C總線物理拓撲結構三、I^2^C數據傳輸3.1、起始信號3.2、終止信號

2022-01-17 13:33:06 6

6 IIC總線規范,詳細介紹了IIC總線傳輸、仲裁、尋址、高低速模式等。

2022-02-22 14:35:55 0

0 AXI IIC 和 PS IIC 控制器都符合 NXP IIC 總線規范。用戶必須確保其選擇使用的從設備的時序參數與UM10204 的第 48 頁上的“表 10”中的參數相同。

2022-08-25 10:29:08 2548

2548 IIC(Inter-Integrated Circuit)總線是一種由PHILIPS公司開發的兩線式串行總線,用于連接微控制器及其外圍設備。

2023-06-30 09:03:19 2552

2552

iic總線最多可以掛多少個從設備?? IIC總線,也被稱為I2C總線,是一種串行通信協議,廣泛使用于數字電路和電腦內部件之間的通訊。該協議允許多個器件共用簡單的通訊線,以低成本、低功耗的方式實現多

2023-09-12 11:36:44 9851

9851 大家在使用MCU IIC通信時,若碰到設備復位或者總線干擾等情況,可能會導致IIC總線卡死,表現上總線上SDA或者SCL其中一根線為低電平,IIC總線一直處于busy狀態。此時若代碼上一直等待總線空閑,則可能導致軟件死機,為解決該問題,本視頻提供了軟件配置釋放IIC總線的方法。

2024-02-24 09:46:13 5396

5396

電子發燒友App

電子發燒友App

評論