前言 SDRAM控制器里面包含5個主要的模塊,分別是PLL模塊,異步FIFO 寫模塊,異步FIFO讀模塊,SDRAM接口控制模塊,SDRAM指令執行模塊。 其中異步FIFO模塊解讀

2025-03-04 10:49:01 2301

2301

現代集成電路芯片中,隨著設計規模的不斷擴大。一個系統中往往含有數個時鐘。多時鐘帶來的一個問題就是,如何設計異步時鐘之間的接口電路。異步 FIFO(First In First Out)是解決這個問題的一種簡便、快捷的解決方案。##異步FIFO的VHDL語言實現

2014-05-28 10:56:41 9209

9209 大家好,又到了每日學習的時間了,今天我們來聊一聊基于FPGA的異步FIFO的實現。 一、FIFO簡介 FIFO是英文First In First Out 的縮寫,是一種先進先出的數據緩存器,它與普通

2018-06-21 11:15:25 7148

7148

異步 FIFO 讀寫分別采用相互異步的不同時鐘。在現代集成電路芯片中,隨著設計規模的不斷擴大,一個系統中往往含有數個時鐘,多時鐘域帶來的一個問題就是,如何設計異步時鐘之間的接口電路。異步 FIFO

2020-07-16 17:41:46 1530

1530

FIFO (先入先出, First In First Out )存儲器,在 FPGA 和數字 IC 設計中非常常用。 根據接入的時鐘信號,可以分為同步 FIFO 和異步 FIFO 。

2023-06-27 10:24:37 3136

3136

相鄰的格雷碼只有1bit的差異,因此格雷碼常常用于異步fifo設計中,保證afifo的讀地址(或寫地址)被寫時鐘(或讀時鐘)采樣時最多只有1bit發生跳變。

2023-11-01 17:37:31 2498

2498

FIFO為什么不能正常工作?復位信號有效長度不夠,接口時序不匹配,可看下面這篇文章。 本文將介紹: 非DFX工程如何確保異步FIFO自帶的set_max_delay生效? DFX工程如何確保異步

2023-11-02 09:25:01 2266

2266

如圖所示的異步FIFO,個人覺得在讀寫時鐘同步時會產生兩個時鐘周期的延時,如果讀寫時鐘頻率相差不大,某一時刻讀寫指針相等,當寫指針同步到讀模塊時會產生延時,實際同步到讀模塊的寫指針是兩個時鐘周期之前的,這樣就不會產生空滿信號,要兩個周期之后才能產生空滿信號,結果是寫溢出或讀空

2015-08-29 18:30:49

異步FIFO介紹異步FIFO的設計難點是什么,怎么解決這些難點?

2021-04-08 06:08:24

始條件: 讀寫時鐘都是100MHz,但是讀寫時鐘不同步(存在相位差,也可能存在精度問題),FIFO深度為16(最小的深度),在固定時刻進行異步復位,復位條件按照Memory User Guide中

2013-12-29 10:32:13

本帖最后由 eehome 于 2013-1-5 09:48 編輯

深入講解異步FIFO的問題

2013-01-01 22:26:57

XINLINX FPGA與CY7C68013通訊,異步slave fifo通訊方式,PKTEND信號的作用是什么,不用的話是不是應該拉高 ,另外由于fifo adr用的都公用地址線,時序上怎么選擇,誰能共享一下verilog HDL的例子。

2015-07-10 15:17:28

勇敢的芯伴你玩轉Altera FPGA連載89:FPGA片內異步FIFO實例特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD功能概述該工程

2019-05-06 00:31:57

`Xilinx FPGA入門連載55:FPGA 片內異步FIFO實例之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能

2016-03-07 11:32:16

cy7c68013a 異步slave fifo 模式,外部mcu無法讀寫fifo

上位機發送bulk數據,flag標志是對的,SLCS也拉低了,是設置的低有效, 檢測到了flag不為空的標志后

2025-06-03 10:49:04

最近用到異步FIFO,發現其中的show-ahead模式很有意思。如下圖,對FIFO IP核仿真后,可以看到在寫請求信號上升沿兩個時鐘周期后數據被寫入,三個時鐘周期后FIFO輸出端就有數據輸出,而

2020-02-21 15:50:27

本帖最后由 630183258 于 2016-11-5 17:31 編輯

一、異步fifo的原理圖管腳定義:data輸入數據q輸出數據wrreq寫使能信號,高電平有效wrfull寫數據滿標志位

2016-11-05 16:57:51

使用它來驅動異步fifo輸入時鐘。然后我會抓住輸出并創建像我以前那樣的啟用如果它改變了答案,這里有一些具體細節:1 MHz時鐘數據在時鐘下降沿之前200 ns有效。保持有效期為250ns。當時鐘無效

2019-07-26 13:54:21

FIFO是FPGA處理跨時鐘和數據緩存的必要IP,可以這么說,只要是任意一個成熟的FPGA涉及,一定會涉及到FIFO。但是我在使用異步FIFO的時候,碰見幾個大坑,這里總結如下,避免后來者入坑。

2021-02-04 06:23:41

關于異步fifo的安全問題:1. 雖然異步fifo可以提供多個握手信號,但真正影響安全性能的就兩個:2. 一個是讀時鐘域的空信號rdrempty3. 另一個是寫時鐘域的滿信號wrfull4. 這是

2018-03-05 10:40:33

這是網上比較流行的一個異步fifo方案,但是fifo的空滿判斷不是應該是立即的嗎,加上同步器之后變成寫指針要延時兩個讀周期再去個讀指針做空比較,而讀指針要延時兩個寫周期再去和寫指針做滿比較,這樣雖然可以避免亞穩態之類的問題,可是這個延時對總體的空滿判斷沒有影響嗎,如果沒有影響是怎么做到的呢,求解

2016-07-24 16:25:33

求一款基于VHDL的異步串行通信電路設計分享

2021-04-08 06:16:42

`勇敢的芯伴你玩轉Altera FPGA連載89:FPGA片內異步FIFO實例特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 功能概述

2018-08-28 09:39:16

我想問一下什么情況下需要用異步FIFO,什么情況下用同步FIFO?

2014-11-03 17:19:54

FIFO芯片是什么?如何利用FIFO去實現DSP間雙向并行異步通訊?

2021-06-02 06:08:17

本文介紹利用VHDL語言實現 FPGA與單片機的串口異步通信電路。

2021-04-29 06:34:57

FIFO的基本結構和工作原理異步FIFO設計中的問題與解決辦法FPGA內部軟異步FIFO設計

2021-04-08 07:07:45

各位大神: 異步FIFO的空 滿信號為什么都是高?描述如下:always @(posedge DFIFO_clk or negedge rst_n )beginif(!rst_n)beginWRITE_req

2015-07-01 01:51:58

求助各位,這是我的一個異步FIFO的實驗,異步FIFO這里在wrreq置高后開始寫數據時,為啥第一個wrclk上升沿時wrusedw還是0啊,到第二個才加1,我覺得應該是圖里黃線的地方就加1,問一下這是為什么,麻煩各位大神了

2018-06-05 21:49:38

也就是說用一個25M頻率的FIFO寫入數據,用另一個100M(或者不同頻)的FIFO讀出數據。該如何實現呢?不使用異步FIFO

2020-12-03 20:47:22

我在網上看到一篇利用格雷碼來設計異步FIFO,但是看他們寫的一些源碼,小弟有些不是很理解,在設計時為什么會出現Waddr和wptr兩個關于寫指針的問題,他們之間的關系是什么????wptr在定義時候為什么比Waddr多一位呀???

2017-05-19 11:04:13

本文討論了在ASIC設計中數據在不同時鐘之間傳遞數據所產生的亞穩態問題,并提出了一種新的異步FIFO的設計方法,并用VHDL語言進行描述,利用Altera公司的Cyclone系列的EP1C6進行硬件實現,該電路軟件仿真和硬件實現已經通過驗證,并應用到各種電路中。

2021-04-29 06:54:00

為什么要設計一種異步FIFO?異步FIFO的設計原理是什么?怎樣去設計一種異步FIFO?

2021-06-18 09:20:29

包括各種類型存儲器的VHDL描述,如FIFO,雙口RAM等

2008-05-20 11:32:14 48

48 首先介紹異步FIFO 的概念、應用及其結構,然后分析實現異步FIFO的難點問題及其解決辦法; 在傳統設計的基礎上提出一種新穎的電路結構并對其進行綜合仿真和FPGA 實現。

2009-04-16 09:25:29 46

46 通用存儲器 包括各種類型存儲器的VHDL描述,如FIFO,雙口RAM等VHDL代碼庫

-- The Free IP Project-- VHDL Free-RAM

2009-06-14 09:35:12 74

74 通用異步串行接口(Universal Asynchronous Receiver Transmitter,UART)在通信、控制等領域得到了廣泛應用。根據UART 接口特點和應用需求,以提高VHDL 設計的穩定性和降低功耗為目標,

2009-09-02 11:06:25 23

23 設計一個FIFO是ASIC設計者遇到的最普遍的問題之一。本文著重介紹怎樣設計FIFO——這是一個看似簡單卻很復雜的任務。一開始,要注意,FIFO通常用于時鐘域的過渡,是雙時鐘設計

2009-10-15 08:44:35 94

94 通用異步串行接口(Universal Asynchronous Receiver Transmitter,UART)在通信、控制等領域得到了廣泛應用。根據UART 接口特點和應用需求,以提高VHDL 設計的穩定性和降低功耗為目標,

2009-11-30 15:34:00 19

19 本文主要研究了用FPGA 芯片內部的EBRSRAM 來實現異步FIFO 設計方案,重點闡述了異步FIFO 的標志信號——空/滿狀態的設計思路,并且用VHDL 語言實現,最后進行了仿真驗證。

2010-01-13 17:11:58 40

40 給出了一個利用格雷碼對地址編碼的羿步FIFO 的實現方法,并給出了VHDL 程序,以解決異步讀寫時鐘引起的問題。

2010-07-16 15:15:42 26

26 介紹了異步FIFO在Camera Link接口中的應用,將Camera Link接口中的幀有效信號FVAL和行有效信號LVAL引入到異步FIFO的設計中。分析了FPGA中設計異步FIFO的難點,解決了異步FIFO設計中存在的兩

2010-07-28 16:08:06 32

32 摘要:使用FIFO同步源自不同時鐘域的數據是在數字IC設計中經常使用的方法,設計功能正確的FUFO會遇到很多問題,探討了兩種不同的異步FIFO的設計思路。兩種思路

2006-03-24 12:58:33 1660

1660

摘要:首先介紹異步FIFO的概念、應用及其結構,然后分析實現異步FIFO的難點問題及其解決辦法;在傳統設計的基礎上提出一種新穎的電路結構并對其進行

2009-06-20 12:46:50 4131

4131

高速異步FIFO的設計與實現

引言

現代集成電路芯片中,隨著設計規模的不斷擴大.一個系統中往往含有數個時鐘。多時鐘帶來的一個問題就是,如何設

2010-04-12 15:13:08 3176

3176

本文采用VHDL描述語言,充分利用Xilinx公司Spartan II FPGA的系統資源,設計實現了一種非對稱同步FIFO,它不僅提供數據緩沖,而且能進行數據總線寬度的轉換。

2011-01-13 11:33:43 2240

2240 文中給出了異步FIFO的實現代碼和FPGA與DSP的硬件連接電路。經驗證,利用異步FIFO的方法,在FPGA與DSP通信中的應用,具有傳輸速度快、穩定可靠、實現方便的優點。

2011-12-12 14:28:22 51

51 異步FIFO結構及FPGA設計,解決亞穩態的問題

2015-11-10 15:21:37 4

4 異步FIFO在FPGA與DSP通信中的運用

2016-05-19 11:17:11 0

0 VHDL例程 FIFO程序,感興趣的小伙伴們可以瞧一瞧。

2016-11-10 17:12:34 4

4 基于異步FIFO在FPGA與DSP通信中的運用

2017-10-19 10:30:56 10

10 介紹了利用CYPRESS公司的FIFO芯片CY7C419實現DSP間雙向并行異步通訊的方法,該方法簡單實用,速度快,特別適用于小數據量的數據相互傳送。文中給出了CY7C419的引腳功能以及用FIFO

2017-10-25 11:35:25 0

0 摘要 利用異步FIFO實現FPGA與DSP進行數據通信的方案。FPGA在寫時鐘的控制下將數據寫入FIFO,再與DSP進行握手后,DSP通過EMIFA接口將數據讀入。文中給出了異步FIFO的實現

2017-10-30 11:48:44 3

3 本文首先對異步 FIFO 設計的重點難點進行分析,最后給出詳細代碼。 一、FIFO簡單講解 FIFO的本質是RAM, 先進先出 重要參數:fifo深度(簡單來說就是需要存多少個數據) fifo位寬

2017-11-15 12:52:41 9176

9176

在現代電路設計中,一個系統往往包含了多個時鐘,如何在異步時鐘間傳遞數據成為一個很重要的問題,而使用異步FIFO可以有效地解決這個問題。異步FIFO是一種在電子系統中得到廣泛應用的器件,文中介紹了一種基于FPGA的異步FIFO設計方法。使用這種方法可以設計出高速、高可靠的異步FIFO。

2018-07-17 08:33:00 8860

8860

在現代的集成電路芯片中,隨著設計規模的不斷擴大,一個系統中往往含有數個時鐘。多時鐘域帶來的一個問題就是,如何設計異步時鐘之間的接口電路。異步FIFO(Firstln F irsto ut)是解決這個

2018-02-07 14:22:54 0

0 異步FIFO(Fist-In-First-Out)是一種先入先出的數據緩沖器[1]。由于可以很好地解決跨時鐘域問題和不同模塊之間的速度匹配問題,而被廣泛應用于全局異步局部同步[2](Globally

2018-06-19 15:34:00 3780

3780

異步FIFO廣泛應用于計算機網絡工業中進行異步數據傳送,這里的異步是指發送用一種速率而接收用另一速率,因此異步FIFO有兩個不同的時鐘,一個為讀同步時鐘,一個為寫同步時鐘。

2019-06-11 08:00:00 3853

3853

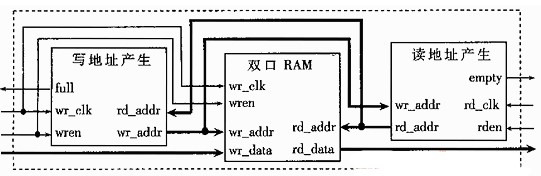

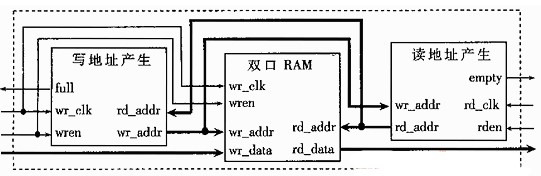

FIFO (先進先出隊列)是一種在電子系統得到廣泛應用的器件,通常用于數據的緩存和用于容納異步信號的頻率或相位的差異。FIFO的實現通常是利用雙口RAM和讀寫地址產生模塊來實現的。FIFO的接口

2019-08-02 08:10:00 2868

2868

一般而言,處理跨時鐘域的方法有這么幾種(大家在網上也都能找到資料,這些資料大都來自幾篇經典的論文,中文方面的資料大都是翻譯過著理解這幾篇論文而來):少量的數據用邊沿檢測電路,或者脈沖檢測電路,或者電平檢測電路,或者兩級觸發器;比較多的數據時用異步FIFO。

2018-09-10 10:06:00 13063

13063

跨時鐘域的問題:前一篇已經提到要通過比較讀寫指針來判斷產生讀空和寫滿信號,但是讀指針是屬于讀時鐘域的,寫指針是屬于寫時鐘域的,而異步FIFO的讀寫時鐘域不同,是異步的,要是將讀時鐘域的讀指針與寫時鐘域的寫指針不做任何處理直接比較肯定是錯誤的,因此我們需要進行同步處理以后進行比較。

2018-09-05 14:29:36 6636

6636 根據FIFO工作的時鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時鐘和寫時鐘為同一個時鐘。在時鐘沿來臨時同時發生讀寫操作。異步FIFO是指讀寫時鐘不一致,讀寫時鐘是互相獨立的。

2019-11-29 07:08:00 2265

2265 異步FIFO存儲器是一種在數據交互系統中得到廣泛應用的先進先出邏輯器件,具有容納異步信號的頻率(或相位差異)的特點。使用異步FIFO可以在兩個不同時鐘系統之間快速而方便地傳輸實時數據。因此,異步FIFO被廣泛應用于實時數據傳輸、網絡接口、圖像處理等方面。

2020-01-29 16:54:00 1265

1265

一、概述 在大規模ASIC或FPGA設計中,多時鐘系統往往是不可避免的,這樣就產生了不同時鐘域數據傳輸的問題,其中一個比較好的解決方案就是使用異步FIFO來作不同時鐘域數據傳輸的緩沖區,這樣既可以

2020-07-17 09:38:20 911

911

隨著數字電子系統設計規模的擴大,一些實際應用系統中往往含有多個時鐘,數據不可避免地要在不同的時鐘域之間傳遞。如何在異步時鐘之間傳輸數據,是數據傳輸中一個至關重要的問題,而采用FIFO正是解決這一

2020-07-21 17:09:36 1931

1931

FIFO是FPGA處理跨時鐘和數據緩存的必要IP,可以這么說,只要是任意一個成熟的FPGA涉及,一定會涉及到FIFO。但是我在使用異步FIFO的時候,碰見幾個大坑,這里總結如下,避免后來者入坑。

2021-03-12 06:01:34 12

12 1.定義 FIFO是英文First In First Out 的縮寫,是一種先進先出的數據緩存器,他與普通存儲器的區別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點就是只能順序寫入數據,順序

2021-04-09 17:31:42 6216

6216

異步FIFO通過比較讀寫地址進行滿空判斷,但是讀寫地址屬于不同的時鐘域,所以在比較之前需要先將讀寫地址進行同步處理,將寫地址同步到讀時鐘域再和讀地址比較進行FIFO空狀態判斷(同步后的寫地址一定

2021-08-04 14:05:21 5131

5131 一、概述 在大規模ASIC或FPGA設計中,多時鐘系統往往是不可避免的,這樣就產生了不同時鐘域數據傳輸的問題,其中一個比較好的解決方案就是使用異步FIFO來作不同時鐘域數據傳輸的緩沖區,這樣既可以

2021-09-30 09:57:40 2382

2382

跨時鐘域處理 & 亞穩態處理&異步FIFO1.FIFO概述FIFO: 一、先入先出隊列(First Input First Output,FIFO)這是一種傳統的按序執行方法,先進

2021-12-17 18:29:31 10

10 在大規模ASIC或FPGA設計中,多時鐘系統往往是不可避免的,這樣就產生了不同時鐘域數據傳輸的問題,其中一個比較好的解決方案就是使用異步FIFO來作不同時鐘域數據傳輸的緩沖區,這樣既可以使相異時鐘域數據傳輸的時序要求變得寬松,也提高了它們之間的傳輸效率。此文內容就是闡述異步FIFO的設計。

2022-03-09 16:29:18 3457

3457 FIFO的分類根均FIFO工作的時鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時鐘和寫時鐘為同一個時鐘。在時鐘沿來臨時同時發生讀寫操作。異步FIFO是指讀寫時鐘不一致,讀寫時鐘是互相獨立的。

2022-11-01 09:57:08 2857

2857 同步FIFO的意思是說FIFO的讀寫時鐘是同一個時鐘,不同于異步FIFO,異步FIFO的讀寫時鐘是完全異步的。同步FIFO的對外接口包括時鐘,清零,讀請求,寫請求,數據輸入總線,數據輸出總線,空以及滿信號。

2022-11-01 09:58:16 2461

2461 FIFO 是我們設計中常用的工具,因為它們使我們能夠在進行信號和圖像處理時緩沖數據。我們還使用異步FIFO來處理數據總線的時鐘域交叉問題。

2022-11-04 09:14:11 6431

6431 異步fifo詳解 一. 什么是異步FIFO FIFO即First in First out的英文簡稱,是一種先進先出的數據緩存器,與普通存儲器的區別在于沒有外部讀寫的地址線,缺點是只能順序的讀取

2022-12-12 14:17:41 5421

5421 FIFO用于為匹配讀寫速度而設置的數據緩沖buffer,當讀寫時鐘異步時,就是異步FIFO。多bit的數據信號,并不是直接從寫時鐘域同步到讀時鐘域的。

2023-01-01 16:48:00 1857

1857 FIFO(First In First Out)是異步數據傳輸時經常使用的存儲器。該存儲器的特點是數據先進先出(后進后出)。其實,多位寬數據的異步傳輸問題,無論是從快時鐘到慢時鐘域,還是從慢時鐘到快時鐘域,都可以使用 FIFO 處理。

2023-03-26 16:00:21 4788

4788

FIFO(First In First Out )先入先出存儲器,在FPG設計中常用于跨時鐘域的處理,FIFO可簡單分為同步FIFO和異步FIFO。

2023-04-25 15:55:28 5975

5975

FIFO是異步數據傳輸時常用的存儲器,多bit數據異步傳輸時,無論是從快時鐘域到慢時鐘域,還是從慢時鐘域到快時鐘域,都可以使用FIFO處理。

2023-05-26 16:12:49 2243

2243

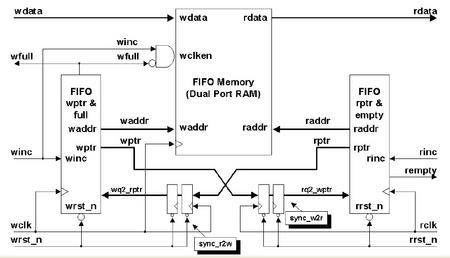

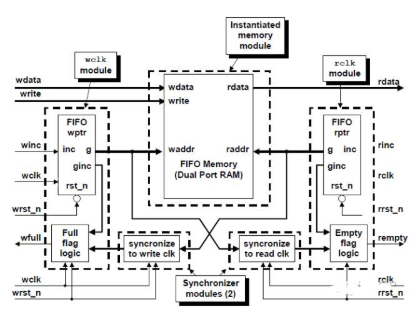

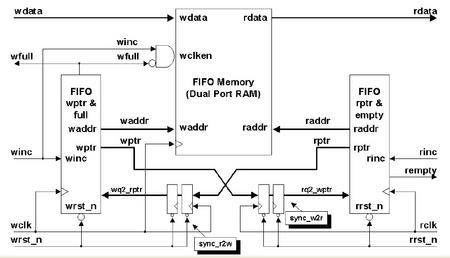

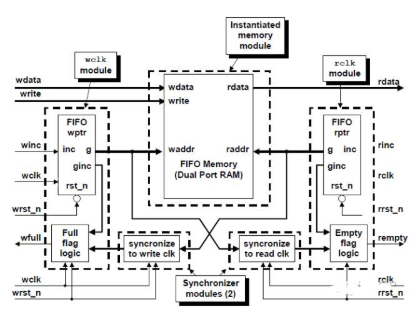

異步FIFO主要由五部分組成:寫控制端、讀控制端、FIFO Memory和兩個時鐘同步端

2023-05-26 16:17:20 2201

2201

在ASIC設計或者FPGA設計中,我們常常使用異步fifo(first in first out)(下文簡稱為afifo)進行數據流的跨時鐘,可以說沒使用過afifo的Designer,其設計經歷是不完整的。廢話不多說,直接上接口信號說明。

2023-07-31 11:10:19 3403

3403

很多人在面試時被問到為什么異步FIFO中需要用到格雷碼,可能大部分的答案是格雷碼可以消除亞穩態。這種回答比較模糊,今天我們就針對這個來深入探討一下。

2023-08-26 14:20:25 1653

1653

異步FIFO包含"讀"和"寫“兩個部分,寫操作和讀操作在不同的時鐘域中執行,這意味著Write_Clk和Read_Clk的頻率和相位可以完全獨立。異步FIFO

2023-09-14 11:21:45 2182

2182

同步FIFO和異步FIFO的區別 同步FIFO和異步FIFO各在什么情況下應用? 1. 同步FIFO和異步FIFO的區別 同步FIFO和異步FIFO在處理時序有明顯的區別。同步FIFO相對來說是較為

2023-10-18 15:23:58 2603

2603 請問異步FIFO的溢出操作時怎么樣判斷的? 異步FIFO是數據傳輸的一種常用方式,在一些儲存器和計算機系統中,常常會用到異步FIFO。作為一種FIFO,異步FIFO經常面臨兩種情況:溢出和空槽位

2023-10-18 15:28:41 4290

4290 電子發燒友網站提供《異步FIFO結構設計.pdf》資料免費下載

2024-02-06 09:06:27 0

0 ,并且間隔時間長,也就是突發寫入。那么通過設置一定深度的FIFO,可以起到數據暫存的功能,且使得后續處理流程平滑。 時鐘域的隔離:主要用異步FIFO。對于不同時鐘域的數據傳輸,可以通過FIFO進行隔離,避免跨時鐘域的數據傳輸帶來的設計和約束上的復

2024-06-04 14:27:37 3489

3489

電子發燒友網站提供《具有FIFO的雙異步通信元件TL16C552A數據表.pdf》資料免費下載

2024-06-26 11:28:20 0

0

電子發燒友App

電子發燒友App

評論