前言 SDRAM控制器里面包含5個主要的模塊,分別是PLL模塊,異步FIFO 寫模塊,異步FIFO讀模塊,SDRAM接口控制模塊,SDRAM指令執(zhí)行模塊。 其中異步FIFO模塊解讀

2025-03-04 10:49:01 2301

2301

現(xiàn)代集成電路芯片中,隨著設(shè)計規(guī)模的不斷擴大。一個系統(tǒng)中往往含有數(shù)個時鐘。多時鐘帶來的一個問題就是,如何設(shè)計異步時鐘之間的接口電路。異步 FIFO(First In First Out)是解決這個問題的一種簡便、快捷的解決方案。##異步FIFO的VHDL語言實現(xiàn)

2014-05-28 10:56:41 9209

9209 大家好,又到了每日學(xué)習(xí)的時間了,今天我們來聊一聊基于FPGA的異步FIFO的實現(xiàn)。 一、FIFO簡介 FIFO是英文First In First Out 的縮寫,是一種先進(jìn)先出的數(shù)據(jù)緩存器,它與普通

2018-06-21 11:15:25 7147

7147

異步 FIFO 讀寫分別采用相互異步的不同時鐘。在現(xiàn)代集成電路芯片中,隨著設(shè)計規(guī)模的不斷擴大,一個系統(tǒng)中往往含有數(shù)個時鐘,多時鐘域帶來的一個問題就是,如何設(shè)計異步時鐘之間的接口電路。異步 FIFO

2020-07-16 17:41:46 1530

1530

FPGA芯片-XC3S50A-5TQ144C可由其他什么芯片代替?

2012-04-07 15:44:32

勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載89:FPGA片內(nèi)異步FIFO實例特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD功能概述該工程

2019-05-06 00:31:57

XC3S400A-4FTG256C 數(shù)據(jù)表 XC3S400A-4FTG256C 圖片 XC3S400A-4FTG256C 部件 XC3S400A-4FTG256C 現(xiàn)貨現(xiàn)貨型號列表XC6SLX9-2FTG256CXC3S400A-4FTG256CXC9572XL-10VQG64IXC2C256-7CPG132IXC6SLX16-2FTG256CXC9536XL-10VQG44IXC6SLX9-2TQG144CXC95144XL-10TQG100IXC9572XL-10VQG64CXC6SLX16-2CSG324CXC3S50AN-4TQG144CXC95288XL-10TQG144CXC2C128-7CPG132CXC3S50A-4VQG100IXC95144XL-10TQG144CXC3S50A-4VQG100CXC2C32A-6VQG44IXC2V500-4FG456IXC3S200AN-4FTG256CXC9572XL-10VQG44CXC3S400A-4FGG400CXCS10XL-4VQG100CXC3S250E-4PQG208CXC3S500E-4FTG256IXC6SLX4-2TQG144CXCR3032XL-10VQG44CXC3S400-4FG456CXC2V500-4FG456CXC3S50A-4FTG256IXC6SLX9-2CSG225CXC6SLX25T-2FGG484CXC2V1000-4FF896CXC6SLX45-2CSG324CXC2S100-5FGG256CXC3S50AN-4TQG144IXC9572XL-10TQG100IXCS20XL-4CSG144CXC3S1400A-4FTG256CXC3S500E-4FGG320CXC3S1400A-4FGG484IXC3S200A-4FTG256CXC2C64A-7VQG44CXC6SLX25T-2CSG324CXCF02SVOG20CXCF32PVOG48CXC2C256-7VQG100IXC6SLX16-3CSG324IXC3S400A-4FTG256IXC2C256-7TQG144IXC2C64A-7QFG48CXC7A100T-2FGG484IXC3S200A-4FTG256IXC6SLX25-2CSG324IXC6SLX45-2FGG484CXC3SD1800A-4FGG676CXC7Z015-2CLG485IXCF128XFTG64CXCR3256XL-10TQG144IXC6SLX45T-2CSG484IXC2C128-7TQG144CXC6SLX16-3FTG256CXC7A200T-1FBG676CXC3S200A-4FGG320CXC4VLX25-10FF668CXC6SLX45-3FGG676CXC6SLX45-3FGG484IXC6SLX45-3FGG484CXC6SLX9-3TQG144CXC3S400-4PQG208CXC7A50T-1FTG256IXC6SLX4-2CPG196CXC7Z020-1CLG484CXC6SLX25-3CSG324IXC6SLX45-2CSG484CXC7A50T-1FGG484CXC2S200-5FG256CXC6SLX75-2FGG484CXC3S50-4PQG208CXC4VFX60-10FFG672CXC5VSX50T-1FFG665IXC6SLX75T-3FGG676CXC3S2000-4FGG456CXC3S700A-4FGG484IXC6SLX45T-3FGG484CXC6SLX45-2CSG484IXC6SLX45-3CSG324IXC2V3000-5FG676CXC3SD1800A-4CSG484IXC9572XL-10TQ100CXC3S1400A-5FGG484CXC3S200A-4VQG100CXC6SLX150T-3FGG676IXC6SLX16-2FTG256I

2019-12-24 10:12:45

***XC3S400-4TQG144CXC5215-6HQ208CO359XC2S50-5TQG144CXC3S1000-4FG320IXC3S400-4FTG256CXC3S250E-4VQG100CXC3S

2021-10-29 13:51:34

)JANTX1N1202AJANTX2N7225W78M32VP-110BMW82M32V-12BMW3H128M72E-400SBMWF1M32B-100G2UM3

2020-06-02 11:09:42

你好,我目前正處于Spartan 3E PQ208的存儲器接口設(shè)計中。我意識到這是非常雄心勃勃的,因為我之前沒有設(shè)計過帶有FPGA的電路板,但是我目前正在研究幾個參考原理圖來幫助我完成這個過程。我

2019-05-10 13:59:37

大家好,我想在PC和FPGA之間發(fā)送和接收數(shù)據(jù)。我有XC2S200E PQ208 FPGA和CY7C68001 u***接口設(shè)備(CyPress)。有沒有人有關(guān)于這個主題的信息和例子?以上來自于谷歌

2019-05-16 14:25:20

`Xilinx FPGA入門連載55:FPGA 片內(nèi)異步FIFO實例之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能

2016-03-07 11:32:16

`Xilinx FPGA入門連載56:FPGA片內(nèi)異步FIFO實例之FIFO配置特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1新建

2016-03-09 10:49:56

): No physical part found for COMP_DEVICE_TYPE=XC3S400_1_PQFP-208_XC3S400-4PQ2, regenerate the netlist

2015-08-04 15:57:02

,當(dāng)我打開iMPACT并初始化鏈以檢測芯片時,它檢測到我的芯片是xc3s400A,而不是AN。因此,當(dāng)我嘗試編寫代碼時,自然會發(fā)生這種情況:起初我認(rèn)為我的芯片很糟糕,但后來我嘗試下載到另一個芯片

2020-05-29 14:19:59

實戰(zhàn)擴展底板(原理圖):FPGA(XC3S400-PQ208)核心板(原理圖): FPGA(EP1C6(12)-PQ240)核心板(原理圖): FPGA核心板與底板管腳對照表: 輸入模塊(4x4矩陣

2013-07-07 13:29:52

本帖最后由 630183258 于 2016-11-5 17:31 編輯

一、異步fifo的原理圖管腳定義:data輸入數(shù)據(jù)q輸出數(shù)據(jù)wrreq寫使能信號,高電平有效wrfull寫數(shù)據(jù)滿標(biāo)志位

2016-11-05 16:57:51

FIFO是FPGA處理跨時鐘和數(shù)據(jù)緩存的必要IP,可以這么說,只要是任意一個成熟的FPGA涉及,一定會涉及到FIFO。但是我在使用異步FIFO的時候,碰見幾個大坑,這里總結(jié)如下,避免后來者入坑。

2021-02-04 06:23:41

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載89:FPGA片內(nèi)異步FIFO實例特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 功能概述

2018-08-28 09:39:16

FIFO芯片是什么?如何利用FIFO去實現(xiàn)DSP間雙向并行異步通訊?

2021-06-02 06:08:17

我無法訪問WebCase網(wǎng)站。如何獲得HW-USB-II-G平臺USB II和XC3S250E-4PQG208C Spartan FPGA的波動性聲明?謝謝。以上來自于谷歌翻譯以下為原文I am

2019-04-28 13:29:42

學(xué)習(xí)fpga一段時間了,用的是EXCD-1的開發(fā)板,上面的fpga芯片是spartan-3e XC3S500E PQ208現(xiàn)在有一個實際的工程要用到fpga,我想問一下一、是用fpga開發(fā)板?二、還是用開發(fā)板上面的芯片,把芯片放到自己設(shè)計的集成電路上???

2014-12-05 10:09:09

結(jié)合高速嵌入式數(shù)據(jù)采集系統(tǒng),提出一種基于CvcloneⅢ FPGA實現(xiàn)的異步FIFO和鎖相環(huán)(PLL)結(jié)構(gòu)來實現(xiàn)高速緩存,該結(jié)構(gòu)可成倍提高數(shù)據(jù)流通速率,增加數(shù)據(jù)采集系統(tǒng)的實時性。采用FPGA設(shè)計高速緩存,能針對外部硬件系統(tǒng)的改變,通過修改片內(nèi)程序以應(yīng)用于不同的硬件環(huán)境。

2021-04-30 06:19:52

FIFO的基本結(jié)構(gòu)和工作原理異步FIFO設(shè)計中的問題與解決辦法FPGA內(nèi)部軟異步FIFO設(shè)計

2021-04-08 07:07:45

親愛的,我想用spartan3 xc3s400pq208 DCM動態(tài)部分重新配置使用基于差異的技術(shù).......我只有ise9.2i .....可以任何身體指導(dǎo)我........以上來自于谷歌翻譯

2018-10-08 17:40:42

的約束。我們將開發(fā)板價格鎖定在100元以內(nèi),那么有幾款價格比較突出的型號、ALTERA的cy2c5Q208c,37元;xc3s400-4pq208c 59元,xc3s50an 26元。找個支付寶號或者

2012-09-19 13:25:27

哥們,當(dāng)XC3S400AN處于通電狀態(tài)時,重置XC3S400AN的DCM_SP。 DCM_SP會進(jìn)入默認(rèn)狀態(tài)嗎?在spartan3a_hdl.pdf的第30頁上,有一個RST用法的說明。 - “異步

2019-08-07 10:18:32

150MHz)。第一個原型被設(shè)計為Spartan-3E Starter-Kit的擴展,現(xiàn)在我正在設(shè)計完整的系統(tǒng)。不幸的是我必須使用PQ208封裝,因為我們無法焊接BGA封裝。 PCB只有兩層銅層(頂部/底部

2019-06-20 11:54:46

誰會spartan3 xc3s400 bit文件轉(zhuǎn)mcs文件!

2012-06-14 10:30:13

首先介紹異步FIFO 的概念、應(yīng)用及其結(jié)構(gòu),然后分析實現(xiàn)異步FIFO的難點問題及其解決辦法; 在傳統(tǒng)設(shè)計的基礎(chǔ)上提出一種新穎的電路結(jié)構(gòu)并對其進(jìn)行綜合仿真和FPGA 實現(xiàn)。

2009-04-16 09:25:29 46

46 文章介紹了基于FPGA 和數(shù)字頻率合成技術(shù),利用VHDL 編制程序并下載至Xilinx 公司的SpartanⅡ系列XC2S100E-6PQ208 FPAG 芯片上,加以簡單的外圍電路,構(gòu)成了高精度數(shù)字式移相正弦波信號發(fā)生

2009-08-29 08:57:52 43

43 介紹了PCI 9054 接口芯片的性能及數(shù)據(jù)傳輸特點,提出了一種基于PCI 9054 外擴異步FIFO(先進(jìn)先出)的FPGA(現(xiàn)場可編程門陣列)實現(xiàn)方法。由于PCI 9054 內(nèi)部FIFO存儲器主要用于數(shù)據(jù)

2010-01-06 15:20:10 44

44 本文主要研究了用FPGA 芯片內(nèi)部的EBRSRAM 來實現(xiàn)異步FIFO 設(shè)計方案,重點闡述了異步FIFO 的標(biāo)志信號——空/滿狀態(tài)的設(shè)計思路,并且用VHDL 語言實現(xiàn),最后進(jìn)行了仿真驗證。

2010-01-13 17:11:58 40

40 A42MX16-PQ208I產(chǎn)品詳情Microsemis 40MX 和 42MX 系列在 5V 電壓下提供具有成本效益的設(shè)計解決方案。MX 器件是單芯片解決方案,在提供高性能的同時縮短了系統(tǒng)

2023-06-16 13:14:55

IDS1-XC3S400開發(fā)板用戶手冊

IDS1系列開發(fā)板主要是基于XILINX SPARTAN3 系列FPGA設(shè)計開發(fā)的入門級開發(fā)板。該系

2010-04-14 11:28:12 85

85 給出了一個利用格雷碼對地址編碼的羿步FIFO 的實現(xiàn)方法,并給出了VHDL 程序,以解決異步讀寫時鐘引起的問題。

2010-07-16 15:15:42 26

26 介紹了異步FIFO在Camera Link接口中的應(yīng)用,將Camera Link接口中的幀有效信號FVAL和行有效信號LVAL引入到異步FIFO的設(shè)計中。分析了FPGA中設(shè)計異步FIFO的難點,解決了異步FIFO設(shè)計中存在的兩

2010-07-28 16:08:06 32

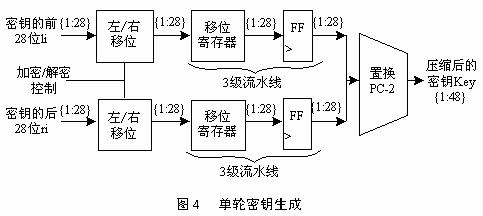

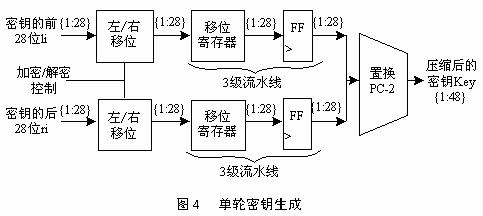

32 摘要:介紹3-DES算法的概要;以Xilinx公司SPARTANII結(jié)構(gòu)的XC2S100為例,闡述用FPGA高速實現(xiàn)3-DES算法的設(shè)計要點及關(guān)鍵部分的設(shè)計。引 言

2006-03-13 19:36:42 1016

1016

摘要:首先介紹異步FIFO的概念、應(yīng)用及其結(jié)構(gòu),然后分析實現(xiàn)異步FIFO的難點問題及其解決辦法;在傳統(tǒng)設(shè)計的基礎(chǔ)上提出一種新穎的電路結(jié)構(gòu)并對其進(jìn)行

2009-06-20 12:46:50 4131

4131

摘要:介紹3-DES算法的概要;以Xilinx公司SPARTANII結(jié)構(gòu)的XC2S100為例,闡述用FPGA高速實現(xiàn)3-DES算法的設(shè)計要點及關(guān)鍵部分的設(shè)計。

關(guān)鍵詞:3-DES

2009-06-20 14:22:00 1600

1600

高速異步FIFO的設(shè)計與實現(xiàn)

引言

現(xiàn)代集成電路芯片中,隨著設(shè)計規(guī)模的不斷擴大.一個系統(tǒng)中往往含有數(shù)個時鐘。多時鐘帶來的一個問題就是,如何設(shè)

2010-04-12 15:13:08 3176

3176

1 FIFO概述

FIFO芯片是一種具有存儲功能的高速邏輯芯片,可在高速數(shù)字系統(tǒng)中用作數(shù)據(jù)緩存。FIFO通常利用雙口RAM和讀寫地址產(chǎn)生模塊來實現(xiàn)其功能。FIFO的接口信號包括異步

2010-08-06 10:22:04 5678

5678

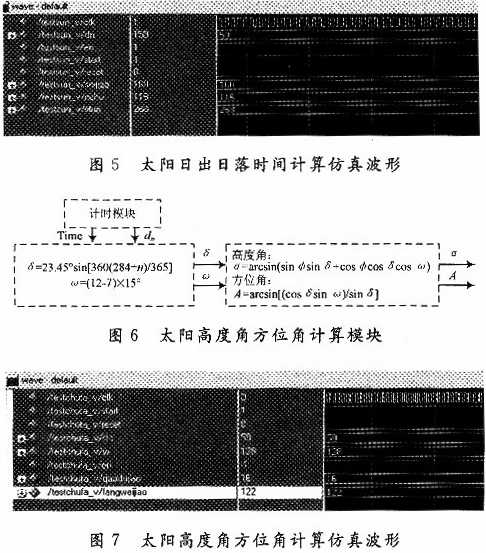

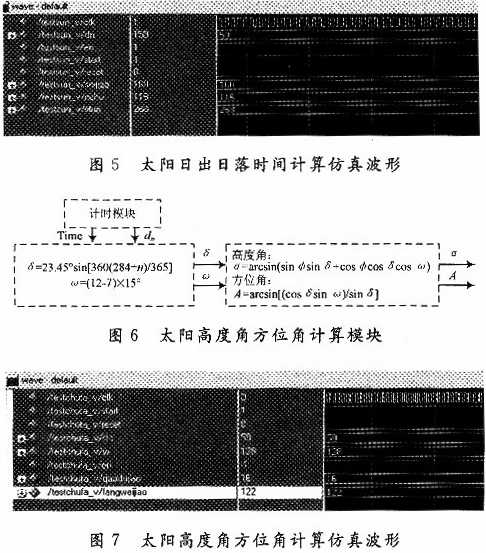

本設(shè)計采用傳統(tǒng)的視日運動跟蹤法,利用Xilinx公司提供的FPGA開發(fā)環(huán)境ISE,設(shè)計完成了基于XC3S1500開發(fā)板的

2010-09-29 09:42:21 1432

1432

摘要:數(shù)字視頻信號處理涉及對高速實時視頻信號的傳輸和處理,要求相關(guān)電路系統(tǒng)具有強大的數(shù)據(jù)處理能力。介紹一種以DSP和FPGA器件為核心構(gòu)建的場發(fā)射平板顯示器視頻信號處理系統(tǒng)方案,并以,11公司的DSP芯片TMS320C6713和Xilinx公司的FPGA芯片XC3S200一PQ208

2011-02-25 16:39:19 53

53 根據(jù)工業(yè)應(yīng)用的實際需要以及網(wǎng)絡(luò)通信發(fā)展的功能要求,提出了基于FPGA智能變送器控制系統(tǒng)的總體方案, 設(shè)計了以XILINX公司的Spartan3系列XC3S4005PQ208C可編程邏輯器件為主控制器、DM9000

2011-04-12 17:15:15 74

74 為了解決基于LabVIEWFPGA模塊的DMAFIFO深度設(shè)定不當(dāng)帶來的數(shù)據(jù)不連續(xù)問題,結(jié)合LabVIEWFPGA的編程特點和DMA FIFO的工作原理,提出了一種設(shè)定 FIFO 深度的方法。對FIFO不同深度的實驗表明,采

2011-09-26 13:45:17 7987

7987

文中給出了異步FIFO的實現(xiàn)代碼和FPGA與DSP的硬件連接電路。經(jīng)驗證,利用異步FIFO的方法,在FPGA與DSP通信中的應(yīng)用,具有傳輸速度快、穩(wěn)定可靠、實現(xiàn)方便的優(yōu)點。

2011-12-12 14:28:22 51

51 為實現(xiàn)目標(biāo)識別與跟蹤的應(yīng)用目的 ,在基于 TMS320DM642 的 FIFO 基礎(chǔ)上擴展存儲空間 ,提出一種基于

FPGA實現(xiàn) SDRAM 控制器的方法。分析所用 SDRAM 的特點和工作原理

2015-10-29 14:05:57 2

2 異步FIFO結(jié)構(gòu)及FPGA設(shè)計,解決亞穩(wěn)態(tài)的問題

2015-11-10 15:21:37 4

4 NBP13 Xilinx CoolRunner-II PQ208 Rev1.01

2016-02-17 14:51:49 0

0 NBP15 Xilinx XC9500XL XC9500XV PQ208 Rev1.01

2016-02-17 14:54:14 0

0 NBP16 Xilinx Spartan-II PQ208 Rev1.01

2016-02-17 15:04:39 0

0 NBP14 Xilinx CoolRunner PQ208 Rev1.01

2016-02-17 15:05:24 0

0 NBP1 Xilinx Spartan-IIE PQ208 Rev1.02

2016-02-17 15:05:45 0

0 NBP2 Altera Cyclone PQ208 Rev1.02

2016-02-17 15:06:04 0

0 NBP5 Actel ProASIC Plus PQ208 Rev1.01

2016-02-17 15:07:40 0

0 異步FIFO在FPGA與DSP通信中的運用

2016-05-19 11:17:11 0

0 基于Xilinx XC3S500E的FPGA最小開發(fā)板制作

2016-06-21 16:50:39 56

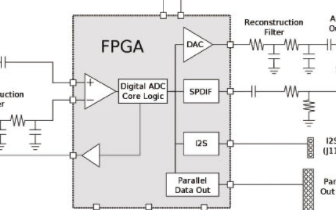

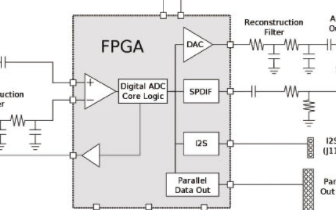

56 XC3S400AN_數(shù)字ADC音頻

2017-09-30 10:00:52 9

9 基于異步FIFO在FPGA與DSP通信中的運用

2017-10-19 10:30:56 10

10 摘要 利用異步FIFO實現(xiàn)FPGA與DSP進(jìn)行數(shù)據(jù)通信的方案。FPGA在寫時鐘的控制下將數(shù)據(jù)寫入FIFO,再與DSP進(jìn)行握手后,DSP通過EMIFA接口將數(shù)據(jù)讀入。文中給出了異步FIFO的實現(xiàn)

2017-10-30 11:48:44 3

3 本文首先對異步 FIFO 設(shè)計的重點難點進(jìn)行分析,最后給出詳細(xì)代碼。 一、FIFO簡單講解 FIFO的本質(zhì)是RAM, 先進(jìn)先出 重要參數(shù):fifo深度(簡單來說就是需要存多少個數(shù)據(jù)) fifo位寬

2017-11-15 12:52:41 9176

9176

介紹了一個基于FPGA的多通道信號采集電路。該電路以FPGA 芯片XC3S400 作為電路的主控制器,采用電子開關(guān)ADG708對7路信號進(jìn)行了循環(huán)采集,使用AD7667 作為模數(shù)轉(zhuǎn)換器,由主控

2017-11-18 10:40:01 3292

3292

設(shè)計,詳述了各子模塊的設(shè)計思路和方法,給出了它們的仿真時序圖。綜合實現(xiàn)后,將程序下載到FPGA芯片中,運行正確無誤。又經(jīng)長時間發(fā)送和接收測試,運行穩(wěn)定可靠。

2017-11-18 11:33:01 6257

6257 在現(xiàn)代電路設(shè)計中,一個系統(tǒng)往往包含了多個時鐘,如何在異步時鐘間傳遞數(shù)據(jù)成為一個很重要的問題,而使用異步FIFO可以有效地解決這個問題。異步FIFO是一種在電子系統(tǒng)中得到廣泛應(yīng)用的器件,文中介紹了一種基于FPGA的異步FIFO設(shè)計方法。使用這種方法可以設(shè)計出高速、高可靠的異步FIFO。

2018-07-17 08:33:00 8860

8860

在現(xiàn)代的集成電路芯片中,隨著設(shè)計規(guī)模的不斷擴大,一個系統(tǒng)中往往含有數(shù)個時鐘。多時鐘域帶來的一個問題就是,如何設(shè)計異步時鐘之間的接口電路。異步FIFO(Firstln F irsto ut)是解決這個

2018-02-07 14:22:54 0

0 ?XC2S100-5PQG208C 這個用在音頻解碼器上面,是直接用,還是要先寫進(jìn)程序再用

2018-03-09 18:16:32 454

454 異步FIFO(Fist-In-First-Out)是一種先入先出的數(shù)據(jù)緩沖器[1]。由于可以很好地解決跨時鐘域問題和不同模塊之間的速度匹配問題,而被廣泛應(yīng)用于全局異步局部同步[2](Globally

2018-06-19 15:34:00 3780

3780

異步FIFO廣泛應(yīng)用于計算機網(wǎng)絡(luò)工業(yè)中進(jìn)行異步數(shù)據(jù)傳送,這里的異步是指發(fā)送用一種速率而接收用另一速率,因此異步FIFO有兩個不同的時鐘,一個為讀同步時鐘,一個為寫同步時鐘。

2019-06-11 08:00:00 3853

3853

為了解決基于LabVIEWFPGA模塊的DMAFIFO深度設(shè)定不當(dāng)帶來的數(shù)據(jù)不連續(xù)問題,結(jié)合LabVIEWFPGA的編程特點和DMA FIFO的工作原理,提出了一種設(shè)定FIFO深度的方法。對FIFO

2019-01-04 14:25:07 5203

5203

本通知的目的是告知Xilinx將停止生產(chǎn)汽車(XA)Spartan?-3/-3e FPGA PQ(G)208包裝產(chǎn)品。本產(chǎn)品停產(chǎn)通知單(PDN)適用于汽車(Q)和(I)溫度等級產(chǎn)品。

2019-02-14 16:19:10 3

3 根據(jù)FIFO工作的時鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時鐘和寫時鐘為同一個時鐘。在時鐘沿來臨時同時發(fā)生讀寫操作。異步FIFO是指讀寫時鐘不一致,讀寫時鐘是互相獨立的。

2019-11-29 07:08:00 2265

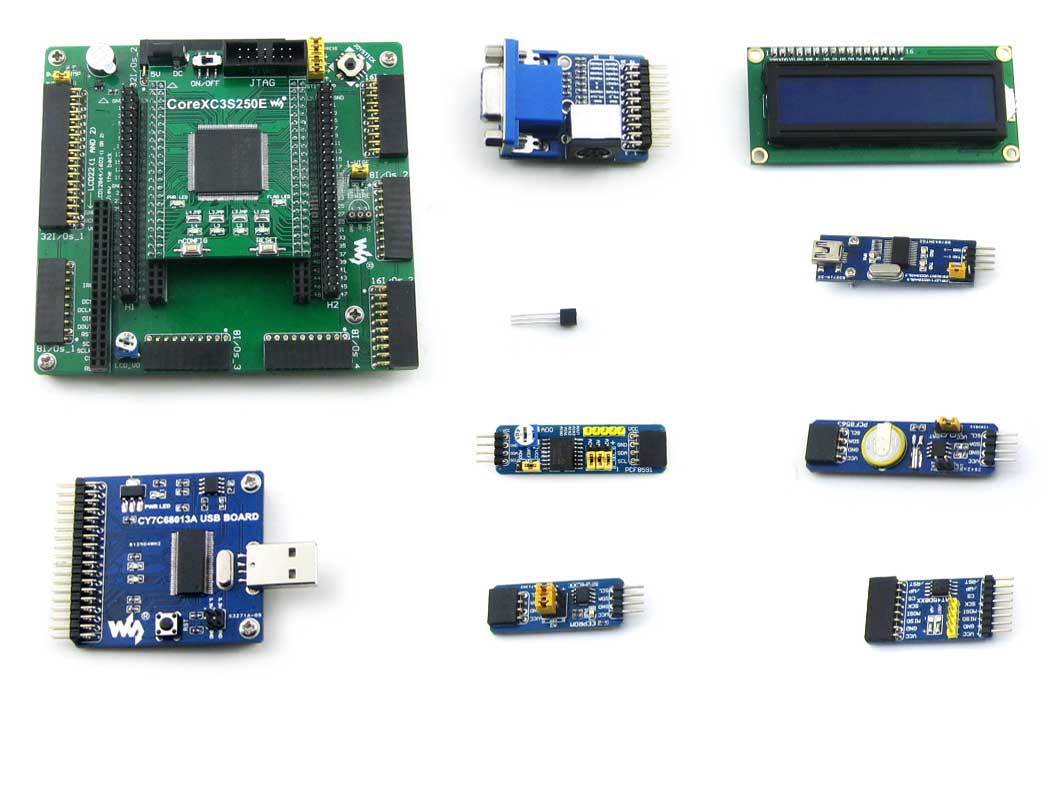

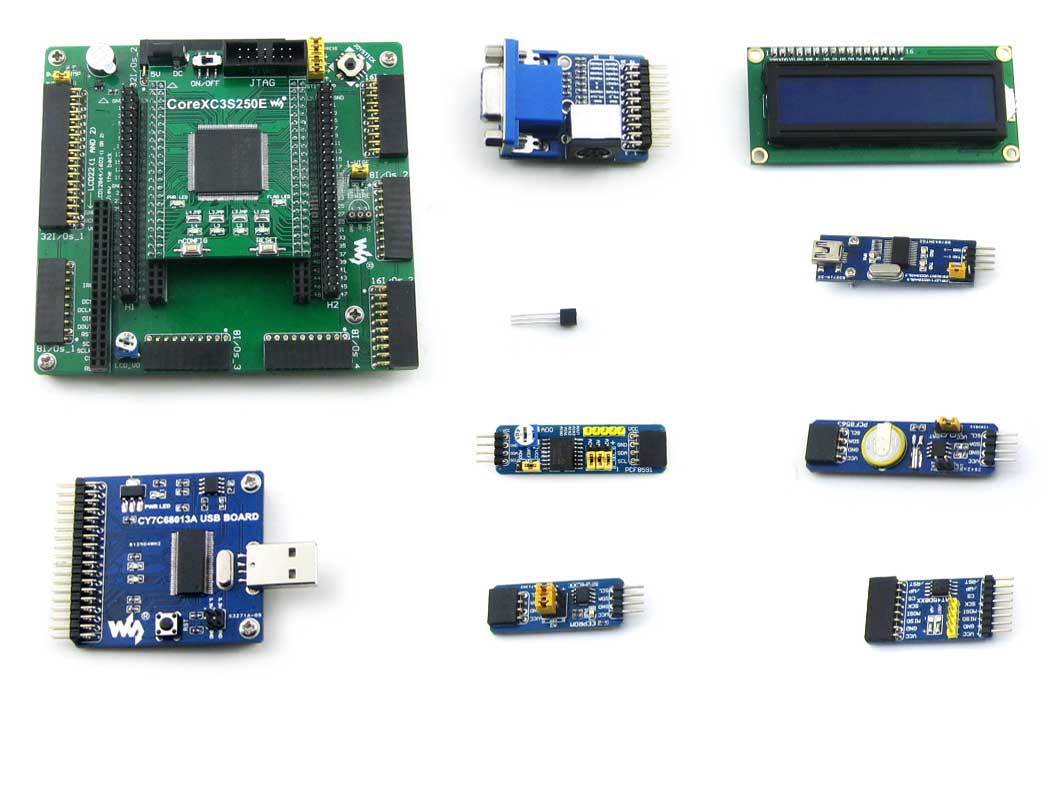

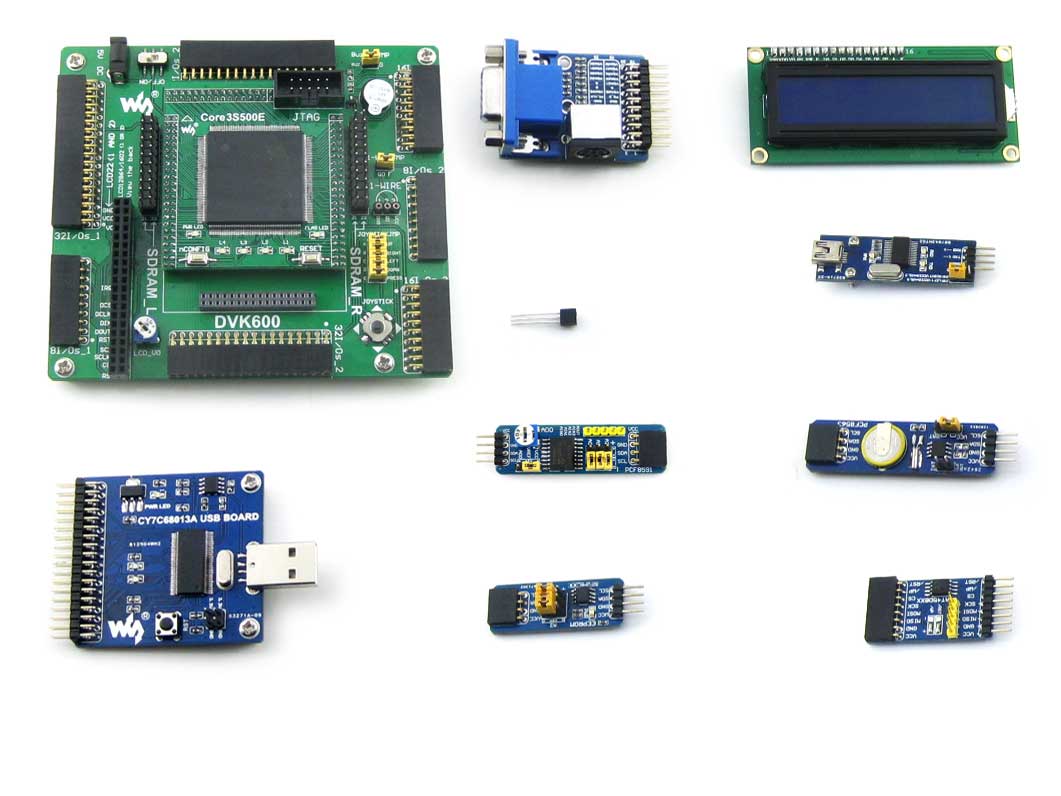

2265 XC3S250E 開發(fā)板 學(xué)習(xí)板 套餐A 含8款模塊

引出常用接口,含LCD、串口、按鍵、USB通信等模塊

型號 Open3S250E (套餐A)

2019-12-23 13:55:34 2507

2507

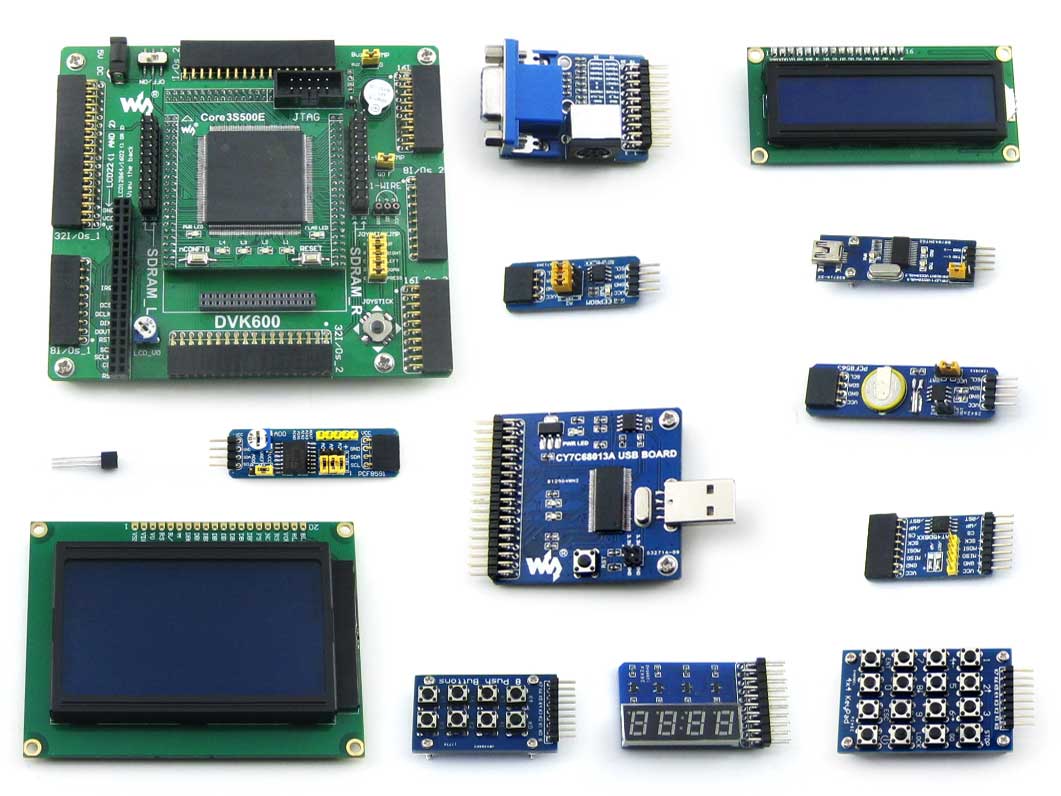

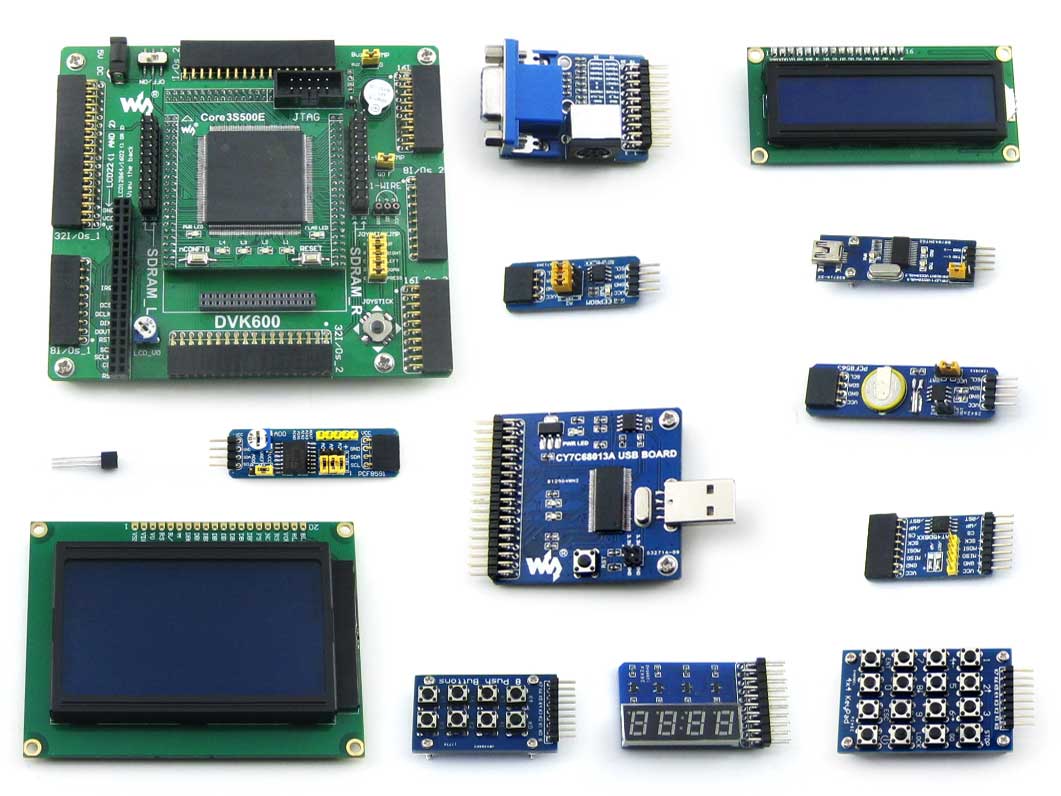

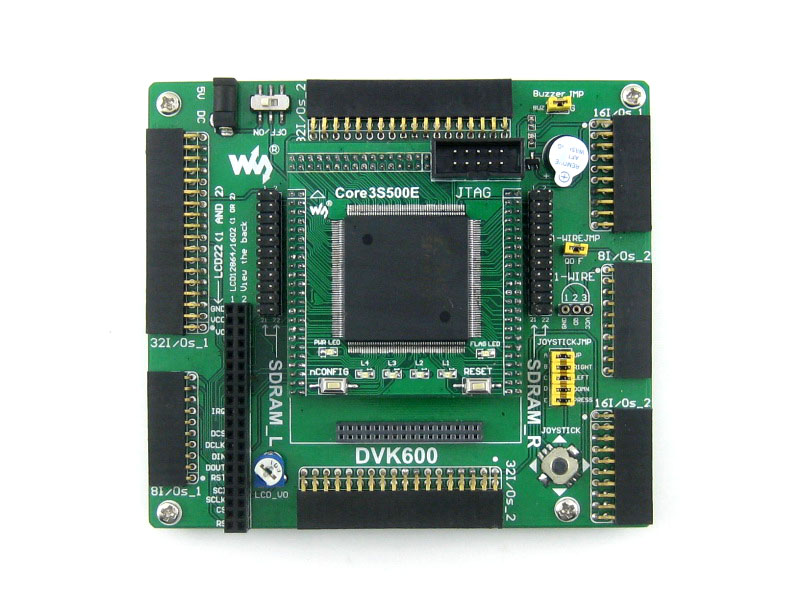

XC3S500E 開發(fā)板 學(xué)習(xí)板 套餐B 含12款模塊

引出常用接口,含LCD、串口、按鍵、USB通信等模塊

型號 Open3S500E (套餐B)

2019-12-23 14:24:19 3224

3224

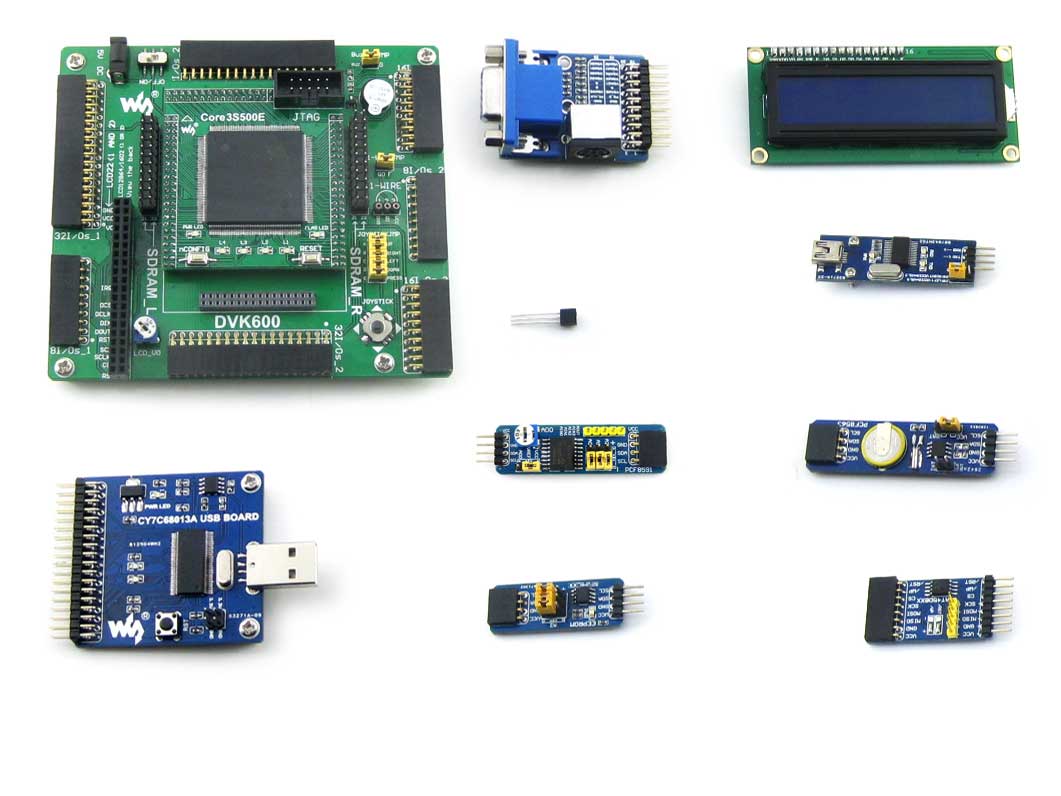

XC3S500E 開發(fā)板 學(xué)習(xí)板 套餐A 含8款模塊

引出常用接口,含LCD、串口、按鍵、USB通信等模塊

型號 Open3S500E (套餐A)

2019-12-23 14:29:29 2268

2268

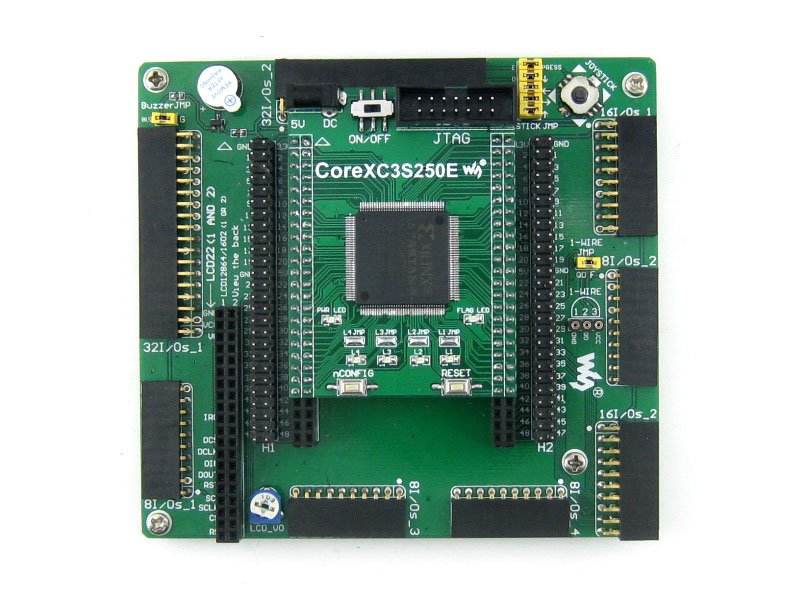

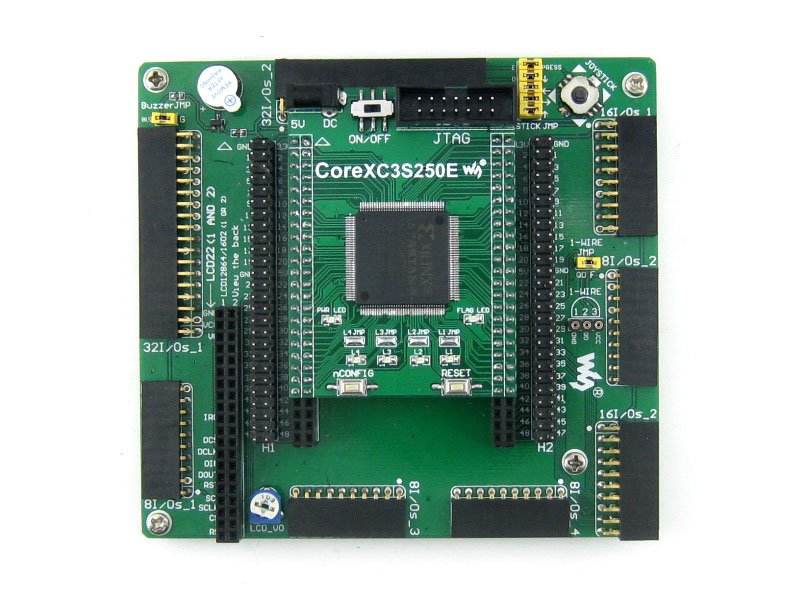

FPGA開發(fā)板Open3S250E是一塊以 Spartan-3E XC3S250E為主控芯片的開發(fā)板,它帶有豐富的擴展接口,支持各類外圍模塊的接入。 底板資源簡介 [ 核心接口簡介 ] 核心板插槽 方便

2019-12-23 14:36:47 4311

4311

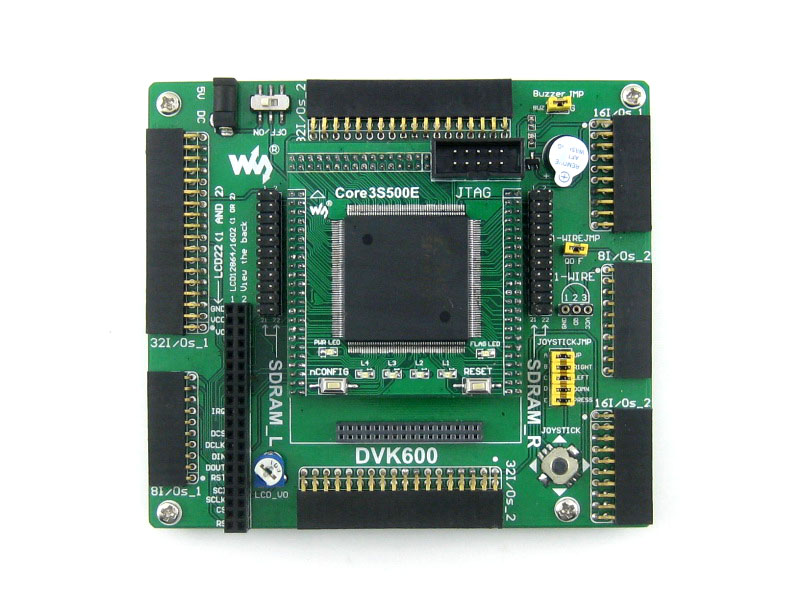

XC3S500E 開發(fā)板 學(xué)習(xí)板 核心板 標(biāo)準(zhǔn)版本

引出常用接口,可接微雪外圍模塊

型號 Open3S500E (標(biāo)準(zhǔn)版)

2019-12-23 14:40:21 3113

3113

。本文提出了一種用Xilinx公司的FPGA芯片實現(xiàn)異步HFO的設(shè)計方案,重點強調(diào)了設(shè)計有效、可靠的握手信號EMPTY與FULL的方法,并給出了其VERILOG語言實現(xiàn)的仿真圖。

2021-01-15 15:27:00 9

9 提出了一種節(jié)能并可升級的異步FIFO的FPGA實現(xiàn)。此系統(tǒng)結(jié)構(gòu)利用FPGA內(nèi)自身的資源控制時鐘的暫停與恢復(fù),實現(xiàn)了高能效、高工作頻率的數(shù)據(jù)傳輸。該系統(tǒng)在Xilinx的VC4VSX55芯片中實現(xiàn),實際

2021-02-02 15:15:00 16

16 FIFO是FPGA處理跨時鐘和數(shù)據(jù)緩存的必要IP,可以這么說,只要是任意一個成熟的FPGA涉及,一定會涉及到FIFO。但是我在使用異步FIFO的時候,碰見幾個大坑,這里總結(jié)如下,避免后來者入坑。

2021-03-12 06:01:34 12

12 一:fifo是什么 FIFO的完整英文拼寫為FirstIn First Out,即先進(jìn)先出。FPGA或者ASIC中使用到的FIFO一般指的是對數(shù)據(jù)的存儲具有先進(jìn)先出特性的一個存儲器,常被用于數(shù)據(jù)

2021-03-12 16:30:48 4047

4047

Stellamar公司的數(shù)字ADC采用Xilinx公司的XC3S400AN FPGA,平均功耗低50%,面積低50%,非常低的工作電壓。高達(dá)14位的有效位,14位500Hz的SNR為90dB,數(shù)字

2021-03-18 15:57:34 4204

4204

FPGA_ASIC-S698MSoC芯片中EDAC模塊的設(shè)計與實現(xiàn)(第四屆星載電源技術(shù)學(xué)術(shù)研討會)-該文檔為FPGA_ASIC-S698MSoC芯片中EDAC模塊的設(shè)計與實現(xiàn)總結(jié)文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-09-15 11:05:19 6

6 一、概述 在大規(guī)模ASIC或FPGA設(shè)計中,多時鐘系統(tǒng)往往是不可避免的,這樣就產(chǎn)生了不同時鐘域數(shù)據(jù)傳輸?shù)膯栴},其中一個比較好的解決方案就是使用異步FIFO來作不同時鐘域數(shù)據(jù)傳輸?shù)木彌_區(qū),這樣既可以

2021-09-30 09:57:40 2382

2382

在大規(guī)模ASIC或FPGA設(shè)計中,多時鐘系統(tǒng)往往是不可避免的,這樣就產(chǎn)生了不同時鐘域數(shù)據(jù)傳輸?shù)膯栴},其中一個比較好的解決方案就是使用異步FIFO來作不同時鐘域數(shù)據(jù)傳輸?shù)木彌_區(qū),這樣既可以使相異時鐘域數(shù)據(jù)傳輸?shù)臅r序要求變得寬松,也提高了它們之間的傳輸效率。此文內(nèi)容就是闡述異步FIFO的設(shè)計。

2022-03-09 16:29:18 3457

3457 無論何時,在復(fù)雜的 FPGA 設(shè)計過程中,都不可避免地需要在模塊之間發(fā)送數(shù)據(jù),實現(xiàn)這一點的常用的是 FIFO。

2022-09-20 09:10:27 3532

3532 同步FIFO的意思是說FIFO的讀寫時鐘是同一個時鐘,不同于異步FIFO,異步FIFO的讀寫時鐘是完全異步的。同步FIFO的對外接口包括時鐘,清零,讀請求,寫請求,數(shù)據(jù)輸入總線,數(shù)據(jù)輸出總線,空以及滿信號。

2022-11-01 09:58:16 2461

2461 異步fifo詳解 一. 什么是異步FIFO FIFO即First in First out的英文簡稱,是一種先進(jìn)先出的數(shù)據(jù)緩存器,與普通存儲器的區(qū)別在于沒有外部讀寫的地址線,缺點是只能順序的讀取

2022-12-12 14:17:41 5421

5421 異步FIFO主要由五部分組成:寫控制端、讀控制端、FIFO Memory和兩個時鐘同步端

2023-05-26 16:17:20 2201

2201

簡單的一種,其特點是輸入和輸出都與時鐘信號同步,當(dāng)時鐘到來時,數(shù)據(jù)總是處于穩(wěn)定狀態(tài),因此容易實現(xiàn)數(shù)據(jù)的傳輸和存儲。 而異步FIFO則是在波形的上升沿和下降沿上進(jìn)行處理,在輸入輸出端口處分別增加輸入和輸出指針,用于管理數(shù)據(jù)的讀寫。異步FIFO的輸入和輸出可同時進(jìn)行,中間可以

2023-10-18 15:23:58 2603

2603 ? 點擊上方 藍(lán)字 關(guān)注我們 ? 第一節(jié):fifo基礎(chǔ) ? ? 內(nèi)容: 1. 掌握FPGA設(shè)計中關(guān)于數(shù)據(jù)緩存的使用 2. 掌握FIFO工作原理

2023-11-17 14:00:02 1219

1219

電子發(fā)燒友App

電子發(fā)燒友App

評論