大家好,又到了每日學(xué)習(xí)的時(shí)間了,今天我們來(lái)聊一聊基于FPGA的異步FIFO的實(shí)現(xiàn)。 一、FIFO簡(jiǎn)介 FIFO是英文First In First Out 的縮寫(xiě),是一種先進(jìn)先出的數(shù)據(jù)緩存器,它與普通

2018-06-21 11:15:25 7149

7149

是這個(gè)問(wèn)題的一種簡(jiǎn)便、快捷的解決方案,使用異步 FIFO 可以在兩個(gè)不同時(shí)鐘系統(tǒng)之間快速而方便地傳輸實(shí)時(shí)數(shù)據(jù)。

2020-07-16 17:41:46 1530

1530

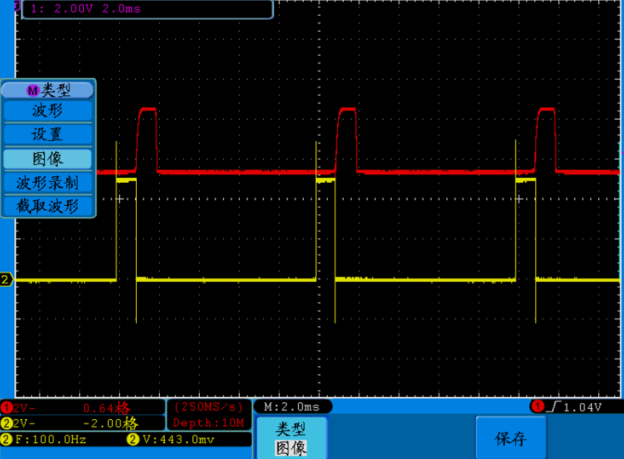

實(shí)例內(nèi)部系統(tǒng)功能框圖如圖9.72所示。我們通過(guò)IP核例化一個(gè)異步FIFO,定時(shí)寫(xiě)入數(shù)據(jù),然后再讀出所有數(shù)據(jù)。通過(guò)QuartusII集成的在線邏輯分析儀SignalTap II,我們可以觀察FPGA片內(nèi)

2019-05-06 00:31:57

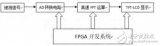

集成了常用IP核,使之可以靈活的用來(lái)進(jìn)行系統(tǒng)設(shè)計(jì)。在單片FPGA芯片上實(shí)現(xiàn)導(dǎo)航信息的高速解算,將會(huì)有廣闊的發(fā)展空間。針對(duì)現(xiàn)有小型無(wú)人機(jī)導(dǎo)航解算系統(tǒng)解算速度慢、多處理器臃腫可靠性差的缺點(diǎn),文中設(shè)計(jì)了一種

2019-07-03 06:57:34

摘要:為了實(shí)現(xiàn)對(duì)非相干雷達(dá)的接收相參處理,基于數(shù)字穩(wěn)定校正(DSU)的原理,采用ALTERA公司的StratixⅡ系列芯片和VHDL編程語(yǔ)言,設(shè)計(jì)了一種基于FPGA的DSU硬件實(shí)現(xiàn)方法。實(shí)驗(yàn)結(jié)果表明

2019-06-28 08:27:33

摘要:UART作為RS232協(xié)議的控制接口得到了廣泛的應(yīng)用,將UART的功能集成在FPGA芯片中,可使整個(gè)系統(tǒng)更為靈活、緊湊,減小整個(gè)電路的體積,提高系統(tǒng)的可靠性和穩(wěn)定性。提出了一種基于FPGA

2019-06-21 07:17:24

中,數(shù)字信號(hào)處理系統(tǒng)經(jīng)常要進(jìn)行高速、高精度的FFF運(yùn)算。現(xiàn)場(chǎng)可編程邏輯陣列(FPGA)是一種可定制集成電路,具有面向數(shù)字信號(hào)處理算法的物理結(jié)構(gòu)。用FPGA實(shí)現(xiàn)FFT處理器具有硬件系統(tǒng)簡(jiǎn)單、功耗低的優(yōu)點(diǎn)

2019-07-03 07:56:53

,影響系統(tǒng)可靠性,要進(jìn)一步提高系統(tǒng)實(shí)時(shí)性,必須研究開(kāi)發(fā)高速嵌入式雷達(dá)信號(hào)采集系統(tǒng)。這里結(jié)合高速嵌入式數(shù)據(jù)采集系統(tǒng),提出一種基于CvcloneⅢFPGA實(shí)現(xiàn)的異步FIFO和鎖相環(huán)(PLL)結(jié)構(gòu)來(lái)實(shí)現(xiàn)

2019-08-21 06:56:32

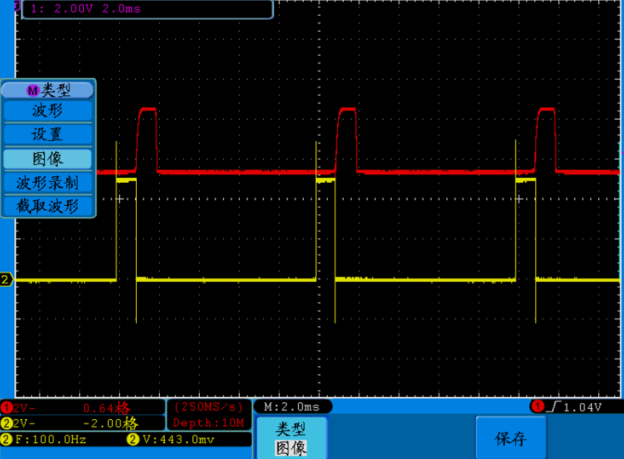

也就是說(shuō)用一個(gè)25M頻率的FIFO寫(xiě)入數(shù)據(jù),用另一個(gè)100M(或者不同頻)的FIFO讀出數(shù)據(jù)。該如何實(shí)現(xiàn)呢?不使用異步FIFO

2020-12-03 20:47:22

本文概述了開(kāi)發(fā)這種系統(tǒng)所必須面對(duì)的各種設(shè)計(jì)挑戰(zhàn),并講解了Altium公司的最新電子設(shè)計(jì)環(huán)境Nexar如何為FPGA設(shè)計(jì)提供一種全新的方法。這種方法不僅可將處理器有效地集成入FPGA之中,而且成為一種挖掘現(xiàn)有以及未來(lái)大容量、低成本FPGA部件應(yīng)用潛力的系統(tǒng)級(jí)

2021-05-08 06:02:24

):https://bbs.elecfans.com/jishu_948330_1_1.html,主要甚至區(qū)別在于第一步,異步fifo設(shè)置方法如下圖。圖(1)三、仿真及分析altera的fifo在讀

2016-11-05 16:57:51

本文介紹了一種在DSP平臺(tái)下對(duì)多路交流信號(hào)采樣時(shí)采用的一種異步采樣方法。

2021-04-02 07:01:30

引 言在高速的數(shù)據(jù)采集或傳輸中,目前使用較多的都是采用USB 2.0接口控制器和FPGA或DSP實(shí)現(xiàn)的,本設(shè)計(jì)在USB 2.0接口芯片CY7C68013的Slave FIFO模式下,利用FPGA作為

2021-06-24 07:00:00

一種FPGA與DSP的高速通信接口設(shè)計(jì)與實(shí)現(xiàn)方案

2021-06-02 06:07:16

FPGA芯片是由哪些部分組成的?如何去實(shí)現(xiàn)一種基于FPGA芯片的可重構(gòu)數(shù)字電路設(shè)計(jì)?

2021-11-05 08:38:57

一種基于VxWorks的多路高速串口的通信方法設(shè)計(jì)

2021-06-03 06:36:54

ASIC系統(tǒng)。 使用USB協(xié)議棧知識(shí)產(chǎn)權(quán)(IP)及外部收發(fā)器 在第一種方法中,我們可以在FPGA或ASIC中實(shí)現(xiàn)SIE(見(jiàn)圖3)。圖3 FPGA + USB協(xié)議棧IP + USB收發(fā)器 SIE IP

2012-11-22 16:11:20

通過(guò)對(duì)FPGA芯片內(nèi)部EBRSRAM的深入研究,提出了一種利用格雷碼對(duì)地址進(jìn)行編碼的異步FIFO設(shè)計(jì)方案。

2021-04-13 06:41:03

結(jié)合高速嵌入式數(shù)據(jù)采集系統(tǒng),提出一種基于CvcloneⅢ FPGA實(shí)現(xiàn)的異步FIFO和鎖相環(huán)(PLL)結(jié)構(gòu)來(lái)實(shí)現(xiàn)高速緩存,該結(jié)構(gòu)可成倍提高數(shù)據(jù)流通速率,增加數(shù)據(jù)采集系統(tǒng)的實(shí)時(shí)性。采用FPGA設(shè)計(jì)高速緩存,能針對(duì)外部硬件系統(tǒng)的改變,通過(guò)修改片內(nèi)程序以應(yīng)用于不同的硬件環(huán)境。

2021-04-30 06:19:52

FIFO的基本結(jié)構(gòu)和工作原理異步FIFO設(shè)計(jì)中的問(wèn)題與解決辦法FPGA內(nèi)部軟異步FIFO設(shè)計(jì)

2021-04-08 07:07:45

我用GPIF作為一個(gè)32位奴隸FIFO與2位尋址。我想知道是否有一種方法來(lái)確定GPIF接口在等待GPIF主機(jī)的數(shù)據(jù)時(shí)“干”還是空。 以上來(lái)自于百度翻譯 以下為原文I am using

2019-05-27 14:25:13

有沒(méi)有一種方法直接從芯片上讀取27443的程序?

2019-09-17 13:45:00

本文介紹了一種基于FPGA芯片的高速智能節(jié)點(diǎn)的硬件結(jié)構(gòu)和軟件設(shè)計(jì),旨在提高現(xiàn)在LON網(wǎng)絡(luò)的智能節(jié)點(diǎn)的處理能力和通用性。

2021-05-06 08:20:28

本文研究設(shè)計(jì)了一種基于高速隔離芯片的高速串行隔離型ADC。該數(shù)字隔離型ADC頻帶寬,延時(shí)小,穩(wěn)定性高并且電路結(jié)構(gòu)簡(jiǎn)單。利用FPGA作為控制器,很好地實(shí)現(xiàn)了模數(shù)轉(zhuǎn)換和隔離傳輸。

2021-05-08 06:14:31

求大佬分享一種基于FPGA的OLED真彩色動(dòng)態(tài)圖像顯示的實(shí)現(xiàn)方法

2021-06-01 06:38:14

求大神分享一種高速突發(fā)模式誤碼測(cè)試儀的FPGA實(shí)現(xiàn)方案

2021-04-29 06:58:18

我有一個(gè)應(yīng)用程序可能會(huì)更好用一個(gè)真正的,沒(méi)有時(shí)鐘的異步fifo,對(duì)于年輕人的說(shuō)服力,這是一種想法,但不需要這個(gè)尺寸。http://www.ti.com/lit/ds/symlink

2019-04-23 13:44:46

本文討論了在ASIC設(shè)計(jì)中數(shù)據(jù)在不同時(shí)鐘之間傳遞數(shù)據(jù)所產(chǎn)生的亞穩(wěn)態(tài)問(wèn)題,并提出了一種新的異步FIFO的設(shè)計(jì)方法,并用VHDL語(yǔ)言進(jìn)行描述,利用Altera公司的Cyclone系列的EP1C6進(jìn)行硬件實(shí)現(xiàn),該電路軟件仿真和硬件實(shí)現(xiàn)已經(jīng)通過(guò)驗(yàn)證,并應(yīng)用到各種電路中。

2021-04-29 06:54:00

為什么要設(shè)計(jì)一種異步FIFO?異步FIFO的設(shè)計(jì)原理是什么?怎樣去設(shè)計(jì)一種異步FIFO?

2021-06-18 09:20:29

可以實(shí)現(xiàn)單片機(jī)系統(tǒng)接入因特網(wǎng):一種方法是利用NIC (網(wǎng)絡(luò)控制/網(wǎng)卡)實(shí)現(xiàn)網(wǎng)絡(luò)接口,由單片機(jī)來(lái)提供所需的網(wǎng)絡(luò)協(xié)議;另外一種方法是利用具有網(wǎng)絡(luò)協(xié)議棧結(jié)構(gòu)的芯片和PHY(物理層的接收器)來(lái)實(shí)現(xiàn)網(wǎng)絡(luò)接口,主控

2019-04-30 07:00:16

首先介紹異步FIFO 的概念、應(yīng)用及其結(jié)構(gòu),然后分析實(shí)現(xiàn)異步FIFO的難點(diǎn)問(wèn)題及其解決辦法; 在傳統(tǒng)設(shè)計(jì)的基礎(chǔ)上提出一種新穎的電路結(jié)構(gòu)并對(duì)其進(jìn)行綜合仿真和FPGA 實(shí)現(xiàn)。

2009-04-16 09:25:29 46

46 本文介紹了一種應(yīng)用FPGA 器件完成高速數(shù)字傳輸?shù)?b class="flag-6" style="color: red">方法,利用這種方法實(shí)現(xiàn)無(wú)線收發(fā)芯片nRF2401A 的高速數(shù)據(jù)接口。為進(jìn)一步提高信息的傳輸速率,這里還對(duì)待傳輸?shù)臄?shù)據(jù)進(jìn)行了壓縮處

2009-08-04 09:16:20 9

9 介紹了PCI 9054 接口芯片的性能及數(shù)據(jù)傳輸特點(diǎn),提出了一種基于PCI 9054 外擴(kuò)異步FIFO(先進(jìn)先出)的FPGA(現(xiàn)場(chǎng)可編程門陣列)實(shí)現(xiàn)方法。由于PCI 9054 內(nèi)部FIFO存儲(chǔ)器主要用于數(shù)據(jù)

2010-01-06 15:20:10 44

44 本文主要研究了用FPGA 芯片內(nèi)部的EBRSRAM 來(lái)實(shí)現(xiàn)異步FIFO 設(shè)計(jì)方案,重點(diǎn)闡述了異步FIFO 的標(biāo)志信號(hào)——空/滿狀態(tài)的設(shè)計(jì)思路,并且用VHDL 語(yǔ)言實(shí)現(xiàn),最后進(jìn)行了仿真驗(yàn)證。

2010-01-13 17:11:58 40

40 給出了一個(gè)利用格雷碼對(duì)地址編碼的羿步FIFO 的實(shí)現(xiàn)方法,并給出了VHDL 程序,以解決異步讀寫(xiě)時(shí)鐘引起的問(wèn)題。

2010-07-16 15:15:42 26

26 介紹了異步FIFO在Camera Link接口中的應(yīng)用,將Camera Link接口中的幀有效信號(hào)FVAL和行有效信號(hào)LVAL引入到異步FIFO的設(shè)計(jì)中。分析了FPGA中設(shè)計(jì)異步FIFO的難點(diǎn),解決了異步FIFO設(shè)計(jì)中存在的兩

2010-07-28 16:08:06 32

32 文章介紹了一種在現(xiàn)場(chǎng)可編程門陣列(FPGA)上實(shí)現(xiàn)UART 的方法。首先闡述了UART 異步串行通信原理,然后介紹了實(shí)現(xiàn)UART異步串行通信的硬件接口電路及各部分硬件模塊,以及用硬件

2010-08-06 16:24:13 55

55 摘要:使用FIFO同步源自不同時(shí)鐘域的數(shù)據(jù)是在數(shù)字IC設(shè)計(jì)中經(jīng)常使用的方法,設(shè)計(jì)功能正確的FUFO會(huì)遇到很多問(wèn)題,探討了兩種不同的異步FIFO的設(shè)計(jì)思路。兩種思路

2006-03-24 12:58:33 1666

1666

摘要:首先介紹異步FIFO的概念、應(yīng)用及其結(jié)構(gòu),然后分析實(shí)現(xiàn)異步FIFO的難點(diǎn)問(wèn)題及其解決辦法;在傳統(tǒng)設(shè)計(jì)的基礎(chǔ)上提出一種新穎的電路結(jié)構(gòu)并對(duì)其進(jìn)行

2009-06-20 12:46:50 4131

4131

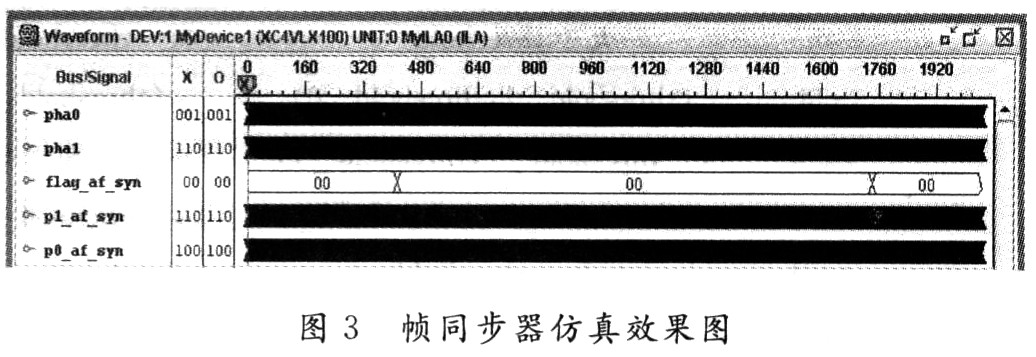

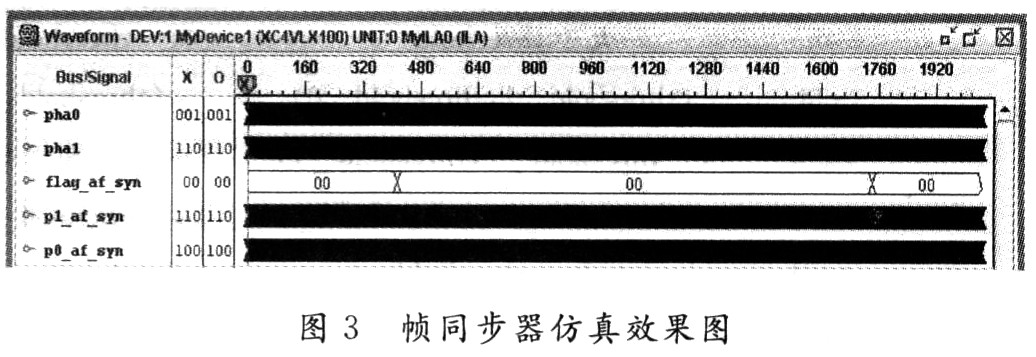

一種高速幀同步和相位模糊估計(jì)的方法及其FPGA實(shí)現(xiàn)

摘要:提出僅依靠接收符號(hào)和本地同步碼快速確定MPSK調(diào)制符號(hào)的幀同步,并同時(shí)估計(jì)其相位模糊值的計(jì)算方法,給

2010-01-27 09:38:17 1833

1833

高速異步FIFO的設(shè)計(jì)與實(shí)現(xiàn)

引言

現(xiàn)代集成電路芯片中,隨著設(shè)計(jì)規(guī)模的不斷擴(kuò)大.一個(gè)系統(tǒng)中往往含有數(shù)個(gè)時(shí)鐘。多時(shí)鐘帶來(lái)的一個(gè)問(wèn)題就是,如何設(shè)

2010-04-12 15:13:08 3176

3176

FPGA設(shè)計(jì)的高速FIFO電路技術(shù)

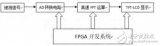

本文主要介紹高速FIFO電路在數(shù)據(jù)采集系統(tǒng)中的應(yīng)用,相關(guān)電路主要有高速A/D轉(zhuǎn)換器、FPGA、SDRAM存儲(chǔ)器等。圖1為本方案的結(jié)構(gòu)框圖。在大容量

2010-05-27 09:58:59 2978

2978

1 FIFO概述

FIFO芯片是一種具有存儲(chǔ)功能的高速邏輯芯片,可在高速數(shù)字系統(tǒng)中用作數(shù)據(jù)緩存。FIFO通常利用雙口RAM和讀寫(xiě)地址產(chǎn)生模塊來(lái)實(shí)現(xiàn)其功能。FIFO的接口信號(hào)包括異步

2010-08-06 10:22:04 5679

5679

為了解決基于LabVIEWFPGA模塊的DMAFIFO深度設(shè)定不當(dāng)帶來(lái)的數(shù)據(jù)不連續(xù)問(wèn)題,結(jié)合LabVIEWFPGA的編程特點(diǎn)和DMA FIFO的工作原理,提出了一種設(shè)定 FIFO 深度的方法。對(duì)FIFO不同深度的實(shí)驗(yàn)表明,采

2011-09-26 13:45:17 7987

7987

本文提出了一種用FPGA實(shí)現(xiàn)糾錯(cuò)編碼的設(shè)計(jì)思想,并以Altera MAX+PluslI為硬件開(kāi)發(fā)平臺(tái)。利用FPGA編程的特點(diǎn),用軟件編程方法,很好的解決了糾錯(cuò)編碼中存在的碼速變換和實(shí)時(shí)性問(wèn)題,實(shí)現(xiàn)

2011-11-10 17:10:59 61

61 文中給出了異步FIFO的實(shí)現(xiàn)代碼和FPGA與DSP的硬件連接電路。經(jīng)驗(yàn)證,利用異步FIFO的方法,在FPGA與DSP通信中的應(yīng)用,具有傳輸速度快、穩(wěn)定可靠、實(shí)現(xiàn)方便的優(yōu)點(diǎn)。

2011-12-12 14:28:22 51

51 為實(shí)現(xiàn)目標(biāo)識(shí)別與跟蹤的應(yīng)用目的 ,在基于 TMS320DM642 的 FIFO 基礎(chǔ)上擴(kuò)展存儲(chǔ)空間 ,提出一種基于

FPGA實(shí)現(xiàn) SDRAM 控制器的方法。分析所用 SDRAM 的特點(diǎn)和工作原理

2015-10-29 14:05:57 2

2 異步FIFO結(jié)構(gòu)及FPGA設(shè)計(jì),解決亞穩(wěn)態(tài)的問(wèn)題

2015-11-10 15:21:37 4

4 一種基于FPGA的以太網(wǎng)高速傳輸平臺(tái),采用DM9000和FPGA芯片,實(shí)現(xiàn)100M以太網(wǎng)數(shù)據(jù)傳輸

2016-02-25 14:45:56 17

17 異步FIFO在FPGA與DSP通信中的運(yùn)用

2016-05-19 11:17:11 0

0 得到模擬應(yīng)用設(shè)計(jì)經(jīng)驗(yàn)的一種方法

2017-01-24 16:29:19 8

8 一種高速卷積編解碼器的FPGA實(shí)現(xiàn)

2017-02-07 15:05:00 22

22 基于異步FIFO在FPGA與DSP通信中的運(yùn)用

2017-10-19 10:30:56 10

10 DSP硬件驅(qū)動(dòng)程序的一種方法

2017-10-19 10:48:45 1

1 介紹了利用CYPRESS公司的FIFO芯片CY7C419實(shí)現(xiàn)DSP間雙向并行異步通訊的方法,該方法簡(jiǎn)單實(shí)用,速度快,特別適用于小數(shù)據(jù)量的數(shù)據(jù)相互傳送。文中給出了CY7C419的引腳功能以及用FIFO

2017-10-25 11:35:25 0

0 代碼和FPGA與DSP的硬件連接電路。經(jīng)驗(yàn)證,利用異步FIFO的方法,在FPGA與DSP通信中的應(yīng)用,具有傳輸速度快、穩(wěn)定可靠、實(shí)現(xiàn)方便的優(yōu)點(diǎn)。 關(guān)鍵詞 異步FIFO;FPGA與DSP數(shù)據(jù)通信;EMIFA

2017-10-30 11:48:44 3

3 介紹一種利用cPLD實(shí)現(xiàn)高速異步串行通信的方法,主要適用于必須使用高速異步串行通信,而對(duì)誤碼率要求又不是很高的應(yīng)用環(huán)境,如基于Rs485協(xié)議的共線語(yǔ)音通信系統(tǒng)。對(duì)實(shí)現(xiàn)方法進(jìn)行詳細(xì)的說(shuō)明,并指出該方法

2017-11-10 14:21:43 4

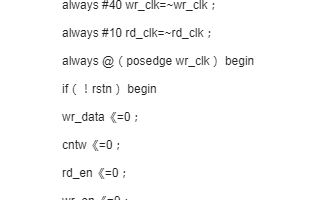

4 (每個(gè)數(shù)據(jù)的位寬) FIFO有同步和異步兩種,同步即讀寫(xiě)時(shí)鐘相同,異步即讀寫(xiě)時(shí)鐘不相同 同步FIFO用的少,可以作為數(shù)據(jù)緩存 異步FIFO可以解決跨時(shí)鐘域的問(wèn)題,在應(yīng)用時(shí)需根據(jù)實(shí)際情況考慮好fifo深度即可 本次要設(shè)計(jì)一個(gè)異步FIFO,深度為8,位寬也是8。

2017-11-15 12:52:41 9177

9177

在現(xiàn)代電路設(shè)計(jì)中,一個(gè)系統(tǒng)往往包含了多個(gè)時(shí)鐘,如何在異步時(shí)鐘間傳遞數(shù)據(jù)成為一個(gè)很重要的問(wèn)題,而使用異步FIFO可以有效地解決這個(gè)問(wèn)題。異步FIFO是一種在電子系統(tǒng)中得到廣泛應(yīng)用的器件,文中介紹了一種基于FPGA的異步FIFO設(shè)計(jì)方法。使用這種方法可以設(shè)計(jì)出高速、高可靠的異步FIFO。

2018-07-17 08:33:00 8860

8860

隨著測(cè)試環(huán)境越來(lái)越復(fù)雜,需要采集的參數(shù)種類越來(lái)越多,要求采集系統(tǒng)連續(xù)采集各種傳感器輸出的模擬信號(hào),而目前常用的固態(tài)存儲(chǔ)器件FLASH的寫(xiě)入速率比較低。本文提出一種基于FPGA(現(xiàn)場(chǎng)可編程門陣列)片

2018-07-12 09:06:00 6077

6077

本文主要介紹了一種基于FPGA的數(shù)字頻譜儀設(shè)計(jì)與實(shí)現(xiàn),該系統(tǒng)主要由信號(hào)采集模塊、高速FFT模塊以及LCD顯示模塊組成。信號(hào)采集模塊以AD9226芯片為核心,配合前置抗混疊濾波電路實(shí)現(xiàn)信號(hào)采集;高速FFT模塊在FPGA開(kāi)發(fā)系統(tǒng)通過(guò)編程實(shí)現(xiàn);LCD顯示模塊選擇4.3寸TFT液晶屏,實(shí)現(xiàn)可視化界面。

2017-12-25 09:46:48 14523

14523

問(wèn)題一種簡(jiǎn)便、快捷的解決方案。使用異步FIFO可以在兩個(gè)不同時(shí)鐘系統(tǒng)之間快速而方便地傳輸實(shí)時(shí)數(shù)據(jù)。在網(wǎng)絡(luò)接口、圖像處理等方面,異步FIFO得到了廣泛的應(yīng)用。 異步FIFO是一種先進(jìn)先出的電路,使用在需要產(chǎn)時(shí)數(shù)據(jù)接口的部分,用來(lái)存儲(chǔ)、緩沖在兩個(gè)異步時(shí)鐘

2018-02-07 14:22:54 0

0 ,常規(guī)做法是利用插值和抽取的方法實(shí)現(xiàn)數(shù)字信號(hào)的變采樣處理,這種方法實(shí)現(xiàn)復(fù)雜,硬件成本高。文中提出了一種高速并行成型濾波器的FPGA實(shí)現(xiàn)方法,這種基于群延時(shí)結(jié)構(gòu)的查找表算法,所需的查找表只需存儲(chǔ)單位沖擊響應(yīng)的采樣值,

2018-02-23 10:14:22 0

0 異步FIFO(Fist-In-First-Out)是一種先入先出的數(shù)據(jù)緩沖器[1]。由于可以很好地解決跨時(shí)鐘域問(wèn)題和不同模塊之間的速度匹配問(wèn)題,而被廣泛應(yīng)用于全局異步局部同步[2](Globally

2018-06-19 15:34:00 3780

3780

異步FIFO廣泛應(yīng)用于計(jì)算機(jī)網(wǎng)絡(luò)工業(yè)中進(jìn)行異步數(shù)據(jù)傳送,這里的異步是指發(fā)送用一種速率而接收用另一速率,因此異步FIFO有兩個(gè)不同的時(shí)鐘,一個(gè)為讀同步時(shí)鐘,一個(gè)為寫(xiě)同步時(shí)鐘。

2019-06-11 08:00:00 3853

3853

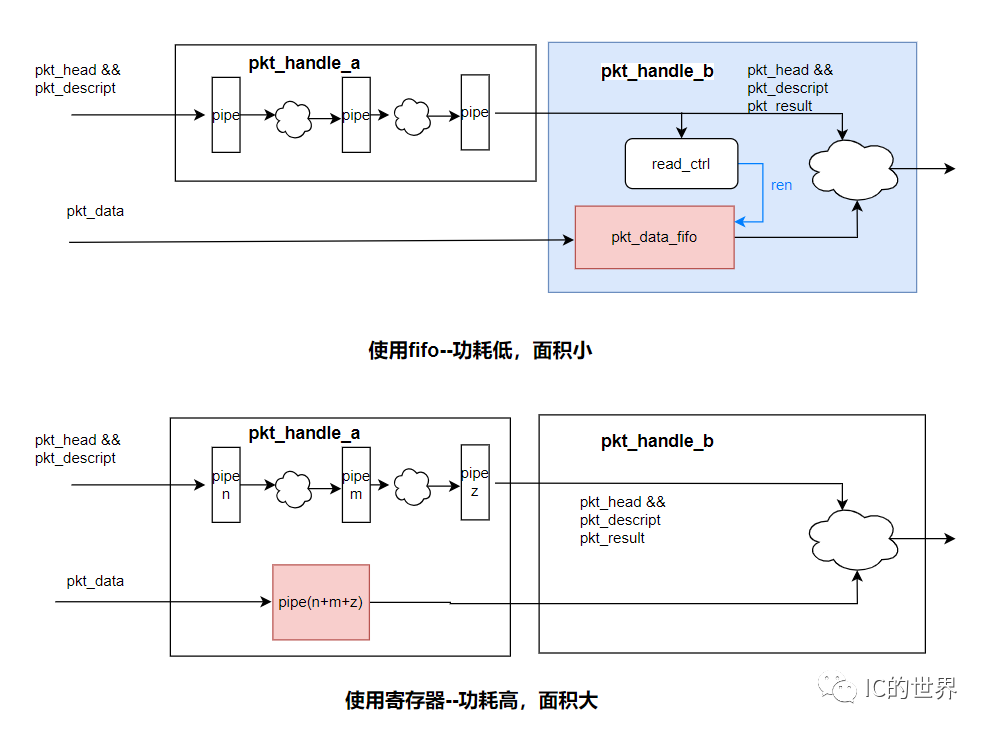

FIFO設(shè)計(jì)。本文提供了一種基于信元的FIFO設(shè)計(jì)方法以供設(shè)計(jì)者在適當(dāng)?shù)臅r(shí)候選用。這種方法也適合于不定長(zhǎng)包的處理。

2018-11-28 08:10:00 8891

8891

介紹了一種用FPGA實(shí)現(xiàn)對(duì)高速A/D轉(zhuǎn)換芯片的控制電路,討論了這一控制電路設(shè)計(jì)思想,提出了更好地解決高速A/D采樣與較慢速的單片機(jī)數(shù)據(jù)處理間矛盾的鏈接方法。

2018-09-21 17:00:29 27

27 異步FIFO存儲(chǔ)器是一種在數(shù)據(jù)交互系統(tǒng)中得到廣泛應(yīng)用的先進(jìn)先出邏輯器件,具有容納異步信號(hào)的頻率(或相位差異)的特點(diǎn)。使用異步FIFO可以在兩個(gè)不同時(shí)鐘系統(tǒng)之間快速而方便地傳輸實(shí)時(shí)數(shù)據(jù)。因此,異步FIFO被廣泛應(yīng)用于實(shí)時(shí)數(shù)據(jù)傳輸、網(wǎng)絡(luò)接口、圖像處理等方面。

2020-01-29 16:54:00 1267

1267

問(wèn)題的有效方法。異步FIFO是一種在電子系統(tǒng)中得到廣泛應(yīng)用的器件,多數(shù)情況下它都是以一個(gè)獨(dú)立芯片的方式在系統(tǒng)中應(yīng)用。本文介紹一種充分利用FPGA內(nèi)部的RAM資源,在FPGA內(nèi)部實(shí)現(xiàn)異步FIFO模塊的設(shè)計(jì)方法。這種異步FIFO比外部 FIFO 芯片更能提高系統(tǒng)的穩(wěn)定性。

2020-07-21 17:09:36 1931

1931

。本文提出了一種用Xilinx公司的FPGA芯片實(shí)現(xiàn)異步HFO的設(shè)計(jì)方案,重點(diǎn)強(qiáng)調(diào)了設(shè)計(jì)有效、可靠的握手信號(hào)EMPTY與FULL的方法,并給出了其VERILOG語(yǔ)言實(shí)現(xiàn)的仿真圖。

2021-01-15 15:27:00 9

9 提出了一種節(jié)能并可升級(jí)的異步FIFO的FPGA實(shí)現(xiàn)。此系統(tǒng)結(jié)構(gòu)利用FPGA內(nèi)自身的資源控制時(shí)鐘的暫停與恢復(fù),實(shí)現(xiàn)了高能效、高工作頻率的數(shù)據(jù)傳輸。該系統(tǒng)在Xilinx的VC4VSX55芯片中實(shí)現(xiàn),實(shí)際

2021-02-02 15:15:00 16

16 FIFO是FPGA處理跨時(shí)鐘和數(shù)據(jù)緩存的必要IP,可以這么說(shuō),只要是任意一個(gè)成熟的FPGA涉及,一定會(huì)涉及到FIFO。但是我在使用異步FIFO的時(shí)候,碰見(jiàn)幾個(gè)大坑,這里總結(jié)如下,避免后來(lái)者入坑。

2021-03-12 06:01:34 12

12 一:fifo是什么 FIFO的完整英文拼寫(xiě)為FirstIn First Out,即先進(jìn)先出。FPGA或者ASIC中使用到的FIFO一般指的是對(duì)數(shù)據(jù)的存儲(chǔ)具有先進(jìn)先出特性的一個(gè)存儲(chǔ)器,常被用于數(shù)據(jù)

2021-03-12 16:30:48 4047

4047

移動(dòng)通信中使用軟件無(wú)線電實(shí)現(xiàn)AGC的一種方法說(shuō)明。

2021-05-27 17:01:59 2

2 隨著微電子工藝技術(shù)和IC設(shè)計(jì)技術(shù)的不斷提高,整個(gè)系統(tǒng)都可集成在一個(gè)芯片上,而且系統(tǒng)芯片的復(fù)雜性越來(lái)越高。為了提高效率,復(fù)用以前的設(shè)計(jì)模塊已經(jīng)成為系統(tǒng)世馘 (SOC)設(shè)計(jì)的必上之路。SOC的實(shí)現(xiàn)基本上有兩種方法,一種是用ASIC芯片實(shí)現(xiàn),另一種是FPGA或PLD芯片實(shí)現(xiàn)。后一種實(shí)現(xiàn)也稱為SOPC實(shí)現(xiàn)。

2021-06-11 15:55:26 2809

2809

跨時(shí)鐘域處理 & 亞穩(wěn)態(tài)處理&異步FIFO1.FIFO概述FIFO: 一、先入先出隊(duì)列(First Input First Output,FIFO)這是一種傳統(tǒng)的按序執(zhí)行方法,先進(jìn)

2021-12-17 18:29:31 10

10 同步FIFO的意思是說(shuō)FIFO的讀寫(xiě)時(shí)鐘是同一個(gè)時(shí)鐘,不同于異步FIFO,異步FIFO的讀寫(xiě)時(shí)鐘是完全異步的。同步FIFO的對(duì)外接口包括時(shí)鐘,清零,讀請(qǐng)求,寫(xiě)請(qǐng)求,數(shù)據(jù)輸入總線,數(shù)據(jù)輸出總線,空以及滿信號(hào)。

2022-11-01 09:58:16 2464

2464 異步fifo詳解 一. 什么是異步FIFO FIFO即First in First out的英文簡(jiǎn)稱,是一種先進(jìn)先出的數(shù)據(jù)緩存器,與普通存儲(chǔ)器的區(qū)別在于沒(méi)有外部讀寫(xiě)的地址線,缺點(diǎn)是只能順序的讀取

2022-12-12 14:17:41 5425

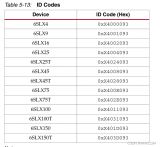

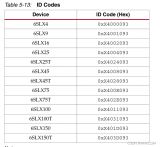

5425 ,這樣就可以通過(guò)讀取IDCODE,來(lái)進(jìn)行自動(dòng)區(qū)分不同的硬件,分別進(jìn)行不同的處理方式。本文介紹Xilinx所有FPGA芯片型號(hào)IDCODE的獲取方法,一共4種方式,總有一種適合你,這些方法同樣適用于別的廠家的FPGA/MCU,比如Intel,Lattice,Microchip等等。

2023-07-03 13:01:31 7553

7553

在RL78/G13芯片上通過(guò)可控硅實(shí)現(xiàn)風(fēng)機(jī)調(diào)速的一種方法

2023-09-28 16:23:23 2371

2371

簡(jiǎn)單的一種,其特點(diǎn)是輸入和輸出都與時(shí)鐘信號(hào)同步,當(dāng)時(shí)鐘到來(lái)時(shí),數(shù)據(jù)總是處于穩(wěn)定狀態(tài),因此容易實(shí)現(xiàn)數(shù)據(jù)的傳輸和存儲(chǔ)。 而異步FIFO則是在波形的上升沿和下降沿上進(jìn)行處理,在輸入輸出端口處分別增加輸入和輸出指針,用于管理數(shù)據(jù)的讀寫(xiě)。異步FIFO的輸入和輸出可同時(shí)進(jìn)行,中間可以

2023-10-18 15:23:58 2604

2604 請(qǐng)問(wèn)異步FIFO的溢出操作時(shí)怎么樣判斷的? 異步FIFO是數(shù)據(jù)傳輸?shù)?b class="flag-6" style="color: red">一種常用方式,在一些儲(chǔ)存器和計(jì)算機(jī)系統(tǒng)中,常常會(huì)用到異步FIFO。作為一種FIFO,異步FIFO經(jīng)常面臨兩種情況:溢出和空槽位

2023-10-18 15:28:41 4290

4290 ? 點(diǎn)擊上方 藍(lán)字 關(guān)注我們 ? 第一節(jié):fifo基礎(chǔ) ? ? 內(nèi)容: 1. 掌握FPGA設(shè)計(jì)中關(guān)于數(shù)據(jù)緩存的使用 2. 掌握FIFO工作原理

2023-11-17 14:00:02 1220

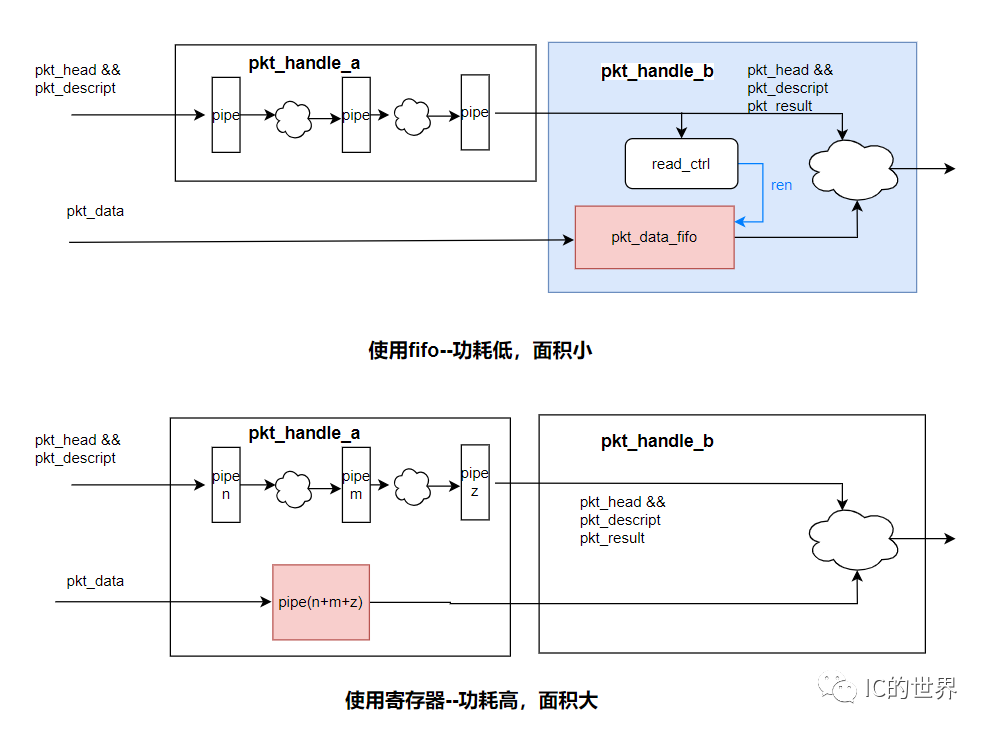

1220 本案例中,我們講解一種使用fifo節(jié)約資源,降低功耗的設(shè)計(jì)。

2023-12-15 16:34:11 1369

1369

本文描述了一種簡(jiǎn)單高效配置FPGA的方法,該方法利用微處理器從串行外圍接口(SPI)閃存配置FPGA設(shè)備。這種方法減少了硬件組件、板空間和成本。

2024-10-24 14:57:24 2383

2383

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論