本文介紹了一個基于FPGA的內存到串行數據傳輸模塊,該模塊設計用來高效地處理存儲器中的數據并傳輸至串行接口。項目中自定義的“datamover_mm2s_fpga_”方案利用異步FIFO結構來解決不同時鐘域之間數據傳輸的同步問題。

2025-11-12 14:31:30 4133

4133

現代集成電路芯片中,隨著設計規模的不斷擴大。一個系統中往往含有數個時鐘。多時鐘帶來的一個問題就是,如何設計異步時鐘之間的接口電路。異步 FIFO(First In First Out)是解決這個問題的一種簡便、快捷的解決方案。##異步FIFO的VHDL語言實現

2014-05-28 10:56:41 9209

9209 大家好,又到了每日學習的時間了,今天我們來聊一聊基于FPGA的異步FIFO的實現。 一、FIFO簡介 FIFO是英文First In First Out 的縮寫,是一種先進先出的數據緩存器,它與普通

2018-06-21 11:15:25 7147

7147

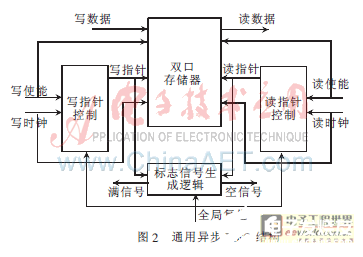

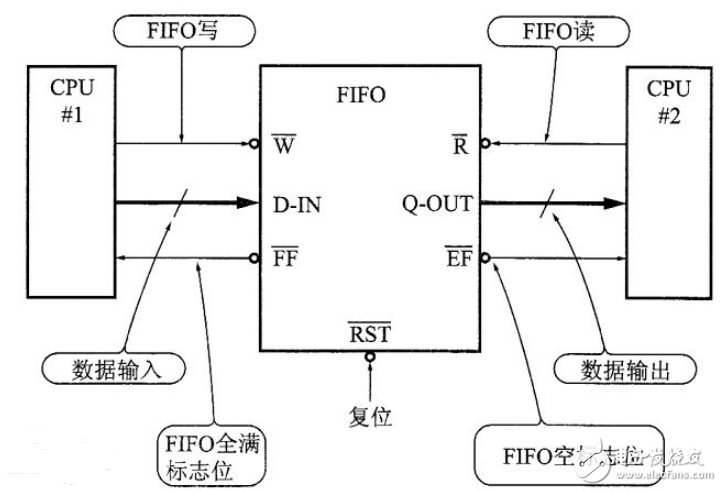

是這個問題的一種簡便、快捷的解決方案,使用異步 FIFO 可以在兩個不同時鐘系統之間快速而方便地傳輸實時數據。

2020-07-16 17:41:46 1530

1530

FIFO (先入先出, First In First Out )存儲器,在 FPGA 和數字 IC 設計中非常常用。 根據接入的時鐘信號,可以分為同步 FIFO 和異步 FIFO 。

2023-06-27 10:24:37 3136

3136

FIFO是一種先進先出數據緩存器,它與普通存儲器的區別是沒有外部讀寫地址線,使用起來非常簡單,缺點是只能順序讀寫,而不能隨機讀寫。

2024-04-09 14:23:15 4603

4603

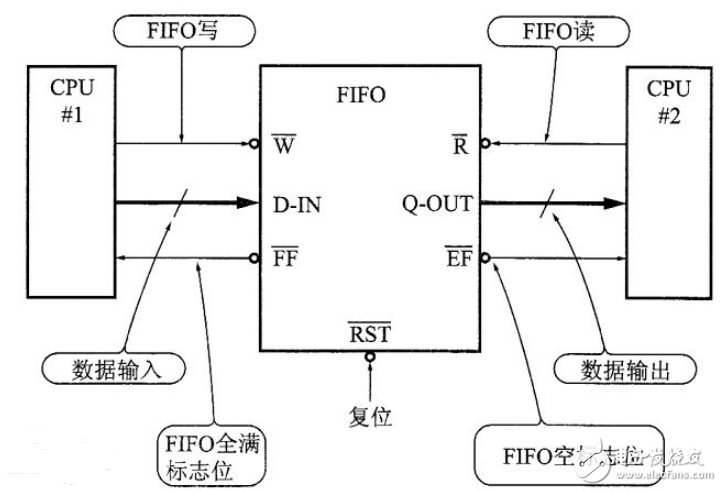

FIFO存儲器是系統的緩沖環節,如果沒有FIFO存儲器,整個系統就不可能正常工作,它主要有幾方面的功能:1)對連續的數據流進行緩存,防止在進機和存儲操作時丟失數據;2)數據集中起來進行進棧和存儲,可

2022-01-18 10:03:06

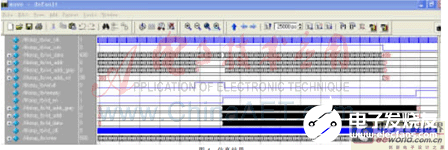

實例內部系統功能框圖如圖9.72所示。我們通過IP核例化一個異步FIFO,定時寫入數據,然后再讀出所有數據。通過QuartusII集成的在線邏輯分析儀SignalTap II,我們可以觀察FPGA片內

2019-05-06 00:31:57

摘要:針對現有小型無人機導航系統的解算速度慢、多處理器核心臃腫可靠性差的缺點,實現了一種僅使用單一FPGA作為數據處理核心的小型高速導航解算系統。該系統對飛機運動方程組和導航方程組進行并行化分

2019-07-03 06:57:34

具體應用情況:5509A DSP 的CE1空間外接了一個異步存儲器(FIFO),由DSP提供的異步讀時鐘 ARE 的頻率是怎么控制的呢?是主頻/(建立時間+選通時間+保持時間)嗎?當然這三個時間可由

2015-01-13 20:33:46

取出、掉電丟失。在各類邏輯系統中運用非常廣泛。在FPGA高級應用四的這個標題下,我們將會從內部存儲器到外部存儲器,介紹FIFO、ram、ddr幾種常用的存儲器設計。第一期我們介紹FIFOFIFO,全稱是first in first out (先入先出存儲隊列) 。在程序中FIFO作為數據的隊列通道,

2021-06-28 09:27:19

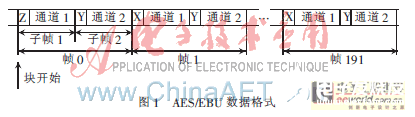

【作者】:趙宇紅;曾雷;白皛;謝人超;閻利早;【來源】:《電聲技術》2010年02期【摘要】:針對串行數字接口(SDI),提出了一種基于FPGA的音頻數據IP模塊解嵌方案。介紹了相關協議標準,重點

2010-04-22 11:54:44

概述該工程實例內部系統功能框圖如圖所示。我們通過IP核例化一個異步FIFO,這個FIFO的讀寫時鐘頻率不同,并且讀寫位寬也不同。定時對這個異步FIFO寫入數據,然后再讀出所有數據。通過ISE集成的在線

2016-03-07 11:32:16

一丶存儲器的分類和層次半導體存儲芯片:片選器:用來選取芯片有兩種譯碼驅動方式:線選法:一維排列,結構簡單,適合容量不大的存儲芯片重合法:二維陣列,適合容量大為什么線選法不適合大的呢?我們以9組

2021-07-23 08:20:14

時序一 什么是FIFOFirst In First Out ,是一種先進先出的數據緩存器,他與普通存儲器的區別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點就是只能順序寫入數據,順序的讀出數據,其

2021-12-27 08:05:35

入的指令先完成并引退,跟著才執行第二條指令。 1.什么是FIFO? FIFO是英文First In First Out 的縮寫,是一種先進先出的數據緩存器,他與普通存儲器的區別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點就是只能順序寫入數據,順序的讀出數據,其數據地址由內部讀寫指針自動加1完成

2022-02-16 06:55:41

內存儲器可以在FPGA配置時自動初始化,相當于提供了一種非易失性的功能。片內存儲器的最佳應用場合包括作為常見的緩存、點到點的緩存、查找表以及FIFO等。緩存,由于其具有低反應延時,片內存儲器在微處理器中作為

2016-10-10 17:08:22

In First Out),即先入先出,這是一種典型的計算機數據或指令處理機制,和中國人所謂的“先來后到”理念有異曲同工之妙。而我們這里要說的FIFO存儲器,和前面帶有地址可直接定位操作的ROM或RAM存儲器

2016-12-23 17:48:03

強大的硬件支持。SOPC是Ahera公司提出的一種靈活、高效的片上系統(SOC)解決方案,它將處理器、存儲器、I/O口等系統設計所需要的功能模塊集成到一個可編程器件上,從而構成一個可編程的片上系統

2018-12-07 10:27:46

如何利用Xilinx FPGA和存儲器接口生成器簡化存儲器接口?

2021-05-06 07:23:59

本文介紹了一種0.13微米CMOS T藝下FPGA中嵌入式存儲器模塊的設計與實現。

2021-04-09 06:02:09

擴展存儲器讀寫實驗的目的是什么?怎樣去設計一種擴展存儲器讀寫的電路?擴展存儲器讀寫實驗的流程有哪些?

2021-07-14 07:04:49

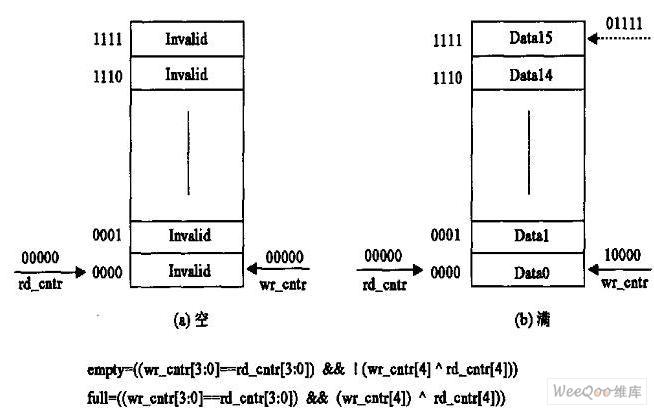

通過對FPGA芯片內部EBRSRAM的深入研究,提出了一種利用格雷碼對地址進行編碼的異步FIFO設計方案。

2021-04-13 06:41:03

FIFO的基本結構和工作原理異步FIFO設計中的問題與解決辦法FPGA內部軟異步FIFO設計

2021-04-08 07:07:45

解碼器需要一個恒速的傳輸流)。雖然存儲器對同步的要求似乎很小,但當涉及到多個碼流時它可能很顯著。這種同步可以由一個異步FIFO實現。 2) 幀存儲: 幀存儲在這些地方需要:任何暫時的處理如幀率轉換

2011-07-15 09:18:00

怎么設計一種面向嵌入式存儲器測試和修復的IIP?如何解決設計和制造過程各個階段的良品率問題?嵌入式存儲器測試和修復技術的未來趨勢是什么?STAR存儲器系統的功能是什么?

2021-04-15 06:05:51

為什么要設計一種異步FIFO?異步FIFO的設計原理是什么?怎樣去設計一種異步FIFO?

2021-06-18 09:20:29

怎樣去設計一種高效率音頻功率放大器?如何對高效率音頻功率放大器進行測試驗證?

2021-06-02 06:11:23

網絡存儲器技術是如何產生的?怎樣去設計一種網絡存儲器?

2021-05-26 07:00:22

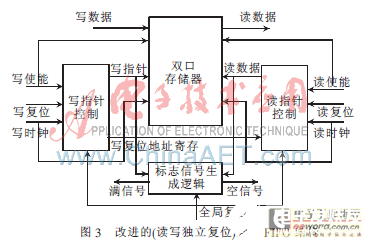

首先介紹異步FIFO 的概念、應用及其結構,然后分析實現異步FIFO的難點問題及其解決辦法; 在傳統設計的基礎上提出一種新穎的電路結構并對其進行綜合仿真和FPGA 實現。

2009-04-16 09:25:29 46

46 基于一種適合于測試靜態簡化故障的March SS 算法,提出了一種改進的嵌入式隨機存取存儲器測試算法-March SSE 算法。該算法在測試長度不變的情況下,不僅能測出March SS 算法所測

2009-08-18 09:37:18 14

14 本文設計了一種基于0.13 微米CMOS 工藝的FPGA 芯片中的嵌入式存儲器模塊。該容量為18Kb 的同步雙端口存儲模塊,可以配置成為只讀存儲器或靜態隨機存儲器,每個端口有6 種數據寬

2009-12-19 16:19:50 24

24 介紹了PCI 9054 接口芯片的性能及數據傳輸特點,提出了一種基于PCI 9054 外擴異步FIFO(先進先出)的FPGA(現場可編程門陣列)實現方法。由于PCI 9054 內部FIFO存儲器主要用于數據

2010-01-06 15:20:10 44

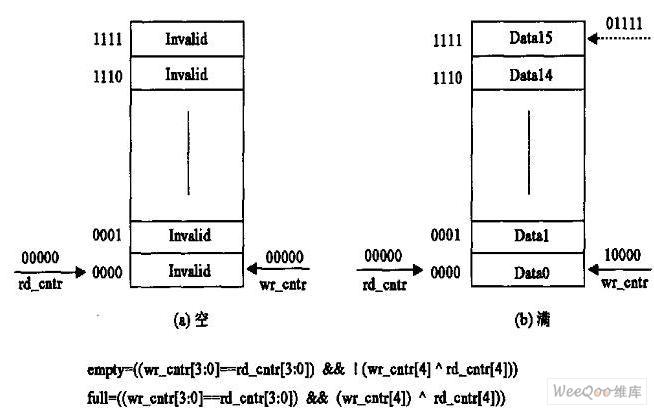

44 本文主要研究了用FPGA 芯片內部的EBRSRAM 來實現異步FIFO 設計方案,重點闡述了異步FIFO 的標志信號——空/滿狀態的設計思路,并且用VHDL 語言實現,最后進行了仿真驗證。

2010-01-13 17:11:58 40

40 不同的應用對存儲器結構有不同的需求:在運行控制任務時,需要Cache 匹配速度差異;在處理數據流時,需要片內存儲器提高訪問帶寬。本文設計了一種基于SRAM 的可配置Cache/SRAM

2010-01-25 11:53:55 24

24 基于SMPTE 272M標準,提出了在標準清晰度視頻信號中加嵌和解嵌音頻信號的硬件實現方案,詳細分析了這兩種系統的組成工作原理與設計過程,并介紹了音頻加解嵌在數字廣播系統

2010-04-25 10:24:38 27

27 介紹了異步FIFO在Camera Link接口中的應用,將Camera Link接口中的幀有效信號FVAL和行有效信號LVAL引入到異步FIFO的設計中。分析了FPGA中設計異步FIFO的難點,解決了異步FIFO設計中存在的兩

2010-07-28 16:08:06 32

32 簡介

SDX6811N/SDX6812N是數字音頻解嵌模塊。兩模塊的區別是:SDX6811N的數字音頻輸出是非平衡的,而SDX6812N的數字音頻輸出是平衡的。

該模塊可以從SD-SDI中解嵌4路,即2對

2010-12-18 22:45:39 32

32 摘要:使用FIFO同步源自不同時鐘域的數據是在數字IC設計中經常使用的方法,設計功能正確的FUFO會遇到很多問題,探討了兩種不同的異步FIFO的設計思路。兩種思路

2006-03-24 12:58:33 1660

1660

摘要:磁電存儲器不僅存取速度快、功耗小,而且集動態RAM、磁盤存儲和高速緩沖存儲器功能于一身,因而已成為動態存儲器研究領域的一個熱點。文章總結了磁電

2006-03-24 13:01:37 2313

2313

摘要:首先介紹異步FIFO的概念、應用及其結構,然后分析實現異步FIFO的難點問題及其解決辦法;在傳統設計的基礎上提出一種新穎的電路結構并對其進行

2009-06-20 12:46:50 4131

4131

存儲器卡,存儲器卡是什么意思

存儲器卡(Memory Card)是一種用電可擦除的可編程只讀存儲器(EEPROM)為核心的,能多次重復使用的IC卡。沒

2010-04-01 17:44:07 3966

3966 FPGA設計的高速FIFO電路技術

本文主要介紹高速FIFO電路在數據采集系統中的應用,相關電路主要有高速A/D轉換器、FPGA、SDRAM存儲器等。圖1為本方案的結構框圖。在大容量

2010-05-27 09:58:59 2978

2978

數字視音頻加解嵌模塊是將標清串行數字信號與數字或模擬音頻信號進行加解嵌處理的模塊。模塊可提供外部參考輸入接口,主要用于調整模擬復合輸出圖象的H/V/SC相位,數字信號均衡

2011-03-31 14:09:45 38

38 賽普拉斯半導體公司日前宣布推出一款容量高達 72 Mbit 的先進先出 (FIFO) 存儲器。該款全新的高容量 (HD) FIFO 是視頻及成像應用的理想選擇,可滿足高效緩沖所需的高容量和高頻率要求

2011-06-17 09:42:02 2992

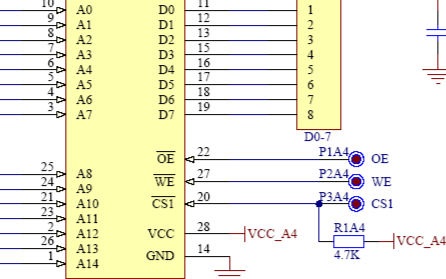

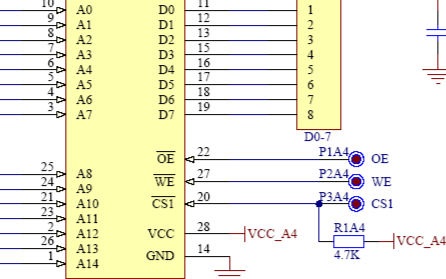

2992 文中給出了異步FIFO的實現代碼和FPGA與DSP的硬件連接電路。經驗證,利用異步FIFO的方法,在FPGA與DSP通信中的應用,具有傳輸速度快、穩定可靠、實現方便的優點。

2011-12-12 14:28:22 51

51 異步SRAM存儲器接口電路設計(Altera FPGA開發板)如圖所示:

2012-08-15 14:37:05 4265

4265

為實現目標識別與跟蹤的應用目的 ,在基于 TMS320DM642 的 FIFO 基礎上擴展存儲空間 ,提出一種基于

FPGA實現 SDRAM 控制器的方法。分析所用 SDRAM 的特點和工作原理

2015-10-29 14:05:57 2

2 異步FIFO結構及FPGA設計,解決亞穩態的問題

2015-11-10 15:21:37 4

4 異步FIFO在FPGA與DSP通信中的運用

2016-05-19 11:17:11 0

0 一種高可靠星載大容量存儲器的壞塊表存儲方案設計_李姍

2017-01-03 15:24:45 0

0 一種基于時鐘抽取偏置電壓技術的存儲器位線_楊澤重

2017-01-07 21:45:57 0

0 基于異步FIFO在FPGA與DSP通信中的運用

2017-10-19 10:30:56 10

10 摘要 利用異步FIFO實現FPGA與DSP進行數據通信的方案。FPGA在寫時鐘的控制下將數據寫入FIFO,再與DSP進行握手后,DSP通過EMIFA接口將數據讀入。文中給出了異步FIFO的實現

2017-10-30 11:48:44 3

3 (每個數據的位寬) FIFO有同步和異步兩種,同步即讀寫時鐘相同,異步即讀寫時鐘不相同 同步FIFO用的少,可以作為數據緩存 異步FIFO可以解決跨時鐘域的問題,在應用時需根據實際情況考慮好fifo深度即可 本次要設計一個異步FIFO,深度為8,位寬也是8。

2017-11-15 12:52:41 9176

9176

由于同步動態隨機存儲器SDRAM內部結構原因導致其控制邏輯比較復雜。現場可編程邏輯門陣列FPGA作為一種半定制電路具有速度快、內部資源豐富、可重構等優點。本文設計了一種基于FPGA的SDRAM

2017-11-18 12:42:03 2520

2520

在現代電路設計中,一個系統往往包含了多個時鐘,如何在異步時鐘間傳遞數據成為一個很重要的問題,而使用異步FIFO可以有效地解決這個問題。異步FIFO是一種在電子系統中得到廣泛應用的器件,文中介紹了一種基于FPGA的異步FIFO設計方法。使用這種方法可以設計出高速、高可靠的異步FIFO。

2018-07-17 08:33:00 8860

8860

FIFO( First In First Out)簡單說就是指先進先出。由于微電子技術的飛速發展,新一代FIFO芯片容量越來越大,體積越來越小,價格越來越便宜。作為一種新型大規模集成電路,FIFO芯片以其靈活、方便、高效的特性。

2017-12-06 14:29:31 11098

11098

起來可能比較困難。我們必須確保包括電路板布局、電源和 FPGA 中存儲器接口電路等諸多因素準確無誤,才能實現一款切實可行的存儲器設計。

2018-01-12 11:48:44 1662

1662

問題一種簡便、快捷的解決方案。使用異步FIFO可以在兩個不同時鐘系統之間快速而方便地傳輸實時數據。在網絡接口、圖像處理等方面,異步FIFO得到了廣泛的應用。 異步FIFO是一種先進先出的電路,使用在需要產時數據接口的部分,用來存儲、緩沖在兩個異步時鐘

2018-02-07 14:22:54 0

0 時丟失數據;2)數據集中起來進行進機和存儲,可避免頻繁的總線操作,減輕CPU的負擔;3)允許系統進行DMA操作,提高數據的傳輸速度。這是至關重要的一點,如果不采用DMA操作,數據傳輸將達不到傳輸要求,而且大大增加CPU的負擔,無法同時完成數據的存儲工作。下面為大家介紹了幾種fifo存儲器芯片。

2018-04-08 16:11:32 26306

26306

異步FIFO(Fist-In-First-Out)是一種先入先出的數據緩沖器[1]。由于可以很好地解決跨時鐘域問題和不同模塊之間的速度匹配問題,而被廣泛應用于全局異步局部同步[2](Globally

2018-06-19 15:34:00 3780

3780

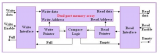

本32X8 FIFO的設計,采用了雙體存儲器的交替讀寫機制,使得在對其中一個存儲器寫操作的同時可以對另一個存儲器進行讀操作;對其中一個存儲器讀操作的同時可以對另一個存儲器進行寫操作。實現了高速數據緩沖,速度比單體存儲器的FIFO提高了一倍。

2018-12-30 10:29:00 4312

4312

本篇主要總結的是塊狀Memory(Block Memory),實際上就是FPGA內部獨立于邏輯單元的專用存儲器,更像是一種硬核。

2018-12-08 11:05:47 3296

3296 FPGA的邏輯是通過向內部靜態存儲單元加載編程數據來實現的,存儲在存儲器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯接方式,并最終決定了FPGA所能實現的功能,FPGA允許無限次的編程。

2019-11-12 07:09:00 1993

1993 介紹了TI公司TMS320C67系列DSP的EMIF(外部存儲器接口)與異步FIFO(先進先出)存儲器的硬件接口設計,著重描述了用EDMA(擴展的直接存儲器訪問)方式讀取FIFO存儲器數據的軟件設計

2019-07-31 16:40:47 21

21 本文檔的主要內容詳細介紹的是FIFO存儲器的尺寸圖免費下載。

2019-08-15 08:00:00 2

2 關鍵詞:異步SRAM , SRAM SRAM是Static Random-Access Memory的縮寫,中文稱為靜態隨機存儲器。SRAM是一種具有靜止存取功能的存儲器,不需要通過刷新電路就能保存

2020-03-08 17:15:00 4433

4433

問題的有效方法。異步FIFO是一種在電子系統中得到廣泛應用的器件,多數情況下它都是以一個獨立芯片的方式在系統中應用。本文介紹一種充分利用FPGA內部的RAM資源,在FPGA內部實現異步FIFO模塊的設計方法。這種異步FIFO比外部 FIFO 芯片更能提高系統的穩定性。

2020-07-21 17:09:36 1931

1931

在FPGA開發板上都有幾種不同的存儲器,比如SDRAM,FLASH,EPCS,還有內部

2020-10-09 11:41:41 3824

3824 FIFO 是英文 First In First Out 的縮寫,是一種先進先出的數據緩存器,它與普通存儲器的區別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點就是只能順序寫入數據,順序的讀出數據

2020-12-22 13:11:00 1

1 提出了一種節能并可升級的異步FIFO的FPGA實現。此系統結構利用FPGA內自身的資源控制時鐘的暫停與恢復,實現了高能效、高工作頻率的數據傳輸。該系統在Xilinx的VC4VSX55芯片中實現,實際

2021-02-02 15:15:00 16

16 FIFO是FPGA處理跨時鐘和數據緩存的必要IP,可以這么說,只要是任意一個成熟的FPGA涉及,一定會涉及到FIFO。但是我在使用異步FIFO的時候,碰見幾個大坑,這里總結如下,避免后來者入坑。

2021-03-12 06:01:34 12

12 一:fifo是什么 FIFO的完整英文拼寫為FirstIn First Out,即先進先出。FPGA或者ASIC中使用到的FIFO一般指的是對數據的存儲具有先進先出特性的一個存儲器,常被用于數據

2021-03-12 16:30:48 4047

4047

1.定義 FIFO是英文First In First Out 的縮寫,是一種先進先出的數據緩存器,他與普通存儲器的區別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點就是只能順序寫入數據,順序

2021-04-09 17:31:42 6216

6216

入的指令先完成并引退,跟著才執行第二條指令。 1.什么是FIFO? FIFO是英文First In First Out 的縮寫,是一種先進先出的數據緩存器,他與普通存儲器的區別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點就是只能順序寫入數據,順序的讀出數據,其數據地址由內部讀寫指針自動加1完成

2021-12-17 18:29:31 10

10 異步fifo詳解 一. 什么是異步FIFO FIFO即First in First out的英文簡稱,是一種先進先出的數據緩存器,與普通存儲器的區別在于沒有外部讀寫的地址線,缺點是只能順序的讀取

2022-12-12 14:17:41 5421

5421 FIFO(First In First Out)是異步數據傳輸時經常使用的存儲器。該存儲器的特點是數據先進先出(后進后出)。其實,多位寬數據的異步傳輸問題,無論是從快時鐘到慢時鐘域,還是從慢時鐘到快時鐘域,都可以使用 FIFO 處理。

2023-03-26 16:00:21 4788

4788

FIFO(First In First Out )先入先出存儲器,在FPG設計中常用于跨時鐘域的處理,FIFO可簡單分為同步FIFO和異步FIFO。

2023-04-25 15:55:28 5975

5975

FIFO是異步數據傳輸時常用的存儲器,多bit數據異步傳輸時,無論是從快時鐘域到慢時鐘域,還是從慢時鐘域到快時鐘域,都可以使用FIFO處理。

2023-05-26 16:12:49 2243

2243

FIFO(First In First Out)是異步數據傳輸時經常使用的存儲器。該存儲器的特點是數據先進先出(后進后出)。

2023-05-29 15:35:42 9923

9923

FIFO(First In First Out)是一種先進先出的存儲結構,經常被用來在FPGA設計中進行數據緩存或者匹配傳輸速率。

2023-08-07 15:39:50 2190

2190 的原理很簡單,寫操作是在寫使能有效時,寫地址指針(Write_Pointer)逐漸遞增,將數據寫入存儲器的相應位置。讀操作是在讀使能信號有效時,讀地址指(Read_Pointer)逐漸遞增,從存儲器的相應位置讀取數據。

2023-09-14 11:21:45 2182

2182

簡單的一種,其特點是輸入和輸出都與時鐘信號同步,當時鐘到來時,數據總是處于穩定狀態,因此容易實現數據的傳輸和存儲。 而異步FIFO則是在波形的上升沿和下降沿上進行處理,在輸入輸出端口處分別增加輸入和輸出指針,用于管理數據的讀寫。異步FIFO的輸入和輸出可同時進行,中間可以

2023-10-18 15:23:58 2603

2603 請問異步FIFO的溢出操作時怎么樣判斷的? 異步FIFO是數據傳輸的一種常用方式,在一些儲存器和計算機系統中,常常會用到異步FIFO。作為一種FIFO,異步FIFO經常面臨兩種情況:溢出和空槽位

2023-10-18 15:28:41 4290

4290 ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 1.1片上存儲(on-chip ram) ? ? ? ? ? ? ? 在實際應用中任何場合都離不開數據,只要有數據的地方就有存儲器,一般存儲分為了2種,一種時可以讀寫,一種時只讀

2023-11-17 14:00:02 1219

1219 半導體存儲器(Semiconductor Memory)是一種電子元件,用于存儲和檢索數據。它由半導體材料制成,采用了半導體技術,是計算機和電子設備中最常用的存儲器。 半導體存儲器可以分為兩種

2024-02-01 17:19:05 5136

5136 帶通濾波器和帶阻濾波器哪個更適合音頻處理?有什么區別?跟著維愛普小編一起來了解一下吧:

2024-04-07 09:28:29 2038

2038

1. FIFO簡介 FIFO是一種先進先出數據緩存器,它與普通存儲器的區別是沒有外部讀寫地址線,使用起來非常簡單,缺點是只能順序讀寫,而不能隨機讀寫。 2. 使用場景 數據緩沖:也就是數據寫入過快

2024-06-04 14:27:37 3489

3489

微控制器(MCU)內部的存儲器是微控制器系統的重要組成部分,它負責存儲程序代碼、數據以及控制邏輯等信息。這些存儲器類型多樣,各具特點,共同支持著微控制器的正常運行和高效工作。以下是對微控制器內部存儲器的詳細介紹。

2024-08-22 10:41:50 1965

1965 )兩大類組成,以及還包括一些高速緩存(Cache)和寄存器(Register)等。下面將詳細介紹這些內部存儲器的工作原理、作用以及它們之間的區別。

2024-09-05 10:42:19 7303

7303 本文描述了一種簡單高效配置FPGA的方法,該方法利用微處理器從串行外圍接口(SPI)閃存配置FPGA設備。這種方法減少了硬件組件、板空間和成本。

2024-10-24 14:57:24 2382

2382

電子發燒友App

電子發燒友App

評論