相鄰的格雷碼只有1bit的差異,因此格雷碼常常用于異步fifo設計中,保證afifo的讀地址(或寫地址)被寫時鐘(或讀時鐘)采樣時最多只有1bit發生跳變。

在不考慮路徑延時的情況下,因為源數據(讀寫地址)只有1bit變化,即使發生了亞穩態,最終的結果相當于被目的時鐘延遲一拍采樣。

需要注意的是:異步fifo中使用格雷碼無法避免亞穩態,它起到的作用是,即使發生了亞穩態,依舊能夠保證異步fifo的功能正確

| 10進制 | 二進制 | 格雷碼 |

| 0 | 000 | 000 |

| 1 | 001 | 001 |

| 2 | 010 | 011 |

| 3 | 011 | 010 |

| 4 | 100 | 110 |

| 5 | 101 | 111 |

| 6 | 110 | 101 |

| 7 | 111 | 100 |

1.二進制轉格雷碼

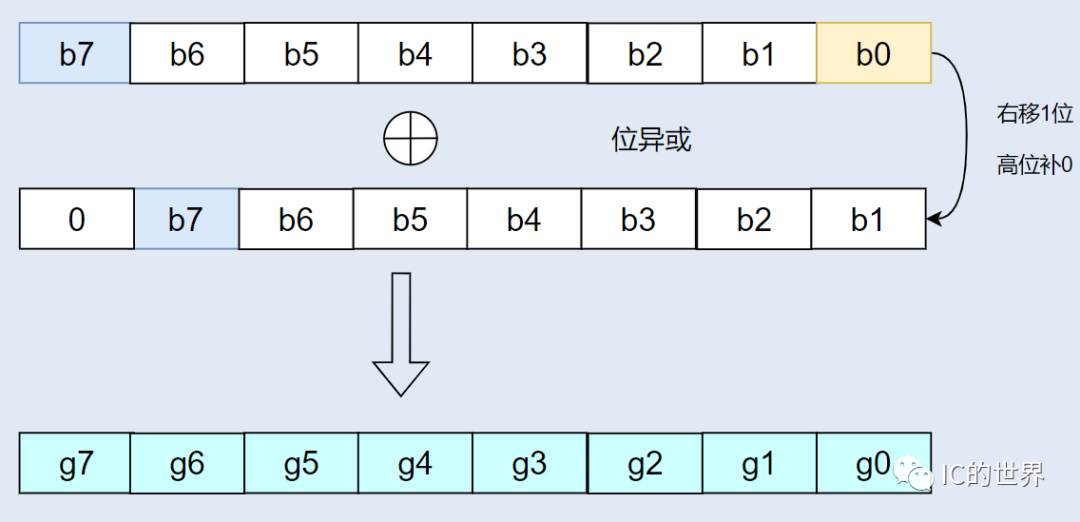

圖1:二進制轉格雷碼

圖1:二進制轉格雷碼

如圖所示,二進制轉格雷碼實現簡單,二進制數據右移1bit,高位補零后與自身進行位異或得到格雷碼。代碼實現如下:waddr為二進制寫地址,waddr_gray為對應的寫地址格雷碼

assign waddr_gray[ADDR_WDTH:0]=waddr[ADDR_WDTH:0] ^ {1’b0,waddr[ADDR_WDTH:1] };

2.格雷碼轉二進制

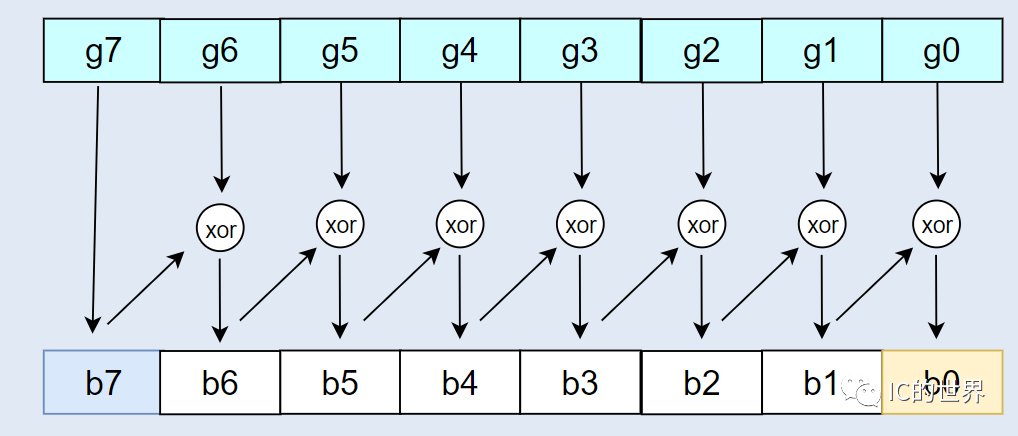

圖2:格雷碼轉2進制 首先需要強調一下異或操作的特點:

A、B、C為1bit二進制整數,假設等式為A^B==C,那么已知B和C的情況下,可以通過A==B^C求得A數值。此處可以使用窮舉法嘗試一下,只有4種情況。

從二進制轉格雷碼也可以反推出格雷碼轉二進制的思路。

首先:最高bit位是相等的,b7等于g7。

因為g6==b7^b6,根據異或特性(由A^B==C得到A==B^C),可得知b6=b7^g6,即b6=g7^g6

因為g5==b5^b6,根據異或特性,可得知b5=g5^b6,即b5=g5^g6^g7

依次類推:b0=g0^g1^g2^g3^g4^g6^g7

在如下Verilog代碼實現中,我們提供了3種寫法。

寫法1和寫法2都是已知確定位寬的情況下,實現格雷碼轉二進制碼,不利于參數化。

寫法3采用function函數實現,不限制位寬,支持參數化。

//寫法 1

assign bin_code[0]=gray_code[0]^gray_code[1]^gray_code[2]^gray_code[3] ;

assign bin_code[1]=gray_code[1]^gray_code[2]^gray_code[3] ;

assign bin_code[2]=gray_code[2]^gray_code[3] ;

assign bin_code[3]=gray_code[3] ;

//寫法2

assign bin_code = {gray_code[3], ^gray_code[3:2], ^gray_code[3:1], ^gray_code};

//寫法3:

function [ADDR_WIDTH:0] bin_out;

input [ADDR_WIDTH:0] gray_in;

reg [ADDR_WIDTH:0] gray_code;

reg [ADDR_WIDTH:0] bin_code;

integer i,j;

reg tmp;

begin

gray_code = gray_in;

for(i=0;i<=ADDR_WIDTH;i=i+1)

begin

tmp=1'b0;

for(j=i;j<=ADDR_WIDTH;j=j+1)

tmp=gray_code[j]^tmp;

bin_code[i]=tmp;

end

bin_out= bin_code;

end

endfunction

審核編輯:湯梓紅

-

fifo

+關注

關注

3文章

407瀏覽量

45860 -

格雷碼

+關注

關注

2文章

34瀏覽量

13552 -

異步FIFO

+關注

關注

0文章

20瀏覽量

8716 -

FIFO設計

+關注

關注

0文章

7瀏覽量

5131

原文標題:

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

詳細討論異步FIFO的具體實現???

格雷碼辨析

異步FIFO設計之格雷碼

異步FIFO設計之格雷碼

評論