電阻,因為物質(zhì)對電流產(chǎn)生的阻礙作用,所以稱其該作用下的電阻物質(zhì)。電阻將會導(dǎo)致電子流通量的變化,電阻越小,電子流通量越大,反之亦然。沒有電阻或電阻很小的物質(zhì)稱其為電

2012-03-12 16:46:08 12594

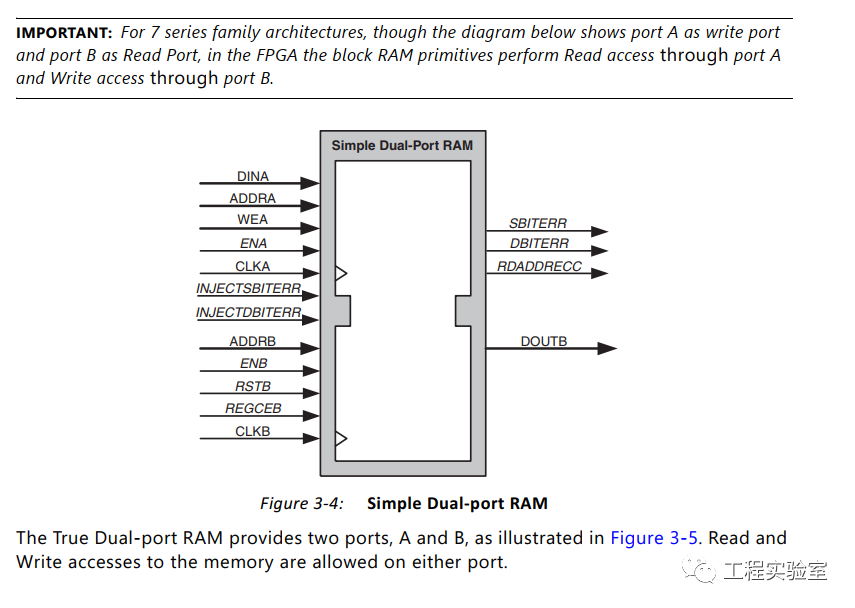

12594 利用FPGA實現(xiàn)雙口RAM的設(shè)計及應(yīng)用

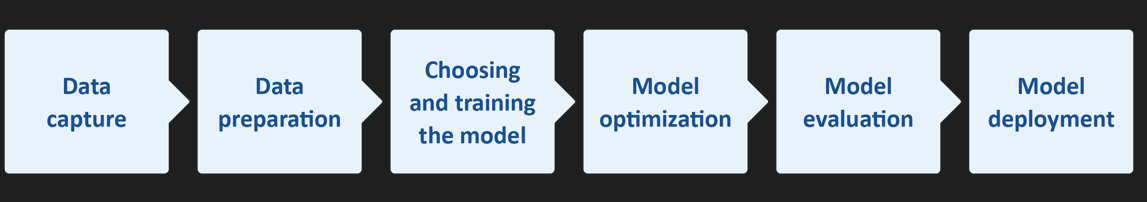

概述:為了在高速采集時不丟失數(shù)據(jù),在數(shù)據(jù)采集系統(tǒng)和

2010-04-16 14:08:36 11881

11881

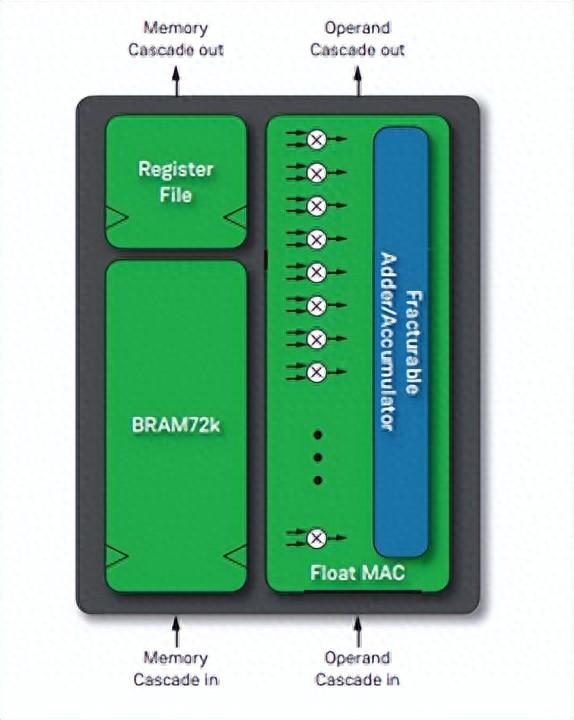

在FPGA獨立芯片上無法實現(xiàn)的功能。利用Speedcore custom blocks定制單元塊,客戶可以獲得ASIC級的效率并同時保持FPGA的靈活性,從而帶來了一種可以將功耗和面積降至最低、同時將數(shù)據(jù)流通量最大化的高效實現(xiàn)方式。

2017-10-19 11:47:25 5818

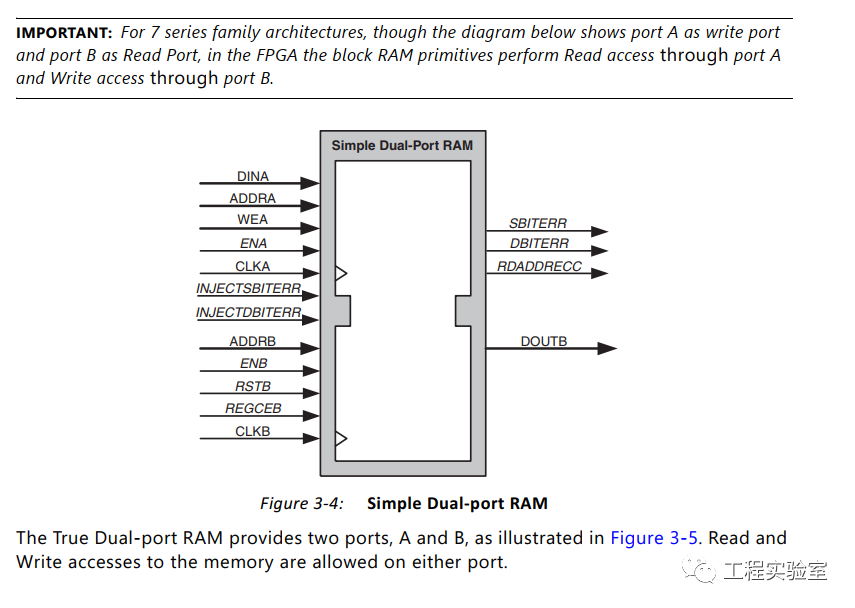

5818 真雙口RAM給設(shè)計帶來很多便利。在高速存儲中,需要對連續(xù)的數(shù)據(jù)同時處理,使用簡單雙口RAM只能讀取一個數(shù)據(jù),而使用真雙口RAM可以同時讀取兩個數(shù)據(jù),這樣明顯提高讀取速度以及處理速度。

2018-06-29 08:54:07 35045

35045

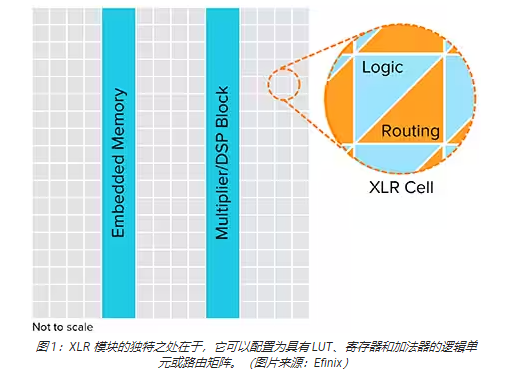

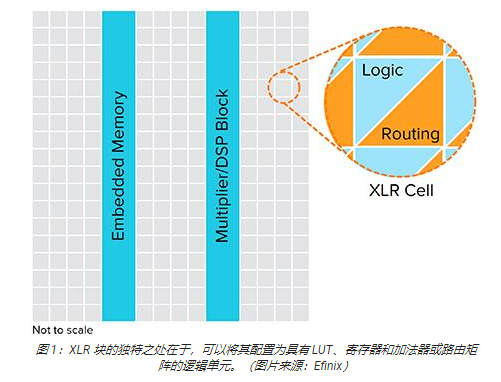

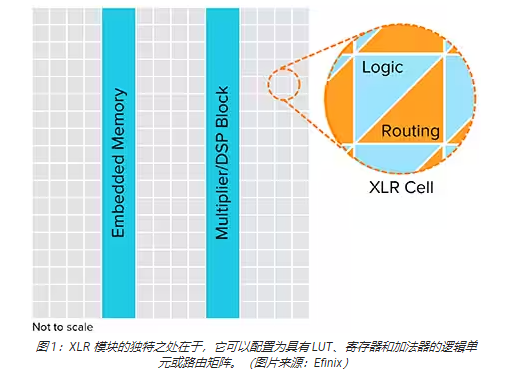

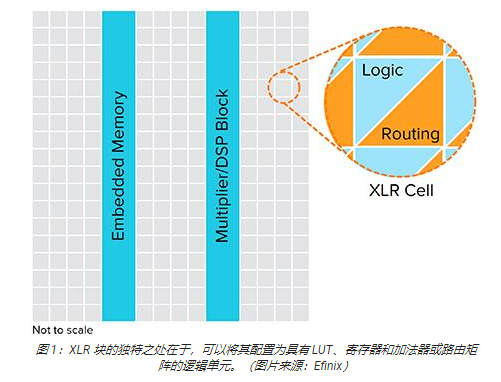

編者按:FPGA 架構(gòu)的新方法帶來了更細(xì)粒度的控制和更大的靈活性,以滿足機器學(xué)習(xí) (ML) 和人工智能 (AI) 的需求。這個由兩部分組成的系列的第 1 部分介紹了 Efinix 的一個這樣的架構(gòu)

2023-04-24 14:49:11 10319

10319

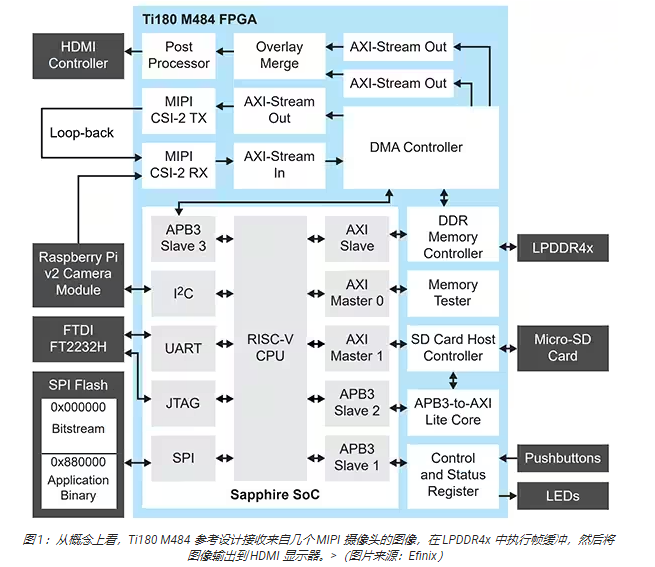

作者:Adam Taylor 編者按:全新的 FPGA 架構(gòu)方法帶來了更精細(xì)的控制和更大的靈活性,以滿足機器學(xué)習(xí) (ML) 和人工智能 (AI) 的需求。本系列文章包括兩部分,第 1部分介紹了

2023-10-03 14:45:00 1715

1715

作者:Adam Taylor 編者按:全新的 FPGA 架構(gòu)方法帶來了更精細(xì)的控制和更大的靈活性,以滿足機器學(xué)習(xí) (ML) 和人工智能 (AI) 的需求。本系列文章包括兩部分,第 1部分介紹了

2023-10-03 14:45:00 1941

1941

Xilinx Block Memory Generator(BMG)是一個先進(jìn)的內(nèi)存構(gòu)造器,它使用Xilinx fpga中的嵌入式塊RAM資源生成面積和 性能優(yōu)化的內(nèi)存。

2023-11-14 17:49:43 4754

4754

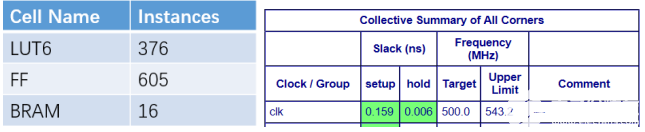

在選擇FPGA時,關(guān)注LUT(Look-Up Table)和BRAM(Block RAM)是非常重要的,因為它們是FPGA架構(gòu)中的兩個核心資源,對于設(shè)計的性能和資源利用至關(guān)重要。

2023-11-21 15:03:06 4794

4794

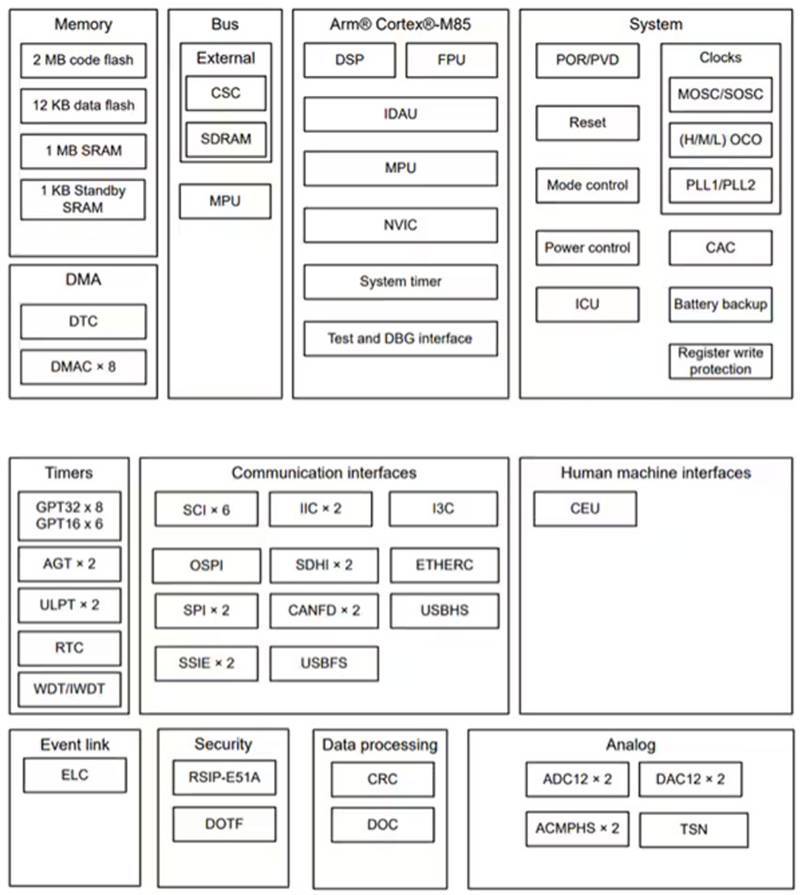

作者:Kenton Williston 人工智能 (AI)、機器學(xué)習(xí) (ML) 和其他計算密集型工作負(fù)載在物聯(lián)網(wǎng)?(IoT) 網(wǎng)絡(luò)邊緣的興起,給微控制器 (MCU) 帶來了額外的處理負(fù)載。處理這些

2024-04-23 15:04:36 2307

2307

【導(dǎo)讀】為了滿足人工智能、機器學(xué)習(xí)、無人駕駛、ADAS等應(yīng)用提出的越來越高的特殊計算需求,Achronix宣布為其eFPGA IP解決方案推出Speedcore定制單元塊,這是一種可以將功耗和面積降至最低、同時將數(shù)據(jù)流通量最大化的解決方案。

2017-10-19 11:28:32 1378

1378 大打折扣,那么如何突破呢? ? 與指令集架構(gòu)不同,數(shù)據(jù)流架構(gòu)的顯著特點就是依托數(shù)據(jù)流的流動次序控制計算執(zhí)行次序,而非指令執(zhí)行次序,因此把它用在AI上可以讓芯片利用率大幅提升,芯片利用率直至逼近?100%。 ? 數(shù)據(jù)流架構(gòu)如何提升芯片利

2021-11-26 07:27:00 5870

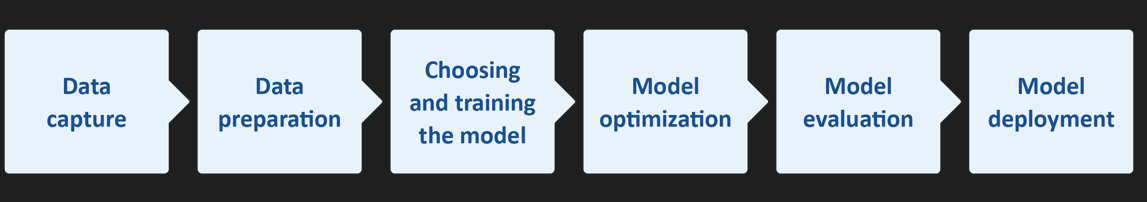

5870 探討了人工智能(AI)的普及給嵌入式設(shè)計人員帶來的新挑戰(zhàn)。在創(chuàng)建“邊緣機器學(xué)習(xí)(ML)”應(yīng)用時,設(shè)計人員必須確保其能有效運行,同時最大限度地降低處理器和存儲開銷,以及物聯(lián)網(wǎng)(IoT)設(shè)備的功耗

2024-08-22 14:20:48 1062

1062

大家好。我設(shè)計并模擬了簡單的RTL with Block RAMin Kintex 7。在合成和實現(xiàn)之后,vivado用于功率估計。當(dāng)我使用分布式RAM時,會正確報告每個RAM的功耗。但是

2019-03-13 14:21:13

制程、異構(gòu)計算、高帶寬內(nèi)存和可重構(gòu)架構(gòu)展開,應(yīng)用領(lǐng)域涵蓋 AI、5G、數(shù)據(jù)中心、自動駕駛和工業(yè)物聯(lián)網(wǎng)。通過優(yōu)化生態(tài)系統(tǒng)、制定有效市場策略、應(yīng)對挑戰(zhàn),FPGA 將在多個領(lǐng)域繼續(xù)發(fā)揮關(guān)鍵作用。

2025-03-03 11:21:28

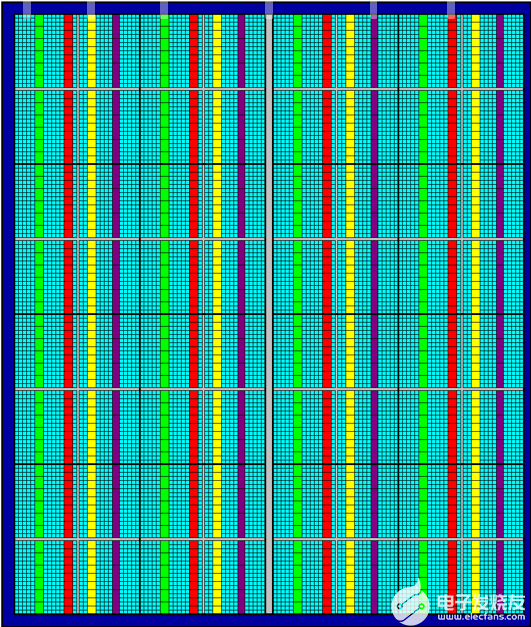

互連線資源(Interconnect)4.嵌入式塊 RAM(BRAM)(Block RAM)5.底層內(nèi)嵌功能單元6.內(nèi)嵌專用硬核7.致謝FPGA 芯片整體架構(gòu)FPGA 芯片整體架構(gòu)如下所示,大體按照...

2021-07-30 08:10:06

各位大神,我最近在做FPGA項目遇到一個問題,我想實現(xiàn)這樣的功能:向RAM里寫一次數(shù)據(jù),再多次讀出來,可是我發(fā)現(xiàn)IP核里的RAM讀第二次的時候RAM數(shù)據(jù)就清零了,根本讀不我寫的數(shù)據(jù),請問有什么好的解決辦法嗎?謝謝啦!

2015-06-07 20:31:57

操作的處理流程為:輸入數(shù)據(jù)流通過“輸入數(shù)據(jù)選擇單元”將數(shù)據(jù)流等時分配到兩個數(shù)據(jù)緩沖區(qū),數(shù)據(jù)緩沖模塊可以為任何存儲模塊,比較常用的存儲單元為雙口RAM(DPRAM)、單口RAM(SPRAM)、FIFO等

2010-11-01 13:17:36

橋接器和一些簡單的UART VHDL代碼通過HyperTerm從FPGA到PC獲取數(shù)據(jù)?我在ML605上看到,Xilinx表示需要實現(xiàn)UART IP,例如XPS UART Lite或UART16550

2019-09-09 06:23:26

的6個原型中運行良好。當(dāng)我連接到FPGA上的參考電壓IO時,其中2個變?yōu)椴煌碾娮柚担虼?b class="flag-6" style="color: red">RAM數(shù)據(jù)流不起作用。我手動手動測試參考電壓引腳以排除出售的問題。在我的工作板上,我在參考電壓電阻12k上測量

2019-06-20 15:21:24

我今天正在實現(xiàn)FIFO,我想知道FIFOPrimitive和Block RAM實現(xiàn)之間的區(qū)別是什么。根據(jù)我的理解,它們使用相同的底層RAM原語,但FIFOPrimitive不能有不同的R / W方面

2019-02-27 14:16:45

實現(xiàn)超高效率的傳質(zhì)及傳熱,安全穩(wěn)定地實現(xiàn)研發(fā)及小試的化工工藝過程。 技術(shù)參數(shù):尺寸:70×70×20mm接頭尺寸:MUNF 1/4”-28螺絲尺寸:M3溫度:-25-230℃壓力:0-100bar建議流通量:50-500mL/min用途:用于工業(yè)化小試及中試生產(chǎn)中的兩相混合,可配合減壓閥一起使用。

2018-06-29 10:45:50

NanoEdge? AI Studio(NanoEdgeAIStudio)是一種新的機器學(xué)習(xí)(ML)技術(shù),可輕松為最終用戶帶來真正的創(chuàng)新。只需幾個步驟,開發(fā)人員就可以基于最少量的數(shù)據(jù)為其項目創(chuàng)建最佳的 ML 庫。

2022-11-29 07:37:53

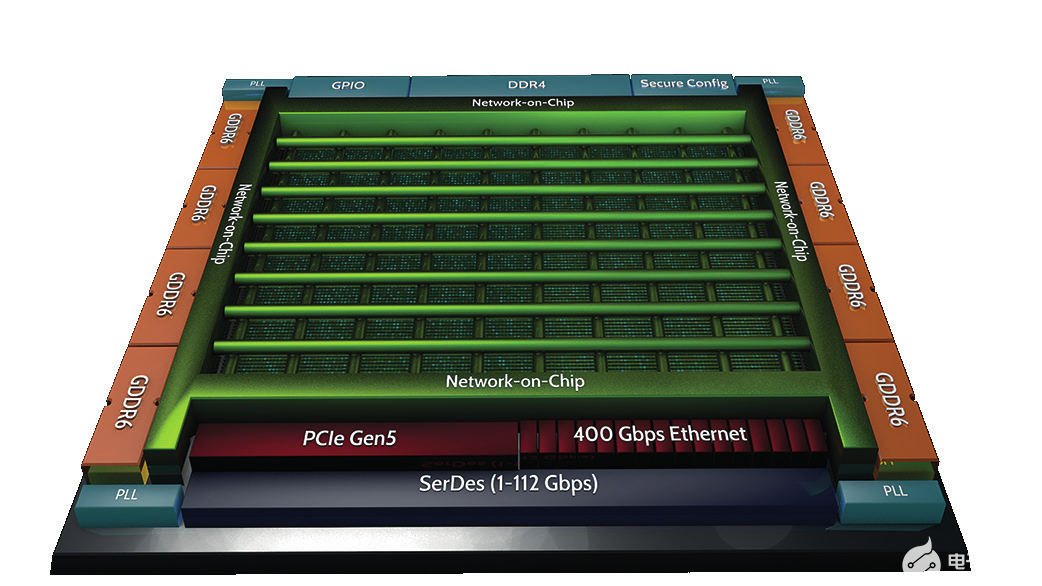

NoC在高端FPGA的應(yīng)用是什么?NoC給Speedster 7t FPGA帶來的優(yōu)勢有哪些?

2021-06-17 11:12:26

嗨,為了調(diào)試系統(tǒng),我需要在系統(tǒng)運行時動態(tài)讀取Block-RAM內(nèi)容....我只有JTAG線,我不能在FPGA中制作一個特定的塊用于讀取內(nèi)容并通過JTAG等發(fā)送它們。我可以使用ISMP 13.2作為

2019-06-11 07:36:08

我想知道 X-CUBE-AI 和 NanoEdge AI Studio 在 ML 和 AI 開發(fā)環(huán)境中的區(qū)別。我可以在任何一個開發(fā)環(huán)境中做同樣的事情嗎?使用的設(shè)備有什么限制嗎?

2022-12-05 06:03:15

RAMB16_S18_S18。我使用一個端口進(jìn)行讀取和寫入(使用寫入啟用),第二個端口僅用于讀取(通過將WEB設(shè)置為0)。兩個端口共享相同的時鐘。 Block RAM設(shè)置為18位寬,但我忽略了奇偶校驗數(shù)據(jù)(即,不使用其輸出值

2019-04-24 07:35:02

首先感謝電子發(fā)燒友論壇提供的書籍和閱讀評測的機會。

拿到書,先看一下封面介紹。這本書的中文名是《AI加速器架構(gòu)設(shè)計與實現(xiàn)》,英文名是Accelerator Based on CNN Design

2023-09-17 16:39:45

CC3200AI實驗教程——瘋殼·開發(fā)板系列AI語音系統(tǒng)架構(gòu)AI語音識別系統(tǒng)的系統(tǒng)架構(gòu)如圖1.0.1所示。圖1.0.1 AI語音系統(tǒng)結(jié)構(gòu) 用戶通過語音采集板卡采集到在駐極體端的語音,通過I2S接口

2022-08-30 14:54:38

CC3200AI實驗教程——瘋殼·開發(fā)板系列AI人臉系統(tǒng)架構(gòu)AI人臉識別系統(tǒng)由7大塊組成,分別是攝像頭、CC3200、串口調(diào)試助手、路由器、公網(wǎng)、服務(wù)器、數(shù)據(jù)庫以及百度AI組成。AI人臉識別系統(tǒng)

2022-08-31 16:35:59

兩方面的問題:①Transformer 模型需要向NVM器件寫入大量數(shù)據(jù)。②傳統(tǒng)內(nèi)存加速器的時序單指令多數(shù)據(jù)流通通道實現(xiàn)這些操作的成本很高。

因此設(shè)計一種既能有效存儲模型參數(shù),又能讓動態(tài)矩陣乘法運算

2025-09-12 17:30:42

本文和設(shè)計代碼由FPGA愛好者小梅哥編寫,未經(jīng)作者許可,本文僅允許網(wǎng)絡(luò)論壇復(fù)制轉(zhuǎn)載,且轉(zhuǎn)載時請標(biāo)明原作者。OV5640提供了一個DVP接口用來輸出采集到的圖像數(shù)據(jù)流,本文提供了一個將DVP接口的圖像

2020-02-18 19:56:10

充分利用了微軟遍布全球數(shù)據(jù)中心的FPGA基礎(chǔ)架構(gòu),使用FPGA解決了AI應(yīng)用中“低延時”和“高帶寬”兩大痛點,并成功構(gòu)建了基于軟核NPU和自定義指令集的實時AI系統(tǒng)。腦波項目的成功實踐,再一次為業(yè)界

2019-08-11 04:00:00

設(shè)計)。如果不考慮維護(hù)性和可測性,調(diào)試成本和壓力就非常之大。通常,FPGA的大部分架構(gòu)設(shè)計可以采用數(shù)據(jù)流驅(qū)動的方式來實現(xiàn),例子1,假設(shè)一個實現(xiàn)視頻解壓縮FPGA的設(shè)計,輸入是無線接口,輸出為顯示屏。那么輸入輸出

2019-08-02 08:30:00

我正在運行Spartan 6 block ram的模擬。時鐘速度為100Mhz。塊ram的寫作運作良好。我可以在內(nèi)存中看到數(shù)據(jù)。但是當(dāng)我讀取數(shù)據(jù)時,輸出有2個時鐘的延遲。在塊ram用戶guidt中

2019-07-25 08:15:27

上面的基本邏輯單元還不夠,多個基本邏輯怎么級聯(lián)?級聯(lián)的連接部分怎么可編程?下圖是FPGA內(nèi)邏輯塊之間互聯(lián)的結(jié)構(gòu)圖。邏輯塊的輸入輸出通過連接塊Connection Block CB和交換塊結(jié)合級聯(lián)到其他

2018-08-21 09:50:44

的CDMA加載權(quán)重,輸入到PL區(qū)的Block Ram。原理框圖首先,我們創(chuàng)建了整個系統(tǒng)的示意圖。有兩個 Block RAW 分別用于存儲輸入特征和權(quán)重數(shù)據(jù)。每個Block RAM 都連接到一個 CDMA

2023-02-21 15:01:58

您好!分布式RAM和Block RAM之間究竟有什么區(qū)別?兩者都只是芯片內(nèi)存,對吧?但我不知道兩者之間的區(qū)別。和..下一個問題.. isaboutMUX ..根據(jù)7系列概述,7系列FPGA支持全范圍

2020-07-19 06:37:51

在我的一個FPGA類中,我被要求使用coregen創(chuàng)建一個blcok ram(8dx16w),單端口ram IP。我在Windows XP,Service Pack 3上使用Xilinx ISE

2019-06-05 13:39:14

一、查找表LUT就是查找表,對于4輸入的LUT而言,實際上就是4位地址位,一位數(shù)據(jù)位的存儲器,能夠存儲16位數(shù)據(jù),所以我們在FPGA設(shè)計中可以用LUT組建分布式的RAM。這樣也可以解釋我們在設(shè)計中

2021-07-28 08:42:17

基于FPGA的超高速FFT硬件實現(xiàn)介紹了頻域抽取基二快速傅里葉運算的基本原理;討論了基于FPGA達(dá)4 096點的大點數(shù)超高速FFT硬件系統(tǒng)設(shè)計與實現(xiàn)方法,當(dāng)多組大點數(shù)進(jìn)行FFT運算時,利用FPGA

2009-06-14 00:19:55

的注意,如果能有意識地利用這些原則指導(dǎo)日后的設(shè)計工作,將取得事半功倍的效果乒乓操作“乒乓操作”是一個常常應(yīng)用于數(shù)據(jù)流控制的處理技巧.乒乓操作的處理流程為:輸入數(shù)據(jù)流通過“輸入數(shù)據(jù)選擇單元”將數(shù)據(jù)流等時分

2020-05-01 07:00:00

RAM是FPGA中常用的基礎(chǔ)模塊,可廣泛用于緩存數(shù)據(jù)的情況,同樣它也是ROM,F(xiàn)IFO的基礎(chǔ)。本實驗將為大家介紹如何使用FPGA內(nèi)部的RAM以及程序?qū)υ?b class="flag-6" style="color: red">RAM的數(shù)據(jù)讀寫操作。1.實驗原理Xilinx

2021-01-07 16:05:28

我們?nèi)绾问褂肰irtex-4 FPGA的Block-RAM來存儲矩陣/ Vector的內(nèi)容。例如,如何在BRAM中存儲矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-27 06:43:47

我們?nèi)绾问褂肰irtex-4 FPGA的Block-RAM來存儲矩陣/ Vector的內(nèi)容。例如,如何在BRAM中存儲矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = 1 2 3 45 6 7 8 9 1 4 5

2020-05-29 09:16:36

我們?nèi)绾问褂肰irtex-4 FPGA的Block-RAM來存儲矩陣/ Vector的內(nèi)容。例如,如何在BRAM中存儲矢量A = [1 2 4 5 6 7 9 3]?OR矩陣B = [1 2 3 45 6 7 8 9 1 4 5 232 1]

2020-05-29 14:41:56

我對在 STM32 上使用 ML 和 AI 很感興趣,在花了一些時間查看 ST 文檔后,我認(rèn)為使用 NanoEdge AI Studio + ST 板是幫助我理解事物的最快方法。據(jù)我所知,ST

2022-12-06 07:35:35

是否可以通過USB將數(shù)據(jù)從我的Spartan 3E FPGA Block RAM發(fā)送到我的計算機?我試圖通過串行RS232發(fā)送數(shù)據(jù),但那不起作用,所以想找到一個發(fā)送數(shù)據(jù)的備用路徑。如果可能的話,那是什么鍛煉?

2019-08-09 09:23:59

我正在嘗試使用virtex 5上的Block RAM來實現(xiàn)延遲線。延遲線需要將數(shù)據(jù)延遲一個時鐘周期。這可能使用Block RAM嗎?我嘗試使用簡單的雙端口RAM,“先讀”作為操作模式。我正在寫一個

2020-06-18 15:40:33

使用AI解決問題提供了第1次經(jīng)驗,但它導(dǎo)致了分散的跨組織的ML算法。不幸的是,這種分散的ML算法不能完全釋放數(shù)據(jù)中隱藏的價值,也不能充分利用組織所擁有的寶貴業(yè)務(wù)知識。此外,它們還會給公司帶來潛在風(fēng)險。分散

2019-05-06 16:46:05

你好,我正在開發(fā)一個在VC709開發(fā)板上使用Virtex7 FPGA的系統(tǒng)。該應(yīng)用程序使用32Mb的板載Block RAM作為設(shè)計中的存儲元件。 FPGA配置序列完成后,有沒有一種方法可以使用PC上的JTAG / USB接口直接寫入和讀取Block RAM的內(nèi)容?謝謝,

2019-09-29 14:00:01

嗨,我正在使用“RAMB16_S36”原始實現(xiàn)一個512內(nèi)存寬度的Block Ram。我通讀了XAPP463用戶指南,但我顯然不了解初始化屬性。INIT_00是否對應(yīng)于[255:0] Block

2019-07-22 08:10:27

] .ram.r / s3a_noinit.ram / dpram.ram有一個有效信號,但沒有連接數(shù)據(jù)輸入引腳。無效數(shù)據(jù)可能會寫入BlockRAM如何更正此錯誤并在bitgen退出之前重復(fù)3次警告

2019-06-04 09:08:32

嗨,我想為我的設(shè)計使用比特流加密,我遇到了一個關(guān)于9K Block RAM的問題,在答案記錄39999中描述了r然后我決定在我的設(shè)計中刪除所有9k Block RAM并將它們更改為16k Block

2019-06-06 07:23:18

賽靈思Virtex-6 HXT FPGA ML630評估套件采用SiTime電子發(fā)燒友振具體型號為:SIT9102AI-243N25E200.0000,而目前針對這一型號sitime推出了抖動更低

2014-11-17 15:07:35

概述EasyGo FPGA Coder Block是嵌入Matlab/Simulink里面的FPGA 仿真工具包軟件。提供了一些基礎(chǔ)的函數(shù)庫以及常用的控制函數(shù)模塊,配合

2022-05-19 09:16:05

分析了西藏的湍流通量數(shù)據(jù)和地表溫度數(shù)據(jù),提出了表征地表溫度變化特征的地表溫度特征量。運用時間序列分析的方法,得到地表溫度特征量和湍流通量之間的傳遞函數(shù)模型,

2009-03-02 22:00:19 22

22 為了在高速采集時不丟失數(shù)據(jù),在數(shù)據(jù)采集系統(tǒng)和CPU之間設(shè)置一個數(shù)據(jù)暫存區(qū)。介紹雙口RAM的存儲原理及其在數(shù)字系統(tǒng)中的應(yīng)用。采用FPGA技術(shù)構(gòu)造雙口RAM,實現(xiàn)高速信號采集系

2010-02-11 11:20:27 69

69 本文提出了一種概率關(guān)聯(lián)規(guī)則算法,通過使用概率的方法估算任意數(shù)據(jù)項集在事務(wù)數(shù)據(jù)庫中出現(xiàn)的概率來求候選頻繁項集,并給出了相關(guān)算法描述及其算法實現(xiàn)。將本算法與Apriori算法

2010-02-25 14:58:44 15

15 基于Actel FPGA 的雙端口RAM 設(shè)計雙端口RAM 芯片主要應(yīng)用于高速率、高可靠性、對實時性要求高的場合,如實現(xiàn)DSP與PCI 總線芯片之間的數(shù)據(jù)交換接口電路等。但普通雙端口RAM 最大

2010-11-15 17:44:19 83

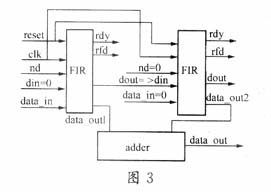

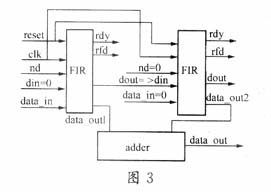

83 【摘 要】 提出了一種基于分布式算法的,采用基于RAM之移位寄存器來設(shè)計可級聯(lián)FIR濾波器的設(shè)計方法。 &

2009-05-11 19:45:52 1285

1285

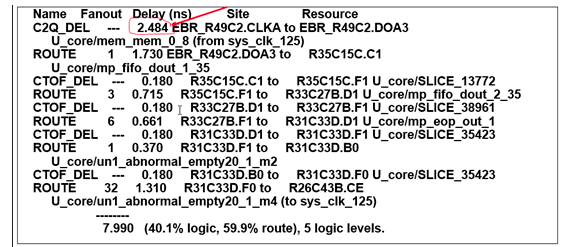

Virtex 型FPGA 芯片是Xilinx 公司芯片系列中的一種,Virtex 系列的數(shù)據(jù)流及配置邏輯與XC4000 的數(shù)據(jù)流及配置邏輯有顯著不同,但卻與Xilinx 的FPGA 家族保持了很大

2017-11-18 11:37:38 2960

2960 FPGA中RAM的使用探索。以4bitX4為例,數(shù)據(jù)位寬為4,深度為4。

2018-03-28 17:07:28 10669

10669

本文介紹了如何在FPGA 中利用Block RAM 的特殊結(jié)構(gòu)實現(xiàn)HDTV視頻增強算法中灰度直方圖統(tǒng)計。

2019-07-10 08:10:00 3489

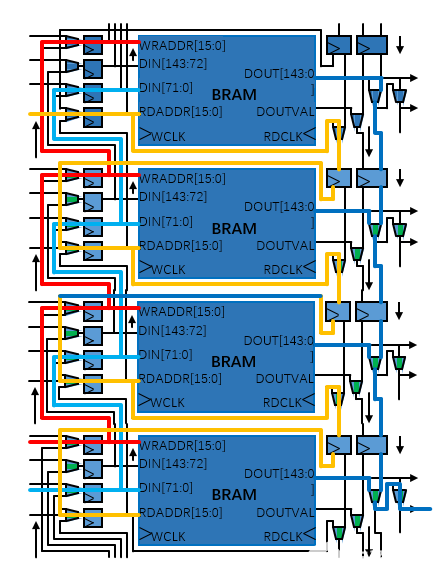

3489 了解新的Block RAM級聯(lián)功能,如何使用它,以及如何利用其功能和性能優(yōu)勢。

2018-11-23 06:56:00 5527

5527 電阻,因為物質(zhì)對電流產(chǎn)生的阻礙作用,所以稱其該作用下的電阻物質(zhì)。電阻將會導(dǎo)致電子流通量的變化,電阻越小,電子流通量越大,反之亦然。沒有電阻或電阻很小的物質(zhì)稱其為電導(dǎo)體,簡稱導(dǎo)體。不能形成電流傳輸?shù)奈镔|(zhì)稱為電絕緣,稱絕緣體。

2019-04-20 09:55:31 57762

57762 某些項目會通過銷毀代幣的方式,減少市場上的流通量,從而給代幣增加價值,比如幣安、火幣都會定期銷毀一部分平臺幣。

2019-08-08 16:25:19 1912

1912 些大材小用,因此xilinx公司在其FPGA內(nèi)部專門集成了很多存儲器模塊,稱作Block RAM,其猶如slice海洋當(dāng)中的一顆顆明珠,專門實現(xiàn)數(shù)據(jù)暫存功能,且每個時鐘區(qū)域都布置了若干個Block

2020-11-23 14:08:43 9097

9097

的寄存器輸出,你要同時檢查數(shù)據(jù)流的時序關(guān)系是否正確。在修改了時序關(guān)系后,可以按照我們之前的介紹,在GUI里使能Block RAM的輸出

2021-03-26 15:50:27 2302

2302

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的RAM存儲資源詳細(xì)資料說明包括了:1、 FPGA存儲資源簡介,2、 不同廠家的 Block RAM 布局,3、 塊 RAM 和分布式 RAM 資源,4、 Xilinx Block RAM 架構(gòu)及應(yīng)用

2020-12-09 15:31:00 11

11 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA硬件基礎(chǔ)之FPGA的RAM存儲課件和工程文件。

2020-12-10 15:27:00 31

31 在FPGA中block ram是很常見的硬核資源,合理的利用這些硬件資源一定程度上可以優(yōu)化整個設(shè)計,節(jié)約資源利用率,充分開發(fā)FPGA芯片中的潛在價值,本文結(jié)合安路科技FPGA做簡單總結(jié),說明基本原理。

2020-12-24 14:28:09 1893

1893 FPGA可以調(diào)用分布式RAM和塊RAM兩種RAM,當(dāng)我們編寫verilog代碼的時候如果合理的編寫就可以使我們想要的RAM被綜合成BRAM(Block RAM)或者DRAM(Distributed

2020-12-30 16:27:52 9

9 RAM是FPGA中常用的基礎(chǔ)模塊,可廣泛用于緩存數(shù)據(jù)的情況,同樣它也是ROM,F(xiàn)IFO的基礎(chǔ)。本實驗將為大家介紹如何使用FPGA內(nèi)部的RAM以及程序?qū)υ?b class="flag-6" style="color: red">RAM的數(shù)據(jù)讀寫操作。

2022-02-08 15:50:49 16172

16172

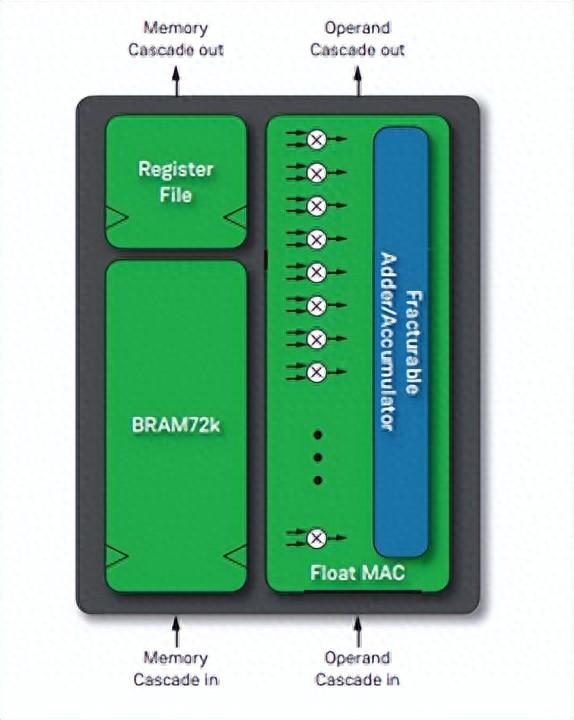

外圍IP超高帶寬需求。本文首先談?wù)凷peedster7t FPGA的片上SRAM,也就是Block RAM針對傳統(tǒng)的結(jié)構(gòu)所做出的一些優(yōu)化。

2022-07-05 15:37:41 1777

1777 (人工智能)和ML(機器學(xué)習(xí))的日益普及開辟了一個充滿可能性的新世界,PC廠商和生態(tài)系統(tǒng)巨頭都在尋求將這些先進(jìn)的新功能添加到其產(chǎn)品功能集中。 在本篇博文中,萊迪思將討論PC中AI/ML功能的增長趨勢,為什么FPGA非常適合實現(xiàn)這些新

2022-09-08 17:19:25 1688

1688 在 FPGA 上實施 AI/ML 的選項

2022-12-28 09:51:08 1424

1424 使用 AMD-Xilinx FPGA設(shè)計一個全連接DNN核心現(xiàn)在比較容易(Vitis AI),但是利用這個核心在 DNN 計算中使用它是另一回事。本項目主要是設(shè)計AI加速器,利用Xilinx的CDMA加載權(quán)重,輸入到PL區(qū)的Block Ram。

2023-02-08 09:33:09 3497

3497 本文主要講述了Speedster7t FPGA的片上SRAM,也就是Block RAM針對傳統(tǒng)的結(jié)構(gòu)所做出的一些優(yōu)化。

2023-07-13 17:24:15 950

950

ai芯片技術(shù)可以分為不同的體系架構(gòu)。下面將對ai芯片技術(shù)架構(gòu)做詳細(xì)介紹。 首先,ai芯片技術(shù)架構(gòu)可以分為顯卡、TPU和FPGA三類。顯卡是目前ai應(yīng)用中使用最為廣泛的一種芯片。nvidia公司推出的GTX和tesla系列顯卡擁有超高的并行運算能力,

2023-08-09 14:28:47 3045

3045 虹科方案1AI&ML變革日常生活AI(人工智能)和ML(機器學(xué)習(xí))的發(fā)展正逐漸滲透到我們的日常生活中,為我們帶來了翻天覆地的變化。從智能手機中的語音助手到智能家居設(shè)備,AI的應(yīng)用讓我們的生活

2023-08-05 08:11:03 1181

1181

在FPGA 邏輯設(shè)計中經(jīng)常用到的數(shù)據(jù)存儲方式有ROM、RAM和FIFO,根據(jù)不同的應(yīng)用場景選擇不同的存儲方式。Xilinx 平臺三種存儲方式在使用過程中的區(qū)別如下。

2023-08-22 16:12:47 6152

6152

設(shè)計都涉及到對RAM的讀寫操作。在FPGA芯片中,RAM也叫做存儲塊(Block RAM),可以存儲大量的數(shù)據(jù)。 FPGA中的RAM可以一次讀取多個數(shù)據(jù),這是因為RAM的結(jié)構(gòu)是一個多列的數(shù)據(jù)表格,其中每一列都是一個包含多個存儲單元的塊。通過在時鐘的一次上升沿來讀取RAM中的數(shù)據(jù),這個操作必須在一個

2023-10-18 15:28:20 1986

1986 二是明晰 TDN 的可信數(shù)據(jù)流通關(guān)鍵技術(shù)范疇。從保障數(shù)據(jù)隱私安全、流通過程可控可信、跨節(jié)點跨平臺跨技術(shù)互聯(lián)互通等角度歸納、分析實現(xiàn)數(shù)據(jù)可信流通的關(guān)鍵技術(shù)方法。

2023-11-06 16:50:24 2696

2696

2024年2月29日,是德科技(Keysight Technologies,Inc.)宣布,針對人工智能(AI)和機器學(xué)習(xí)(ML)基礎(chǔ)設(shè)施生態(tài)系統(tǒng),推出了 AI數(shù)據(jù)中心測試平臺,旨在加速AI / ML網(wǎng)絡(luò)驗證和優(yōu)化的創(chuàng)新。

2024-02-29 09:32:49 1356

1356

FPGA雙口RAM的使用主要涉及配置和使用雙端口RAM模塊。雙端口RAM的特點是有兩組獨立的端口,可以對同一存儲塊進(jìn)行讀寫操作,從而實現(xiàn)并行訪問。

2024-03-15 13:58:14 2071

2071 的來臨,而是包括GPU、FPGA和NPU等一眾數(shù)據(jù)處理加速器時代的來臨,就像GPU以更高的計算密度和能效勝出CPU一樣,各種加速器件在不同的AI/ML應(yīng)用或者細(xì)分市場中將各具優(yōu)勢,未來并不是只要貴的而是更需要對的。 此次GTC上新推出的用于AI/ML計算或者大模型的B200芯片有一個顯

2024-04-02 15:25:31 834

834

FPGA 的分布式 RAM(Distributed RAM)或塊 RAM(Block RAM)資源,創(chuàng)建一個可配置的移位寄存器,支持用戶定義的寬度和深度,適用于需要數(shù)據(jù)延遲、數(shù)據(jù)緩沖或流水線處理的場景

2025-05-14 09:36:22 913

913 日前,在2025年“數(shù)據(jù)要素×”大賽全國總決賽頒獎儀式暨2025全球數(shù)商大會開幕式上,國家數(shù)據(jù)局正式發(fā)布了第二批數(shù)據(jù)流通安全治理典型案例,四維圖新“基于智駕數(shù)據(jù)閉環(huán)應(yīng)用場景的汽車數(shù)據(jù)流通安全技術(shù)應(yīng)用案例”成功入選。

2025-12-11 16:52:22 1165

1165

電子發(fā)燒友App

電子發(fā)燒友App

評論