本文作者陳雯,Tools Product Applications Engineer, WTS China.

本文給想直接使用Vitis HLS 工具在 Standalone 模式下調用 Xilinx Vision Library L1 API 的小伙伴提供了一個非常容易上手的腳本文件。

在論壇上遇到在高層次綜合工具中調用視覺庫遇到的大多數問題都和 opencv 庫以及Xilinx Vision 庫的安裝路徑有關,如今 Vitis HLS 2020.1 之后的版本都不再提供OpenCV 的預編譯庫,就更需要開發者們將各自工作環境中的庫路徑,環境變量都設置好。希望這篇博文能給大家調用 Vitis Vision Library 提供向導,提升效率。

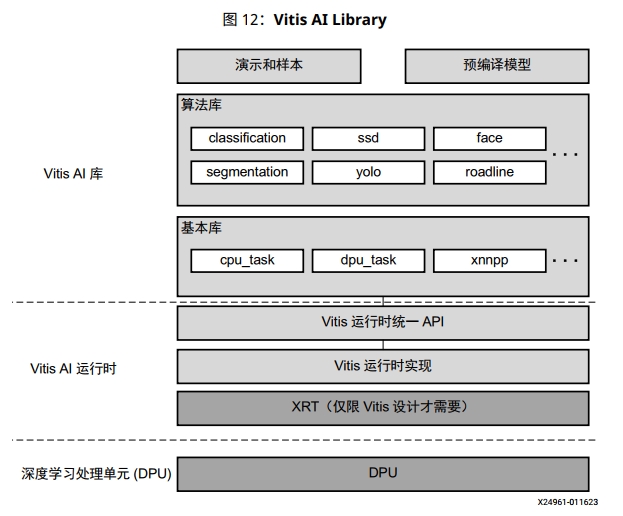

Vitis Vision庫

Vitis Vision 庫是 Xilinx 官方將 Opencv 功能轉換至易于在 FPGA 中部署的視覺加速庫,可在Vitis 環境中實施。其中 Vitis Vision 庫的 L1 目錄提供了在 Vitis HLS 層級部署的應用實例設計。這個實例設計中 C-sim 的流程中需要調用 OpenCV 用于測試平臺功能,因此需要現有的OpenCV 安裝。

Vitis Vision庫:

https://github.com/Xilinx/Vitis_Libraries/tree/master/vision

為了適應各種用戶環境,從2020.1版本開始,Xilinx 不再提供帶有 Vivado / Vitis 工具的OpenCV 的預安裝版本。盡管 Vitis 在綜合布局布線Vision庫的流程中不需要 OpenCV,但是運行示例設計仿真是必需的。

本文使用 Vitis 2020.2 版本介紹了如何創建獨立的 Vitis HLS TCL 文件,用戶只要在將該 tcl腳本拷貝在 Vision Lirary 的實例目錄中,即可在命令行模式下跑完 Vitis_HLS C仿真,綜合,聯合仿真以及導出 IP 等全部流程。

Vision 的官方文檔中包含使用 Vitis HLS standalone 模式的教程,該信息位于以下位置:

https://github.com/Xilinx/Vitis_Libraries/blob/master/vision/docs/gettin...

https://xilinx.github.io/Vitis_Libraries/vision/2020.1/index.html#

要利用示例設計或在用戶測試平臺中引用 OpenCV 庫,必須執行以下步驟:

-安裝 OpenCV 工具版本3.x

OpenCV 在Linux 的安裝和環境設置請參考附錄A, 在 Windows 環境下建議使用 Mingw 編譯Opencv 安裝包。

-設置環境變量以引用 OpenCV 安裝路徑

-下載 Vitis Version library

-創建 TCL 腳本并在 Vitis HLS 命令行執行

注意:2020.1 Vitis Vision 庫已使用 OpenCV 庫的3.3版進行了驗證。比該版本更新的任何版本都可以使用,但是,版本4.x可能相對于3.x版本具有庫功能更改,可能需要修改示例設計測試平臺。因此,建議使用 OpenCV 3.x 版運行示例設計。OpenCV 庫僅提供測試平臺功能,不是必需的,并且不會以任何方式影響 Vision 內核的實現。

環境設置

Linux 環境變量設置要求:

source /settings64.sh source /setup.sh export DEVICE=/.xpfm

export OPENCV_INCLUDE=

export OPENCV_LIB=

export LD_LIBRARY_PATH=$LD_LIBRARY_PATH:

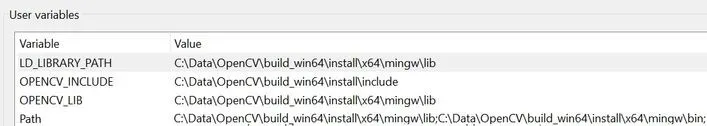

Windows 環境變量設置要求:

示例如下所示,并且每個用戶的設置會有所不同,具體取決于 OpenCV 和編譯器工具的安裝目錄。

注意:必須在用戶的環境中正確設置 LD_LIBRARY_PATH 動態庫的搜索路徑環境變量和OpenCV PATH 信息,此腳本和 Vitis Vision 示例設計才能正常工作。此外,OpenCV 的包含庫和二進制文件的路徑必須包含在系統的環境變量中。否則,將導致仿真期間庫包含錯誤。

操作步驟

要運行 Vitis HLS tcl 腳本,請執行以下操作:

-將修改好的 tcl 腳本放在

/ vision / L1 / example / resize 目錄中

-打開 Vitis HLS 命令行外殼并 cd

/ vision / L1 / example / resize 目錄

-運行以下命令:vitis_hls -f run_hls_standalone.tcl

Vitis HLS TCL腳本詳細解釋

該AR提供了一個 TCL 腳本,用于在 makefile 流之外運行 L1 調整大小示例設計。該腳本基于Windows 環境。該腳本基于以下環境設置:

-OpenCV 版本3.4.11

Linux:

set XF_PROJ_ROOT"/home/vicky/Xilinx/Vitis_Libraries-master/vision"

set OPENCV_INCLUDE"/home/vicky/opencv/include"

set OPENCV_LIB"/home/vicky/opencv/lib"

Windows:

- OpenCV include directory :C:/Data/OpenCV/build_win64/install/include

- OpenCV library directory :C:/Data/OpenCV/build_win64/install/x64/mingw/lib

- Vitis Vision Directory :C:/Data/Vitis_Libraries/Vitis_Libraries-master/vision/

TCL腳本文件包含以下部分,本文將逐一介紹

· 代表 OpenCV 和項目環境的變量聲明

· 項目創建命令

· 使用 Vitis Vision 庫添加設計文件包括路徑

· 使用 OpenCV 和 VitisVision 庫添加 Testbench 文件包括路徑

· 使用 OpenCV 鏈接器參考進行 C 仿真

· Vitis HLS IP 綜合

· 具有 OpenCV 鏈接器參考的 RTL 協同仿真

· 導出IP

1. 變量聲明:

變量聲明部分的第一部分聲明了一些變量,這些變量復制makefile流和該流生成的settings.tcl文件的環境變量。這些變量指向 Vitis Vision Includes,OpenCV 頭文件和 OpenCV預編譯的庫。這些位置可能會根據用戶系統的安裝路徑而有所不同。

設置 XF_PROJ_ROOT“ C:/ Data / Vitis_Libraries / Vitis_Libraries-master / vision” #Vitis Vision庫的包含目錄

設置 OPENCV_INCLUDE“ C:/ Data / OpenCV / build_win64 / install /include” #OpenCV頭文件目錄

設置 OPENCV_LIB“ C:/ Data / OpenCV / build_win64 / install / x64 /mingw / lib” #OpenCV 編譯的庫目錄

下一個變量聲明部分有助于創建 Vitis HLS 項目,并有助于使腳本可移植:

· 設置 PROJ_DIR“ $ XF_PROJ_ROOT /L1 / examples / resize”

· 設置 SOURCE_DIR“ $ PROJ_DIR /”

· 設置 PROJ_NAME“ hls_example”

· 設置 PROJ_TOP“ resize_accel”

· 設置 SOLUTION_NAME“ sol1”

· 設置 SOLUTION_PART“xcvu11p-flgb2104-1-e”

· 設置 SOLUTION_CLKP 5

最后,最后一部分聲明變量,這些變量表示 HLS 引用和使用庫所需的引用路徑和標志。這里我們發現在一個易用性高的腳本中,使用變量而不是代碼有助于理解如何使用這些選項。

設置 VISION_INC_FLAGS“ -I $XF_PROJ_ROOT / L1 / include -std = c ++ 0x”#Vitis Vision 包含路徑和 C ++ 11 設置

設置 OPENCV_INC_FLAGS“ -I $OPENCV_INCLUDE”#OpenCV 包含目錄引用

設置 OPENCV_LIB_FLAGS“ -L $OPENCV_LIB”#OpenCV 庫參考

注意:

在 Windows 中,庫引用必須包含版本號。本示例使用 OpenCV 3.4.11安裝。精確的包含格式將取決于用戶的安裝,并且可能與下面列出的格式不同。

設置 OPENCV_LIB_REF“ -lopencv_imgcodecs3411-lopencv_imgproc3411 -lopencv_core3411 -lopencv_highgui3411 -lopencv_flann3411-lopencv_features2d3411”

在 Linux include 語句不使用版本號,并給出如下:

設置 OPENCV_LIB_REF“-lopencv_imgcodecs -lopencv_imgproc -lopencv_core -lopencv_highgui -lopencv_flann-lopencv_features2d”

2. 項目創建:

項目創建部分非常簡單,它會創建一個新的項目目錄和項目文件:

open_project -reset$PROJ_NAME

設計文件包括:

設計文件已添加到本節中的設計中。該命令:

-引用單個HLS內核文件:add_files“ $ {PROJ_DIR} /xf_resize_accel.cpp”

-引用 Vision 庫和特定于項目的包含合成目錄:-cflags“ $ {VISION_INC_FLAGS} -I $ {PROJ_DIR} /build

-引用了用于 C 仿真的Vision庫和特定于項目的包含目錄:-csimflags“ $ {VISION_INC_FLAGS} -I $ {PROJ_DIR}/ build”

完整的命令如下所示:

add_files“ $ {PROJ_DIR}/xf_resize_accel.cpp” -cflags“ $ {VISION_INC_FLAGS} -I $ {PROJ_DIR} / build”-csimflags“ $ {VISION_INC_FLAGS} -I $ {PROJ_DIR} / build”

Testbench 文件包括:

testbench 文件將在本節中添加到設計中。命令:

-引用 Test bench 文件:add_files -tb“ $ {PROJ_DIR} /xf_resize_tb.cpp”

-引用 Vision 庫和特定于項目的包含目錄:-cflags“ $ {OPENCV_INC_FLAGS} $ {VISION_INC_FLAGS} -I $ {PROJ_DIR}/ build”

-引用 Vision 庫和特定于項目的 C 仿真目錄:-csimflags“ $ {OPENCV_INC_FLAGS} $ {VISION_INC_FLAGS} -I $ {PROJ_DIR} /build”

請注意,在測試臺標志和設計文件標志中添加了$ {VISION_INC_FLAGS}變量。此設置引用OpenCV 包含文件。

完整的命令如下所示:

add_files -tb“ $ {PROJ_DIR}/xf_resize_tb.cpp” -cflags“ $ {OPENCV_INC_FLAGS} $ {VISION_INC_FLAGS} -I ${PROJ_DIR} / build” -csimflags“ $ {OPENCV_INC_FLAGS} $ {PROSION_IN /建立”

3. 項目設置:

現在已經添加了所有需要的 C 源文件,執行項目創建的最后一步。這些命令設置 HLS IP 的頂層函數,并創建一個所需的項目solution。

set_top $ PROJ_TOP#設置HLS IP的頂級文件

open_solution -reset $SOLUTION_NAME#創建項目解決方案

set_part $ SOLUTION_PART#設置解決方案部分

create_clock -period $SOLUTION_CLKP#設置項目目標時鐘周期

4. c-sim:

本部分通過將 HLS IP 和 Testbench 設計發送給編譯器進行編譯和執行,來執行 HLS 流的 C仿真階段。此命令用于設置編譯器鏈接器標志和 testbench 文件,以及:

-引用 OpenCV包含和預編譯的庫目錄:-ldflags“ -L $ {OPENCV_LIB} $ {OPENCV_LIB_REF}”

-包括用于驗證測試臺的圖像作為主要功能的參數:-argv“ $ {XF_PROJ_ROOT} /data/128x128.png”

完整的命令如下所示:

csim_design -ldflags“ -L ${OPENCV_LIB} $ {OPENCV_LIB_REF}” -argv“ $ {XF_PROJ_ROOT} /data/128x128.png”

5. C到RTL綜合:

本部分執行 Vitis HLS C 到 RTL 合成階段。此階段不需要標志或選項。

csynth_design

6. C/RTL協同仿真:

本部分在合成后執行 Vitis HLS IP的 RTL 協同仿真。HLS 會自動根據 C test bench 生成RTLtestbench 進行協同仿真,以下指令用于設置編譯器鏈接器標志和 testbench 文件,以及:

-引用 OpenCV包含和預編譯的庫目錄:-ldflags“ -L $ {OPENCV_LIB} $ {OPENCV_LIB_REF}”

-包括用于驗證測試平臺的圖像:-argv“ $ {XF_PROJ_ROOT} /data/128x128.png”

完整的命令如下所示:

cosim_design -ldflags“ -L ${OPENCV_LIB} $ {OPENCV_LIB_REF}” -argv“ $ {XF_PROJ_ROOT} /data/128x128.png”

7. 導出IP:

Vitis HLS 流程的最后階段是設計的輸出。本示例導出RTL的設計并運行 Vivado Synthesis,以獲取準確的資源利用率和估計的時序結果。

export_design -flow syn -rtlverilog

注意:導出 RTL 的設計并運行 Vivado Synthesis 進行布局布線的過程需要在 Vivado 工具中先載入有效的 license

附件為在 Ubuntu 18.04 版本在 2020.2 上運行成功的 tcl shell, 大家可以下載后稍作修改,根據本文流程在自己的環境中進行實驗,有問題歡迎在本帖下方留言。

?

附錄A -掃碼下載并安裝OpenCVon Linux

1. 打開一個終端,先不要執行任何有關 Vivado 或 Vitis 的 set up 指令, 否則 CMake 會失敗.

2. 按照自己的意愿在 Home 創建一個 home 目錄下的 opencv 目錄 –> for instance: cd ~/src_opencv

3. git clone --branch 3.4.11 https://github.com/opencv/opencv.git

creates sub-folder “opencv” with the source files –> ~/src_opencv/opencv

4. git clone --branch 3.4.11 https://github.com/opencv/opencv_contrib.git

creates sub-folder “opencv_contrib” with the sourcefiles –> ~/src_opencv/opencv_contrib

5. mkdirbuild -> this will create a sub-folder “build” ->~/src_opencv/build

6. cd build

7.跑以下指令去生成編譯 OpenCV library 的 makefile:

cmake -DCMAKE_BUILD_TYPE=Release-OPENCV_EXTRA_MODULES_PATH=~/src_opencv/opencv_contrib/modules -DCMAKE_INSTALL_PREFIX=~/opencv ~/src_opencv/opencv

8. From the “build” directory 輸入以下兩個指令

make -j7

make install

9. 編譯安裝完成后,你就會看到 Opencv 庫在以下路徑中 ~/opencv

電子發燒友App

電子發燒友App

評論