Xilinx FIR IP的介紹與仿真

1 xilinx fir ip 簡(jiǎn)介

1)符合 AXI4-Stream 的接口

2)高性能有限脈沖響應(yīng)(FIR),多相抽取器,多相內(nèi)插器,半帶,半帶抽取器和半帶內(nèi)插器,希爾伯特變換和內(nèi)插濾波器實(shí)現(xiàn)

3)最多支持 256 組系數(shù),處理一組以上時(shí),每組 2 至 2048 個(gè)系數(shù)。

4)輸入數(shù)據(jù)高達(dá) 49 位精度

5)濾波器系數(shù)高達(dá) 49 位精度

6)支持多達(dá) 1024 個(gè)交錯(cuò)數(shù)據(jù)通道

7)支持高級(jí)交錯(cuò)數(shù)據(jù)通道序列

8)通過(guò)共享控制邏輯支持多個(gè)并行數(shù)據(jù)通道

9)插值和抽取因子通常最多為 64,單通道濾波器的最大為 1024

10)支持大于時(shí)鐘頻率的采樣頻率

11)在線系數(shù)重裝能力

12)用戶可選的輸出舍入

13)高效的多列結(jié)構(gòu),適用于所有過(guò)濾器的實(shí)現(xiàn)和優(yōu)化

Fir 公式

常規(guī)抽頭延遲線 FIR 濾波器表示

2設(shè)計(jì)驗(yàn)證思路

混頻模塊內(nèi)部包含兩個(gè) dds 模塊,一個(gè)產(chǎn)生 2khz sine 波,一個(gè)產(chǎn)生 3khz sine 波,然后相乘得到 1khz+6khz 的混頻,然后使用 xilinx FIR IP 設(shè)計(jì)一個(gè)低通濾波器濾掉 6khz,最后只剩 1khz。

3 matlab fdatool 設(shè)計(jì)低通濾波器

1)打開 fdatool

2)低通濾波器設(shè)計(jì)

Fs=44100;

Fpass =3000;

Fstop =5000;

Apass = 1;

Astop =120;

3系數(shù)量化

4)matlab 導(dǎo)出.coe

4 xilinx FIR IP的設(shè)置與仿真

左側(cè)包含 IP Symbol、Freq.Response、Implementation Details 和 CoefficientReload。右側(cè)包括 Filter Options、Channel Specification、Implementation、Detailed Implementation、Interface 和 Summary.

1)Filter Options

(1)系數(shù)源(Coefficient Source):直接在 GUI 中使用系數(shù)矢量參數(shù)或使用由 CoefficientFile 參數(shù)指定的 .coe 文件,指定要使用的系數(shù)輸入。

(2)系數(shù)向量(Coefficient Vector ):用于直接在 GUI 中指定濾波器系數(shù)。過(guò)濾器系數(shù)使用逗號(hào)分隔列表以十進(jìn)制形式指定,與過(guò)濾器系數(shù)數(shù)據(jù)文件中的 coefdata 字段相同。與 .coe 文件一樣,可以使用 FIR 編譯器根據(jù)您的要求適當(dāng)量化的非整數(shù)實(shí)數(shù)來(lái)指定濾波器系數(shù)。

(3)濾波器類型(Filter Typ ):支持五種濾波器類型:?jiǎn)嗡俾?FIR,插值 FIR,抽取 FIR,希爾伯特變換和插值 FIR。

2)Channel Specification

(1)選擇格式(Select format ):選擇用于指定硬件過(guò)采樣率,內(nèi)核可用于處理輸入采樣并生成輸出的時(shí)鐘周期數(shù)的格式。該值直接影響核心實(shí)現(xiàn)和所使用資源的并行度。選擇“頻率規(guī)格”后,可以指定“輸入采樣頻率”和“時(shí)鐘頻率”。這些值之間的比率以及其他核心參數(shù)決定了硬件過(guò)采樣率。

選擇“輸入采樣周期”時(shí),可以指定輸入采樣之間的時(shí)鐘周期數(shù)。同樣,選 擇“輸出采樣周期”時(shí),可以指定輸出采樣之間的時(shí)鐘周期數(shù)。

(2)采樣周期(Sample Period ):輸入或輸出采樣之間的時(shí)鐘周期數(shù)。當(dāng)指定了多個(gè)通道時(shí),該值應(yīng)該是時(shí)分多路復(fù)用輸入樣本數(shù)據(jù)流之間時(shí)鐘周期的整數(shù)。可以使用分?jǐn)?shù)采樣周期來(lái)指定大于時(shí)鐘頻率的采樣頻率 .

(3)輸入采樣頻率(Input Sampling Frequency ):該字段可以是整數(shù)或?qū)崝?shù)值;它指定一個(gè)通道的采樣頻率。根據(jù)時(shí)鐘頻率和濾波器參數(shù)(例如插值率和通道數(shù))設(shè)置上限。

(4)時(shí)鐘頻率(Clock Frequency ):此字段可以是整數(shù)或?qū)崝?shù)值。限制是根據(jù)采樣頻率,內(nèi)插率和通道數(shù)設(shè)置的。該領(lǐng)域僅影響體系結(jié)構(gòu)選擇。最終的實(shí)現(xiàn)可能無(wú)法達(dá)到指定的時(shí)鐘速率。

3) Implementation

(1)系數(shù)類型(Coefficient Type ):系數(shù)數(shù)據(jù)可以指定為有符號(hào)或無(wú)符號(hào)。

(2)輸入數(shù)據(jù)小數(shù)位(Input Data Fractional Bits ):用于表示過(guò)濾器輸入數(shù)據(jù)樣本的小數(shù)部分的輸入數(shù)據(jù)寬度位數(shù)。該字段僅供參考。它與系數(shù)小數(shù)位一起使用,以計(jì)算濾波器的輸出小數(shù)位值。此參數(shù)在 IP 集成器中自動(dòng)設(shè)置,但也可以被覆蓋。

(3)輸出舍入模式(Output Rounding Mode ):指定要應(yīng)用于過(guò)濾器輸出的舍入類型。

(4)輸出小數(shù)位(Output Fractional Bits ):此字段報(bào)告用于表示濾波器輸出樣本小數(shù)部分的輸出寬度位數(shù)

4) Interface

5) Freq.Response

將混頻信號(hào)和經(jīng)過(guò) xilinx FIR IP濾波后信號(hào)寫出 matlab 觀察時(shí)域和頻域 .

1混頻信號(hào)

濾波前的 1khz+6khz 的混頻信號(hào)。

2濾波后

如上所示,經(jīng)過(guò)濾波后 6khz 完全被濾除,只剩下 1khz 信號(hào)。仿真驗(yàn)證成功。

審核編輯 黃昊宇

-

FIR

+關(guān)注

關(guān)注

4文章

152瀏覽量

35510 -

仿真

+關(guān)注

關(guān)注

54文章

4482瀏覽量

138255

發(fā)布評(píng)論請(qǐng)先 登錄

SOME/IP 節(jié)點(diǎn)仿真測(cè)試方案推薦:智能車載網(wǎng)絡(luò)驗(yàn)證的關(guān)鍵支撐

一文詳解SystemC仿真庫(kù)的編譯

Xilinx FPGA串行通信協(xié)議介紹

【產(chǎn)品介紹】Modelsim:HDL語(yǔ)言仿真軟件

小白也能輕松上手!一招解決IP被封殺難題

vivado仿真時(shí)GSR信號(hào)的影響

智多晶SerDes 2.0 IP介紹

FPGA利用DMA IP核實(shí)現(xiàn)ADC數(shù)據(jù)采集

Xilinx Shift RAM IP概述和主要功能

基于 FPGA 的任意波形發(fā)生器+低通濾波器系統(tǒng)設(shè)計(jì)

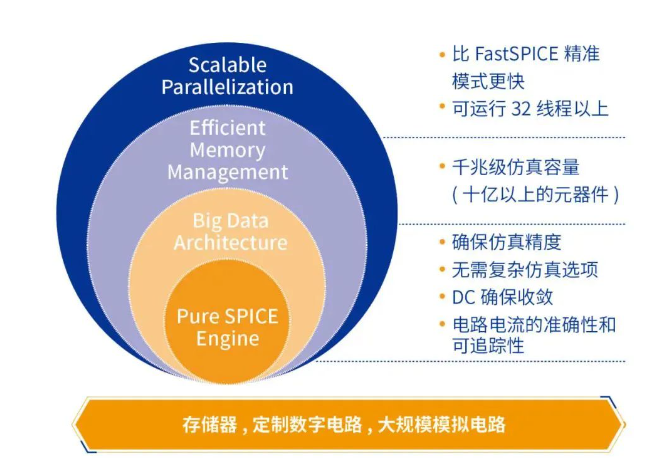

概倫電子千兆級(jí)高精度電路仿真器NanoSpice Giga介紹

詳解Xilinx的10G PCS PMA IP

深入解讀智多晶FIR IP

博世GTM IP模塊架構(gòu)介紹

Xilinx FIR IP的介紹及仿真

Xilinx FIR IP的介紹及仿真

評(píng)論