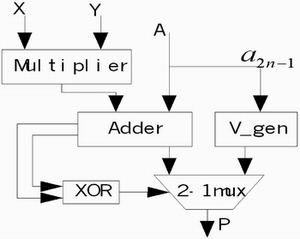

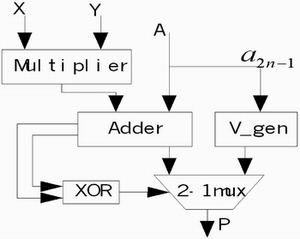

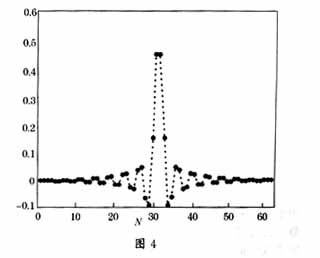

根據BPSK調制信號調制機理和平方倍頻法原理,在FPGA平臺上設計實現了BPSK調制信號載波頻率估計單元。

2014-09-01 11:26:40 3313

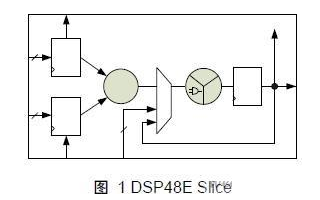

3313 本文系統(tǒng)的實現主要用到了兩類邏輯資源來優(yōu)化系統(tǒng)性能:DSP48E Slice:25x18位二進制補碼乘法器能產生48位全精度結果。此功能單元還能夠實現諸多DSP模塊如乘累加器、桶形移位器、寬總線多路復用器等。

2020-09-03 12:45:22 892

892

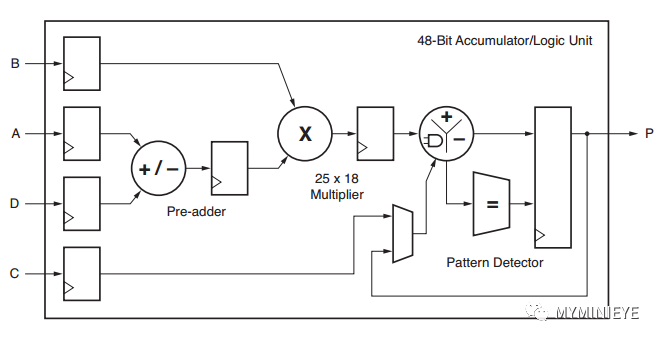

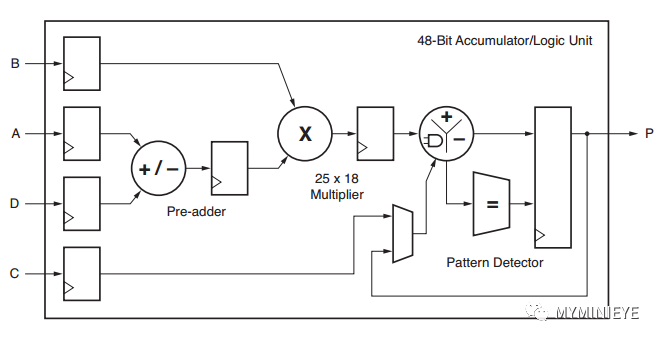

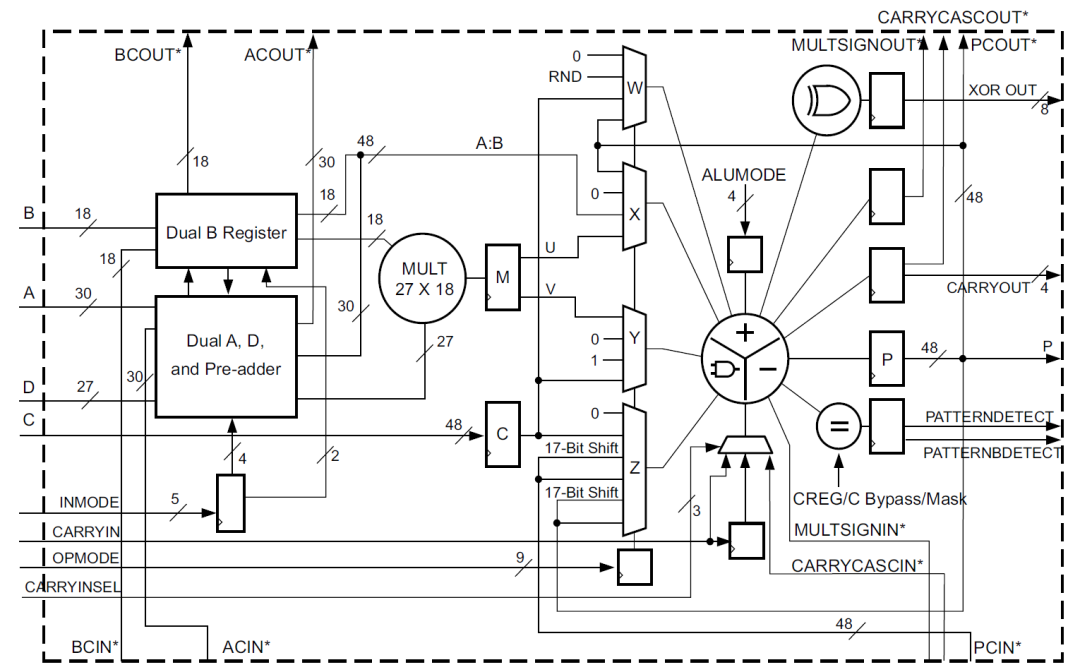

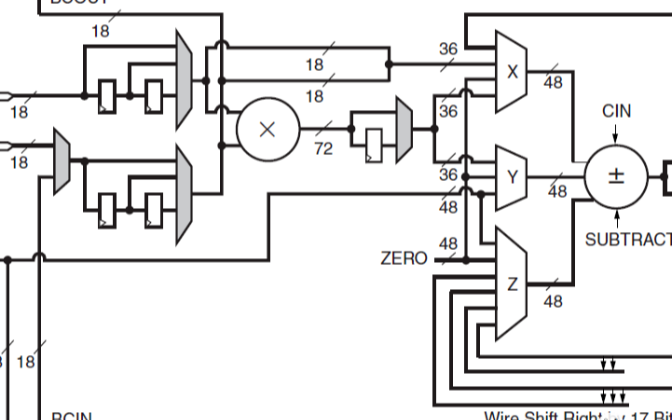

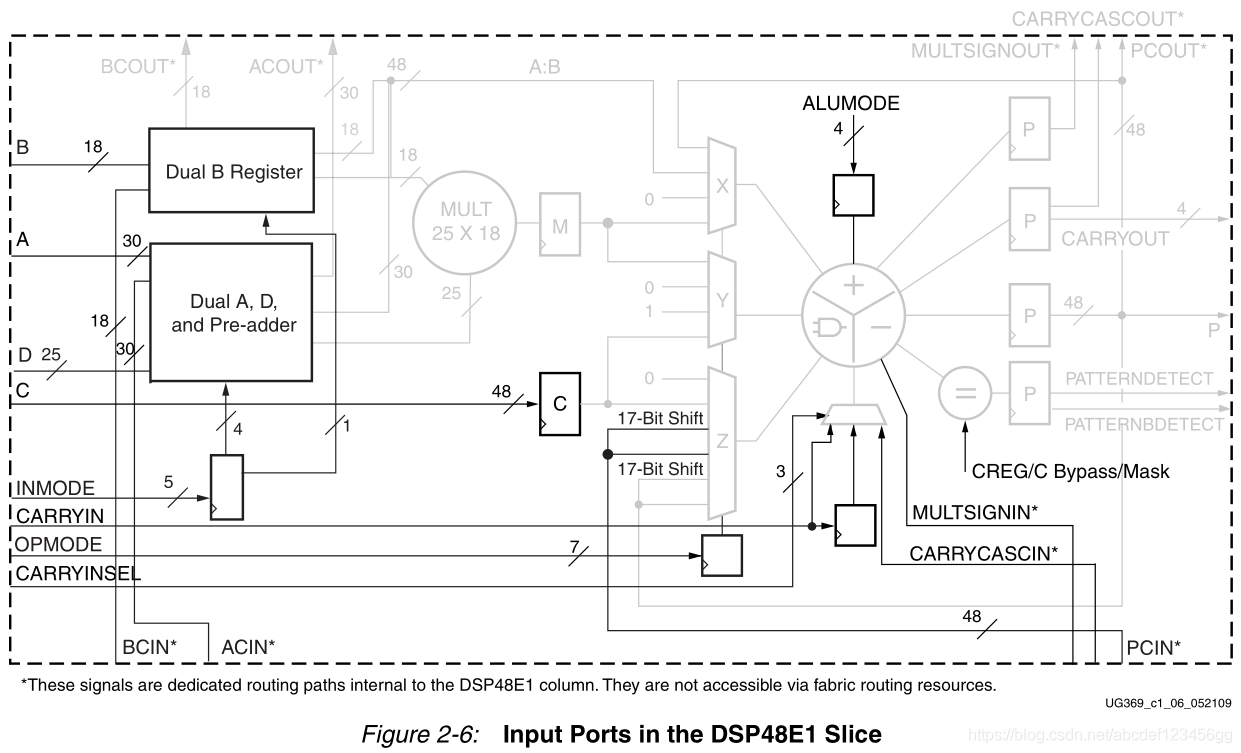

充分利用DSP資源,我們需要對DSP48E1有所了解。 1.DSP48E1介紹 DSP48E1是7系列的最小計算單元,DSP資源,支持許多獨立的功能,其基本功能如下所示 DSP48E1簡易模型 包括: 帶有D寄存器的25位預加法器 25*18二進制乘法 48位累加 三輸入加法 其他的一些功能還包括

2020-09-30 11:48:55 32566

32566

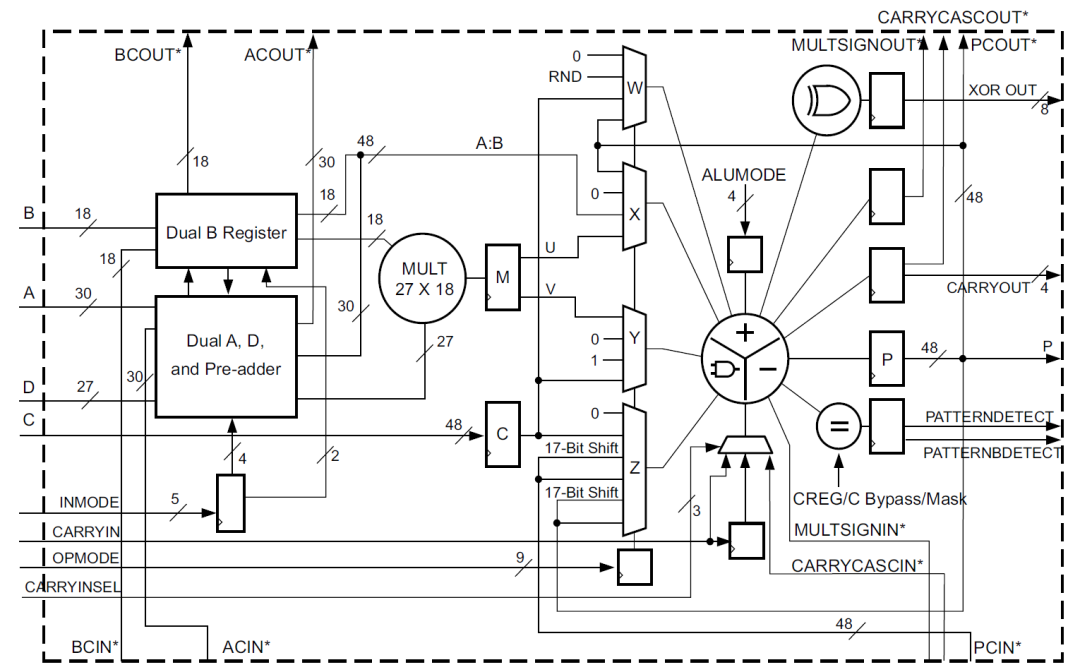

DSP48E2是zynq器件中使用的DSP類型,其主要結構包括一個27bit前加器,27x18bit的乘法器,一個48bit的可以執(zhí)行加減法,累加以及邏輯功能的ALU。

2022-08-02 09:16:27 5383

5383

和C寄存器,具有獨立的復位和時鐘啟用。 ?CARRYCASCIN和CARRYCASCOUT內部級聯(lián)信號支持兩個DSP48E1片中的96位累加器/加法器/減法器 ?MULTSIGNIN

2021-01-08 16:46:10

7系列FPGA DSP48E1片的特點什么

2021-03-05 06:26:41

我正在實例化DSP切片并進行簡單的乘法然后加法((A * B)+ C)。根據DSP48E1用戶指南,當使用所有三個流水線寄存器時,它給出了最高頻率為600 MHz。但就我而言,它使用流水線寄存器

2020-06-12 06:32:01

嗨,我有一個如下的指令:(D-A)* B + C.端口A,B,C,D與DSP48E1輸入引腳相對應。我試圖將整個操作打包在DSP單元中。 (順便說一句,我的數據寬度是8位)在布局和布線完成后,我

2019-04-01 14:25:40

DSP48E1屬性

2021-01-27 06:21:23

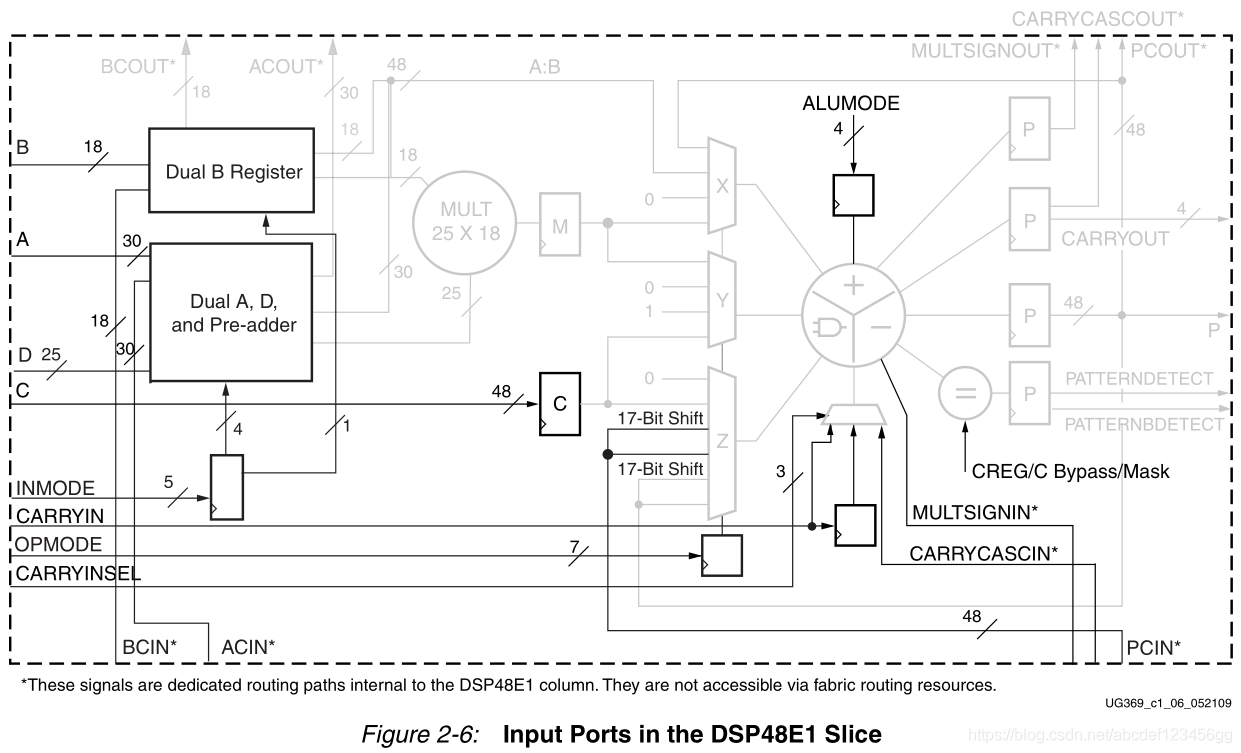

。 DSP48E1片輸入數據端口支持許多通用的DSP和數學算法。DSP48E1片有四個直接輸入數據端口,分別為A、B、C和D。 A數據端口寬30位,B數據端口寬18位,C數據端口寬48位,預加器D數據端口寬25位

2020-12-23 16:54:08

DSP56800 16位DSP內核架構DSP56800內核是一款旨在同時提供高效實時DSP能力和通用計算能力的可編程CMOS 16位DSP內核。DSP56800內核由四個并行執(zhí)行的功能單元組成,從而

2011-07-16 14:21:33

操作,用硬件的方法總比用軟件的方法有著無法比擬的速度優(yōu)勢。 DSP處理都有自己的累加器單元AUL,大多數的DSP處理器在執(zhí)行乘加操作時可以在一條指令周期內同時...

2021-11-03 08:41:44

想請教一下高手,公司了DSP開發(fā)或大家自己開發(fā)學習用TI定義的庫還是自己定義相關寄存器,然后在自己定義的基礎上進行相關算法的開發(fā)????

2014-05-22 12:58:35

充當,利用DSP的HPI接口組成一個多DSP互 連并行系統(tǒng),一般是一個主處理器和一個從處理器,此種方法的一個應用實例是在雷達中的應用。滑窗算法是數字信號處理中一種常用的基本算法,但滑窗算法一般

2019-04-08 09:36:19

近來,Altera公司推出業(yè)界首款浮點FPGA,它集成了硬核IEEE754兼容浮點運算功能,提高了DSP性能、設計人員的效能和邏輯效率。據悉,硬核浮點DSP模塊集成在

2019-07-03 07:56:05

算術邏輯單元(ALU)和一個帶有48位累加器的單24x24位乘加器(MAC)。這些單元都以并行狀態(tài)工作,并具有雙口數據存儲接口,可以同時產生地址信息。所有尋址模式包括反轉和求模運算都支持高效率的單周期訪問。

2011-03-12 03:00:07

:實際上就是乘加器,FPGA 內部可以集成多個乘加器,而一般的 DSP 芯片往往每個 core 只有一個。換言之,FPGA 可以更容易實現多個 DSP core 功能。在某些需要大量乘加計算的場合,往往

2025-05-13 15:41:38

分時鐘、DSP48E/A模塊、BRAM模塊、DCM模塊。0.5學時4. ISE高級操作技巧,包括:FloorPlanner、FPGA Editor、ChipScope Pro

2009-07-21 09:22:42

小、帶寬要求低等優(yōu)點,特別適用于各種無線設備和智能卡等計算資源受限的設備,因而受到了人們的廣泛關注,成為新一代公鑰密碼標準。而模乘運算是橢圓曲線加密算法中的核心運算,如何高效地實現模乘運算是當前的一個研究熱點。

2020-03-20 06:04:40

的整數,即 ; ,通常取 , 是r模n的逆,即 ; 。

計算 的算法:

因為 所以 , 都可以通過簡單的移位操作實現,從而消去了最復雜的除法運算。由于Montgomery 算法計算的是 的值,因此還需要進行相應的預計算和后處理來消除 的影響所以Montgomery 算法并不適合于單次的模乘運算。

2025-10-22 07:35:11

,Z選擇器的輸入;(7bit)

?ALUMODE邏輯控制選擇單元;(4bit)

我們通過構建一個乘累加器來介紹DSP的使用以及寄存器的配置。

實現的乘累加完成如下功能,即SUM = SUM

2023-06-20 14:29:51

分時鐘、DSP48E/A模塊、BRAM模塊、DCM模塊。0.5學時4. ISE高級操作技巧,包括:FloorPlanner、FPGA Editor、ChipScope Pro

2009-07-21 09:20:11

本帖最后由 eehome 于 2013-1-5 10:03 編輯

fpga實現濾波器在利用FPGA實現數字信號處理方面,分布式算法發(fā)揮著關鍵作用,與傳統(tǒng)的乘加結構相比,具有并行處理的高效性特點

2012-08-11 18:27:41

fpga實現濾波器fpga實現濾波器在利用FPGA實現數字信號處理方面,分布式算法發(fā)揮著關鍵作用,與傳統(tǒng)的乘加結構相比,具有并行處理的高效性特點。本文研究了一種16階FIR濾波器的FPGA設計方法

2012-08-12 11:50:16

為什么BUFG驅動DSP48E1的CE會出現問題?警告:LIT:683 - DSP48E1符號“Inst_control_loop / u_Subsystem11

2020-06-12 11:45:43

QuartusII中乘加器IP的手冊,如上圖所示,出現DSP Blocks字樣。手冊中說到,DSP塊由一些專用的邏輯塊組成。這些邏輯塊可以實現乘法、加法、減法、累加、求和運算。你可以把DSP塊配置成

2020-09-04 10:31:13

與遵循馮·諾依曼結構的CPU和單片機不同,典型的DSP內部采用改進的哈佛結構和流水線技術,可以在單指令周期內完成乘加指令,更具有擴展動態(tài)范圍的乘積累加單元、數據指針環(huán)形尋址和零開銷循環(huán)跳轉等特殊

2011-03-06 22:28:27

的距離塊就可以完成256個單元的計算。把上述結構映射到FPGA上實現,則FPGA上并行32個運算單元,且每1個運算單元具有1個與其他運算單元獨立的復數乘加模塊、寄存器組和1個互相關值輸出鎖存寄存器

2009-09-19 09:25:42

DSU相關的權函數使用,記為fI和fQ;接收回波信號在A/D采樣后,經過正交分解形成數據流rI和rQ,然后對接收數據進行相關操作,即回波數據以流水方式通過相關器與發(fā)射樣本數據逐點進行乘加處理。本論

2015-02-05 15:34:43

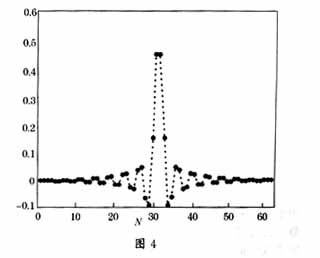

針對長期演進(LTE)下行正交頻分復用(OFDM)系統(tǒng)的最小二乘(LS)信道估計算法對噪聲比較敏感的問題,提出了一種基于小波變換去噪與變換域插值相結合的信道估計方法。該方法通過在最小二乘(LS)估計

2010-05-06 09:01:31

/20755211100719/1310381718_530721f7.gif]4 FFT復乘的FPGA實現由于軟件和DSP實現的速度較慢,而FPGA資源豐富,組織結構便于采用流水線結構和并行運算,其速度快、擴展能力強

2011-07-11 21:32:29

本帖最后由 mr.pengyongche 于 2013-4-30 03:23 編輯

8核的TMS320C6678款DSP芯片一個周期可

2012-02-18 13:19:36

本帖最后由 mr.pengyongche 于 2013-4-30 03:23 編輯

8核的TMS320C6678款DSP芯片一個周期可

2012-02-18 13:29:59

,圖2-1和第14頁和第16頁的2-2中的原理圖,我注意到乘法路徑具有實現3級流水線所需的寄存器但是,C輸入的datha路徑只能使用2個寄存器。所以我的問題是,我應該在DSP48E1 Block之外添加

2020-07-21 13:52:24

FIFO芯片是什么?如何利用FIFO去實現DSP間雙向并行異步通訊?

2021-06-02 06:08:17

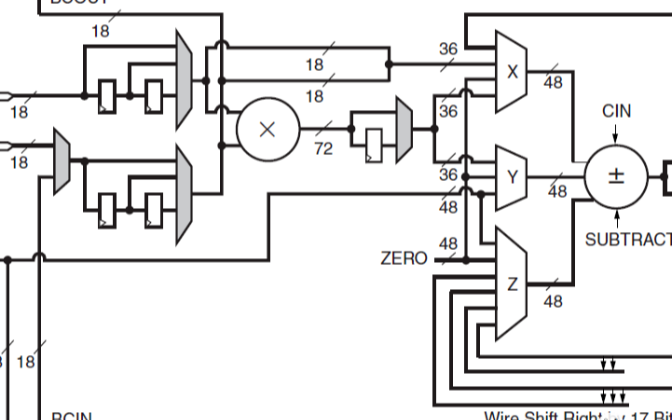

DSP48E1片的數學部分由一個25位的預加器、2個25位、18位的補法器和3個48位的數據路徑多路復用器(具有輸出X、Y和Z)組成,然后是一個3輸入加法器/減法器或2輸入邏輯單元(參見圖2-5

2021-01-08 16:36:32

簡化DSP48E1片操作

2021-01-27 07:13:57

喜據我所知,有些xilinx FPGA具有DSP Slice(DSP48E)。在fpga設計摘要中,我看到切片寄存器,切片LUT,占用切片等以及DSP48E的單獨行。我的問題是 - 1)DSP48E

2019-04-04 06:36:56

值。目前,數字信號處理器(DSP)技術的高速發(fā)展為高效媒體處理器的實現提供了可靠的硬件平臺。C64系列DSP是當前TI(Texas Instruments)公司推出的處理能力最高的定點DSP,NVDK

2008-06-25 10:35:31

。 Achronix為了解決這一大困境,創(chuàng)新地設計了機器學習處理器(MLP)單元,不僅支持浮點的乘加運算,還可以支持對多種定浮點數格式進行拆分。

2020-11-26 06:42:00

嘿,為了在Zynq設備上對一種算法的不同實現進行簡單比較,我想為每種實現的資源使用創(chuàng)建一個指示符,例如CLB的使用。因此,獲得基本元素CLB,DSP48E1和BRAM36K的面積指標會很好。在

2020-07-25 11:04:42

的,和整數長度一致。

2.浮點運算指令實現:蜂鳥E203可以通過在EXU內添加一個與ALU平行的模塊:浮點處理單元(float point unit),專用于處理浮點指令。該單元可以更高效地執(zhí)行浮點數計算

2025-10-22 07:04:49

、譯碼和執(zhí)行等操作可以重疊執(zhí)行。 當然,與通用微處理器相比,DSP芯片的其他通用功能相對較弱些。 DSP優(yōu)勢在于其有獨特乘法器,一個指令就可以完成乘加運算,但GPP(通用處理器)處理一般是用加法代替乘法

2018-12-11 12:05:54

、譯碼和執(zhí)行等操作可以重疊執(zhí)行。 當然,與通用微處理器相比,DSP芯片的其他通用功能相對較弱些。 DSP優(yōu)勢在于其有獨特乘法器,一個指令就可以完成乘加運算,但GPP(通用處理器)處理一般是用加法代替乘法

2019-02-25 16:58:00

操作,使取指、譯碼和執(zhí)行等操作可以重疊執(zhí)行。 當然,與通用微處理器相比,DSP芯片的其他通用功能相對較弱些。 DSP優(yōu)勢在于其有獨特乘法器,一個指令就可以完成乘加運算,但GPP(通用處理器)處理一般是用

2019-05-16 17:06:34

我看書上說現代DSP內置MAC硬核,可以在一個時鐘周期完成取數相乘并累加。實驗如下,例如c=a*b+c;反匯編如下可以看到有七句匯編,先用2個周期取ab值,1個周期相乘,1個周期取c值,1個周期想加

2018-10-10 11:08:14

【摘要】針對以往DOA估計算法中智能天線系統(tǒng)的陣列單元模型多采用全向振子的情況,分析了當天線單元存在方向性時對MUSIC算法估計信號到達角的影響,并在進行陣元互耦校正后

2009-03-14 15:12:51 18

18 基于VxWorks的多DSP并行處理系統(tǒng)的實現

2009-03-29 12:31:18 17

17 High DSP Performance Platform– The DSP48E Slice– Essential DSP Building Blocks• Imaging Algorithms

2009-04-09 22:05:31 12

12 本文設計了擴展的乘累加單元(DSPMAC),用于運算速度的提高。基于or1200 乘累加單元,運用RISC技術和并行操作,通過開發(fā)32-bit 指令中的保留位,在資源占用增幅較少和一定的功耗及

2009-05-25 09:25:25 8

8 本文針對CDMA 系統(tǒng),提出使用DSP 器件TMS320C6701 實現對CDMA 信號的波達方向估計。該算法基于對解擴前后相關陣相減,去除了干擾相關陣是,然后使用傳統(tǒng)MUSIC或ESPRIT 算法進行DOA 估

2009-06-18 09:13:09 16

16 比較了幾種16x16 位乘加器的實現方法,給出了一種嵌入于微處理器的基于流水線重構技術的16x16 位乘加器的設計方案,該設計可完成16bit 整數或序數的乘法或乘加運算,并提高了運

2009-06-22 09:04:47 12

12 信道估計是RAKE 接收機的關鍵技術,WCDMA 中可采用時分復用導頻完成,給出了用DSP 的具體實現方案。關鍵詞:DSP;信道估計;WCDMA

2009-09-15 09:36:23 28

28 PC機與DSP之間的并行通訊技術

摘要:對PC 機在EPP 模式下與C6000 系列DSP 的HPI 口之間進行的并行通訊進行了研究,提出了用EPP 協(xié)議和CPLD 實現DSP 與計算機并口

2010-04-07 14:37:06 35

35 乘累加器在DSP算法中有著舉足輕重的地位。現在,很多前端DSP算法都通過FPGA實現。結合FPGA具體的硬件結構,提出了乘累加器在FPGA中實現的改進方法:流水線技術、CSD編碼、DA算法,

2010-08-06 14:41:38 29

29 摘要:提出了一種巧妙實現DSP并行自舉的方法,即采用“兩次下載法”,利用DSP自身對FLASH編程,以實現DSP的并行自舉。這種在系統(tǒng)編程的DSP自舉實現方式無需文件

2006-03-11 17:39:50 1758

1758

摘 要:本文介紹了一種48bit+24bit×24bit帶飽和處理的MAC單元設計。在乘法器的設計中,采用改進的booth 算法來減少部分積的數目,用由壓縮單元組成的Wallace tree將產生

2006-03-24 13:32:00 1171

1171

基于流水線技術的并行高效FIR濾波器設計

基于流水線技術,利用FPGA進行并行可重復配置高精度的FIR濾波器設計。使用VHDL可以很方便地改變?yōu)V波器的系數和階數。在DSP中采用

2009-03-28 15:12:27 995

995

帶有飽和處理功能的并行乘加單元設計

本文介紹了一種48bit+24bit×24bit帶飽和處理的MAC單元設計。在乘法器的設計中,采用改進的booth 算法來減少部分積的數目,用由壓縮單

2009-03-28 16:28:58 2253

2253

介紹了一種用于IP電話中的自適應回聲消除器,采用歸一化最小二乘(NLMS)自適應濾波器實現,包括語音模式檢測器和粗略時延估計器。最后以TI公司的TMS320C5402 DSP芯片為平臺,實現

2009-05-06 20:22:13 2802

2802

本文提出了一種新型的高速濾波器結構,此結構的核心是一種獨特的乘加單元. 該乘加單元是通過對BOOTH 型乘法器與高速加法器結構的深入研究而探索出來的. 采用該乘加單元我們可以實

2011-06-20 15:34:35 27

27 在水下日標檢測和跟蹤系統(tǒng)中,多目標方位估計算法起著重要的作用.MUSIC算法是最具代表性的方法}為了滿足目標方位估計對高速變時并行處理技術的要求,針對水下陣列信號處理的實

2011-10-12 16:19:54 41

41 介紹了時差測向的基本原理,其關鍵在于對時差的測量,因此主要工作即為對跳頻信號進行時差測量。基于信道化方法對跳頻信號進行時差估計具有較高的精度,可以在FPGA中實現。

2012-02-08 15:12:58 34

34 4個16乘16LED點陣仿真加原理圖加PCB,直接就可以用,還附有論文可以用來參考

2016-12-20 22:23:43 80

80 ):使用DS48E1的SIMD功能實現四路并行12位加法”,要求數據從不同的DSP48端口進去。 評分標準: 1)使用Vivado 仿真通過 2)使用7A50T板子,使用Vivado硬件實現且記錄波形,或者,使用Matlab sysgen硬件仿真,或者其他硬件實現方式且有硬件結果 軟件環(huán)境:

2017-02-07 20:23:33 3109

3109 概述 Xilinx的DSP48E1模塊在7系列的fpga芯片中經常被用于DSP應用當中。他能夠有效提高設計的靈活性和效率,提高產品的性能。 DSP48E1支持許多獨立的功能。包括:乘法、乘加

2017-02-08 01:07:12 1174

1174

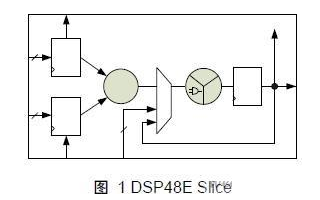

概述 利用4個dsp48e1模塊,實現四路加法器,dsp48e1模塊在手冊中表示比較復雜,找了兩個圖,可以大致看懂他的基本功能。 圖1 dsp48e1端口說明 圖2 簡化的DSP48E1結構 軟件

2017-02-08 01:10:08 994

994

仍然不是最優(yōu)的結果。理論上如果采用串行的結構,乘加運算可以復用,雖然latency會變長,但是一個fir濾波器最少只需要1個乘法器即可實現。但是我們之前的c代碼,HLS確采用的2個乘法運算單元,這是為什么呢? 我們還是先看下原先的代碼結構,簡單起見,只放相關的片段: 我們可以看到

2017-02-08 05:11:11 775

775

基于FPGA和多DSP的多總線并行處理器設計

2017-10-19 13:40:31 4

4 TMS320VC5416DSP并行自舉方案的設計與實現

2017-10-20 09:15:22 12

12 DSP并行系統(tǒng)的并行粒子群優(yōu)化目標跟蹤

2017-10-20 10:54:00 6

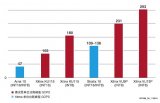

6 本白皮書旨在探索實現在賽靈思 DSP48E2 Slice 上的 INT8 深度學習運算,以及與其他 FPGA 的對比情況。在相同資源數量情況下,賽靈思的 DSP 架構憑借 INT8在 INT8 深度

2017-11-16 14:23:01 16026

16026

根據BPSK調制信號調制機理和平方倍頻法原理,在FPGA平臺上設計實現了BPSK調制信號載波頻率估計單元。利用ModelSim仿真環(huán)境對載頻估計功能進行仿真,驗證了平方倍頻法對BPSK信號進行載波

2017-11-18 05:13:05 4539

4539

布爾多項式求解是當今密碼代數分析中的關鍵步驟,F4算法是布爾多項式求解的高效算法。分析了Lachartre為F4矩陣專門設計的高斯消去算法,針對其中布爾矩陣乘這一耗時的計算步驟,設計并實現了分布式

2017-11-21 15:32:59 3

3 軟相關器的方法。本方法利用GPU在計算FFT、向量乘和向量加等密集型計算模型的優(yōu)勢,設計相關器的并行模型,使其性能較前期在CPU并行的MPI集群實現的相關器有了大幅提升。同時,本文選擇廣泛應用于大數

2017-12-06 10:12:26 0

0 本文主要介紹了一種基于DSP+FPGA視頻圖像采集處理系統(tǒng)的設計與實現,DSP-BF561作為主處理器,負責整個算法的調度和數據流的控制,完成圖像數據的采集與顯示及核心算法的實現,FPGA作為DSP的協(xié)處理器,依托其高度的并行處理能力,完成圖像預處理中大量的累乘加運算。實驗證明系統(tǒng)達到了實時性要求。

2017-12-25 10:39:47 5649

5649

描述了浮點型算法的加、減、乘、除的verilog代碼,編寫了6位指數位,20位小數位的功能實現并且通過仿真驗證

2018-01-16 14:15:54 1

1 ,其速度直接影響DSP的速度,因此國內外學者對提高浮點乘加單元的性能進行了大量的研究。浮點運算單元的設計主要是在速度和所占用資源之間進行權衡。 本文以實時信號處理為應用背景,首先介紹了單精度浮點格式,然后從速度和占用

2018-04-10 10:47:21 8

8 更加多樣化。DSP48基本結構如下圖所示(圖片來源:ug073, Figure 2-1)。DSP48中的核心單元是18x18的乘法器。從圖中不難看出,DSP48可實現基本數學函數P=Z(X+Y+CIN

2020-10-30 17:16:51 7834

7834

A、B、C、CARRYIN、CARRYINSEL、OPMODE、BCIN、PCIN、ACIN、ALUMODE、CARRYCASCIN、MULTSIGNIN以及相應的時鐘啟用輸入和復位輸入都是保留端口。D和INMODE端口對于DSP48E1片是唯一的。本節(jié)詳細描述DSP48E1片的輸入端口

2022-07-25 18:00:18 6751

6751

DSP48E1片的數學部分由一個25位的預加器、2個25位、18位的補法器和3個48位的數據路徑多路復用器(具有輸出X、Y和Z)組成,然后是一個3輸入加法器/減法器或2輸入邏輯單元(參見圖2-5)。使用2輸入邏輯單元時,不能使用乘法器。

2022-01-21 14:14:26 1829

1829 在DSP48E1列中,級聯(lián)各個DSP48E1片可以支持更高級的DSP功能。兩個數據路徑(ACOUT和BCOUT)和DSP48E1片輸出(PCOUT、MULTSIGNOUT和CARRYCASCOUT)提供級聯(lián)功能。級聯(lián)數據路徑的能力在過濾器設計中很有用。

2022-06-21 08:55:00 3249

3249 擴頻碼的相關解擴是擴頻通信接收機的關鍵技術之一,主要介紹了數字相關器在全球定位系統(tǒng)(GPS)信號捕獲中的應用,并進行了FPGA實現。在設計中,采用了16路并行相關運算的方式加快相關解擴運算速度。在

2021-01-26 16:22:43 15

15 在DSP48E1列中,級聯(lián)各個DSP48E1片可以支持更高級的DSP功能。兩個數據路徑(ACOUT和BCOUT)和DSP48E1片輸出(PCOUT、MULTSIGNOUT和CARRYCASCOUT)提供級聯(lián)功能。級聯(lián)數據路徑的能力在過濾器設計中很有用。

2021-01-27 07:34:32 10

10 A、B、C、CARRYIN、CARRYINSEL、OPMODE、BCIN、PCIN、ACIN、ALUMODE、CARRYCASCIN、MULTSIGNIN以及相應的時鐘啟用輸入和復位輸入都是保留端口。D和INMODE端口對于DSP48E1片是唯一的。本節(jié)詳細描述DSP48E1片的輸入端口

2021-01-27 08:18:02 2

2 DSP48E1片的數學部分由一個25位的預加器、2個25位、18位的補法器和3個48位的數據路徑多路復用器(具有輸出X、Y和Z)組成,然后是一個3輸入加法器/減法器或2輸入邏輯單元(參見圖2-5)。使用2輸入邏輯單元時,不能使用乘法器。

2021-01-29 08:19:37 13

13 并行矩陣乘法是線性代數中最重要的基本運算之一,同時也是許多科學應用的基石。隨著高性能計算(HPC)向E級計算發(fā)展,并行矩陣乘法的通信開銷所占比重越來越大。如何降低并行矩陣乘法的通信開銷,提高并行矩陣

2021-06-01 14:33:43 5

5 本文是本系列的第三篇,本文主要介紹FPGA常用運算模塊-乘加器,xilinx提供了相關的IP以便于用戶進行開發(fā)使用。

2023-05-22 16:17:12 2959

2959

電子發(fā)燒友網為你提供Maxim(Maxim)DS2502-E48+相關產品參數、數據手冊,更有DS2502-E48+的引腳圖、接線圖、封裝手冊、中文資料、英文資料,DS2502-E48+真值表,DS2502-E48+管腳等資料,希望可以幫助到廣大的電子工程師們。

2023-07-31 18:42:26

電子發(fā)燒友App

電子發(fā)燒友App

評論