1.請問AM335X armv7 架構是否有向DSP 有單週期可執行多個乘加運算的功能 ??

2. FFT 運算式會運用到AM335X的VFP 還是NEON??

3.若執行一段浮點運算程式碼 例如

2018-06-21 06:58:42

算術邏輯單元(ALU)和一個帶有48位累加器的單24x24位乘加器(MAC)。這些單元都以并行狀態工作,并具有雙口數據存儲接口,可以同時產生地址信息。所有尋址模式包括反轉和求模運算都支持高效率的單周期訪問。

2011-03-12 03:00:07

卷積運算單元,支持3*3或者5*5模板大小,運算能力相當于8300MMAC/s;支持基于像素、方差、幅值和梯度的積分運算;支持閾值和直方圖運算;通用的32位硬件加、減、乘、除法器;最大支持1280*960像素點分辨率;最大支持4路運算并行處理,每路最大帶寬為84MP/s(P->Pixel。

2018-08-28 11:48:35

CPU中央處理單元包含基本的運算單元AUL,存儲單元cache等基本資源,實現硬件設備的基本控制功能。中央處理器作為一個普世概念,實際根據具體數據處理功能方向不同,細分位DSP、MCU和MP。其中

2021-12-14 07:46:20

操作,用硬件的方法總比用軟件的方法有著無法比擬的速度優勢。 DSP處理都有自己的累加器單元AUL,大多數的DSP處理器在執行乘加操作時可以在一條指令周期內同時...

2021-11-03 08:41:44

`產品特點基于ZYNQ+并行DSP處理架構處理架構十分靈活,能夠滿足各類并行加速需求支持OpenCL編程,方便算法移植系統處理靈活:FPGA或DSP可選尺寸小巧,方便集成擴展能力強 應用領域并行控制

2017-06-08 10:33:07

DSP并行處理的方法摘 要:TI公司的TMS320C6x和AD公司的ADSP2106x是目前業界使用廣泛的數字信號處理器(DSP)。

2009-11-03 15:16:47

在通信、雷達等系統中,特別是在3G無線基站等系統中,隨著輸入語音 數字和分組數據量急劇增加,系統的處理能力也需要急劇增加,這需要一種功能強大的大型并行陣列信號處理系統。系統往往需要進行非常復雜

2019-04-08 09:36:19

:實際上就是乘加器,FPGA 內部可以集成多個乘加器,而一般的 DSP 芯片往往每個 core 只有一個。換言之,FPGA 可以更容易實現多個 DSP core 功能。在某些需要大量乘加計算的場合,往往

2025-05-13 15:41:38

LABVIEW的并行事件處理小程序

2015-12-18 10:27:50

的整數,即 ; ,通常取 , 是r模n的逆,即 ; 。

計算 的算法:

因為 所以 , 都可以通過簡單的移位操作實現,從而消去了最復雜的除法運算。由于Montgomery 算法計算的是 的值,因此還需要進行相應的預計算和后處理來消除 的影響所以Montgomery 算法并不適合于單次的模乘運算。

2025-10-22 07:35:11

S32k系列微型機,特別是S32K388具有并行處理功能嗎?

2025-03-26 08:27:41

FPU是什么 獨立于CPU的一個浮點運算單元,可以使能或關閉。 支持單精度浮點數的運算:加、減、乘、除、乘加、平方根… 整數、單精度浮點(32位)、半精度浮點(16位)之間的數據格式轉換

2023-09-12 07:09:11

我是一個過時的電腦用戶,從Pong天C64 / 128,Amiga,英特爾......我正在研究MS發生的事情,并想知道他/她們什么時候會跳轉到并行處理的電路板。他們正在推出當前的硬件,并且即將

2018-10-18 14:06:51

,Z選擇器的輸入;(7bit)

?ALUMODE邏輯控制選擇單元;(4bit)

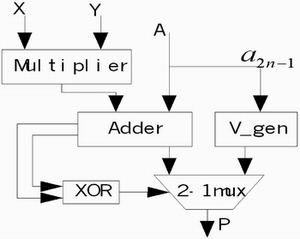

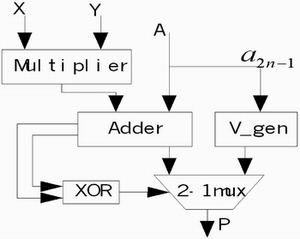

我們通過構建一個乘累加器來介紹DSP的使用以及寄存器的配置。

實現的乘累加完成如下功能,即SUM = SUM

2023-06-20 14:29:51

詳細的數據呢?據我了解,dsp與arm的主要區別是多了一個乘加指令,arm是利用加法指令模擬乘法指令的,那么arm 需要多少指令可以完成一個乘加指令呢

2013-02-27 11:18:54

官方給出的只需要一個指令周期,按這個說也就是6ns。而我自己測試的是20多ns,測試方法是進行1000次乘加運算后把某個引腳拉低,用示波器觀察。請問有什么好的方法測試嗎,或者有測試出需要一個指令周期的。希望有高人指點

2017-04-20 16:47:21

`一、硬件平臺 二、實驗簡介 STMH32H7采用Cortex-M7內核,相比Cortex-M3系列除了內置硬件FPU單元,在數字信號處理方面還增加了DSP指令集,支持諸如單周期乘加指令(MAC

2020-04-14 22:47:36

一種柔性圖像并行處理機摘 要:探討了多指令流多數據流圖像并行處理拓撲結構,設計了一種具有柔性結構的圖像并行處理機。分析比較了柔性圖像并行處理機與典型圖像并行處理機在結構和性能方面的差異,給出了一種

2009-10-06 08:57:53

結構。此結構能同時從四個并行存儲器中讀取蝶形運算所需的4個操作數,極大地提高了處理速度。此結構控制單元簡單,便于模塊化設計。經硬件驗證,達到設計要求。在系統時鐘為100MHZ時,1024點18位復數

2008-10-15 22:41:48

乘法器、乘加器、乘累加器,并運用在絕大多數DSP算法上。顯然,這里的DSP塊,只是一個可配置的乘加單元,并非前面所說的DSP處理器。其實FPGA內部并沒有DSP處理器。五、STM32中的DSP是什么東西

2020-09-04 10:31:13

與多核處理器配合使用,那么從信號到最后測量的并行化測量就實現了。并行化測試利用多核處理器、PCI Express總線和LabVIEW軟件,用戶可以創建并行化的測量系統,它們能夠同時測試一個待測單元

2014-12-12 16:02:30

合并行或者列或者cell單元 控件怎么用。。。求 最好有例子截圖 謝謝

2015-01-06 13:56:30

由STC89C52單片機+4乘4按鍵模塊+LCD1602液晶顯示屏+電源構成具體功能:利用輸入采用4×4矩陣鍵盤,可以進行加、減、乘、除等幾種數字運算,并在LCD1602上顯示操作過程及結果。

2021-07-15 07:41:53

由STC89C52單片機+5乘4按鍵模塊+LCD1602液晶顯示屏+電源構成具體功能:利用輸入采用5×4矩陣鍵盤,可以進行加、減、乘、除等十幾種數字運算,并在LCD1602上顯示操作過程及結果。

2021-07-21 08:41:58

DSP并行處理系統的原理圖如圖1所示。整個雷達信號處理系統以高可靠性CPCI工控機為平臺,內置不同功能的信號處理板。板間的數據傳輸通過CPCI接口完成。根據雷達信號處理系統的任務分 配,本系統負責完成

2019-05-21 05:00:19

隨著深亞微米工藝的發展, FPGA的容量和密度不斷增加,以其強大的并行乘加運算(MAC)能力和靈活的動態可重構性,被廣泛應用于通信、圖像等許多領域。

2019-10-30 06:16:57

FFT(快速傅里葉變換)在無線通信、語音識別、圖像處理和頻譜分析等領域有著廣泛應用。在FFT運算中,核心操作是蝶形運算,而蝶形運算的主要操作是向量旋轉,實現向量旋轉可用復數乘法運算來實現,但復數乘

2011-07-11 21:32:29

本帖最后由 mr.pengyongche 于 2013-4-30 03:23 編輯

8核的TMS320C6678款DSP芯片一個周期可

2012-02-18 13:19:36

本帖最后由 mr.pengyongche 于 2013-4-30 03:23 編輯

8核的TMS320C6678款DSP芯片一個周期可

2012-02-18 13:29:59

其他部件發來的中斷請求。CPU內部包含如下三部分:算術邏輯部件;累加器和寄存器組;控制器;他們通過內部總線相連接。32位的CPU芯片中還集成了浮點運算器、存儲管理器和高速緩存等部件。**算術邏輯部件:**專門用來處理各種數據信息,它可以進行加、減、乘、除算術運算和與、或、非、異

2022-02-28 07:05:19

優化的器件,我們開發了eIQ Neutron神經處理單元(NPU)。eIQ Neutron神經處理單元架構可從我們產品組合中最高效的MCU擴展到功能最強大的i.MX應用處理器。它具有較高的可擴展性,每周

2023-02-17 13:51:16

。 Achronix為了解決這一大困境,創新地設計了機器學習處理器(MLP)單元,不僅支持浮點的乘加運算,還可以支持對多種定浮點數格式進行拆分。

2020-11-26 06:42:00

的,和整數長度一致。

2.浮點運算指令實現:蜂鳥E203可以通過在EXU內添加一個與ALU平行的模塊:浮點處理單元(float point unit),專用于處理浮點指令。該單元可以更高效地執行浮點數計算

2025-10-22 07:04:49

采用軟硬件結合的方法,給出一種基于VLIW 的并行可配置橢圓曲線密碼體制(ECC)專用指令協處理器架構。該協處理器采用點加、倍點并行調度算法,功能單元微結構采

2009-03-20 16:14:02 25

25 基于VxWorks的多DSP并行處理系統的實現

2009-03-29 12:31:18 17

17 本文設計了擴展的乘累加單元(DSPMAC),用于運算速度的提高。基于or1200 乘累加單元,運用RISC技術和并行操作,通過開發32-bit 指令中的保留位,在資源占用增幅較少和一定的功耗及

2009-05-25 09:25:25 8

8 比較了幾種16x16 位乘加器的實現方法,給出了一種嵌入于微處理器的基于流水線重構技術的16x16 位乘加器的設計方案,該設計可完成16bit 整數或序數的乘法或乘加運算,并提高了運

2009-06-22 09:04:47 12

12 FAG、SKF 等公司開發的帶有集成傳感器的軸承是把某些功能的傳感器與軸承結合為一體而形成的獨特結構單元。如帶有運動傳感器的深溝球軸承,除支承旋轉軸外,還可以測量軸承內

2009-07-06 08:27:31 10

10 HT MCU 加、減、乘、除法文件編碼:HA0014s簡介:本程序包含八位、十六位、二十四位及三十二位定點數據的基本運算。基本的運算包括:加法(有符號、無符號)、減法

2010-03-26 08:34:21 21

21 CPU接口。該器件提供了兩個分別帶有標簽識別的接收器、一個32乘32的FIFO和一個模擬線路接收器。每個接收器最多可以編程16個標簽。獨立的發射器還具有一個32乘32

2024-02-19 15:11:37

摘 要:本文介紹了一種48bit+24bit×24bit帶飽和處理的MAC單元設計。在乘法器的設計中,采用改進的booth 算法來減少部分積的數目,用由壓縮單元組成的Wallace tree將產生

2006-03-24 13:32:00 1171

1171

BP神經網絡圖像壓縮算法乘累加單元的FPGA設計

0 引 言??? 神經網絡(Neural Networks)是人工神經網絡(Ar-tificial Neural Networks)的簡稱,是當前的研究熱點之一。人

2009-11-13 09:50:05 1774

1774 什么是頂點著色單元 頂點著色單元是顯示芯片內部用來處理頂點(Vertex)信息并完成著色工作的并行處理

2009-12-25 10:46:02 425

425 分享Accuon技術RGB/視頻并行處理技術

在信號處理方面,Accuon已經不再停留在依賴網絡圖像處理器的階段,在此基礎上開發了世界獨創的RGB/視頻并行處

2010-02-11 14:51:19 602

602 BP神經網絡圖像壓縮算法乘累加單元的FPGA設計

概 述神經網絡(Neural Networks)是人工神經網絡(Ar-tificial Neural Networks)的簡稱,是當前的研究熱點之一。人腦在接受視覺

2010-03-29 10:05:12 893

893

并行除法器 ,并行除法器結構原理是什么?

1.可控加法/減法(CAS)單元 和陣列乘法器非常相似,陣列式除法器也是一種并行運算部件,采用大規模集成

2010-04-13 10:46:30 16505

16505 本文通過改變通常FIR處理結構,有效地節省了資源,只使用了一套乘加器,一套FIR濾波器結構,就完成了兩套FIR濾波器的功能,

2011-05-13 09:32:32 5329

5329

本文提出了一種新型的高速濾波器結構,此結構的核心是一種獨特的乘加單元. 該乘加單元是通過對BOOTH 型乘法器與高速加法器結構的深入研究而探索出來的. 采用該乘加單元我們可以實

2011-06-20 15:34:35 27

27 針對小衛星仿真測試系統中對信 號處理 單元的模擬需求,設計并開發了一種信號處理單元模擬器,模擬真實衛星信號處理單元的工作過程和時序,在衛星仿真測試系統中代替信號處理

2011-06-22 16:56:44 45

45 提出了一種具有高并行度機載SAR實時并行成像算法實現方案。對實測數據進行成像處理結果表明,文中所提方案能夠滿足實時成像處理要求,同時與傳統實時成像處理系統相比較,能夠大幅

2011-11-30 17:25:06 55

55 帶有PFC功能的變頻電源構成方案帶有PFC功能

2015-12-07 14:05:50 29

29 4個16乘16LED點陣仿真加原理圖加PCB,直接就可以用,還附有論文可以用來參考

2016-12-20 22:23:43 80

80 SoC集成中的處理單元性能評估及功能劃分

2017-01-12 22:09:33 2

2 并行處理在計算全息中的應用_簡獻忠

2017-03-19 11:28:02 0

0 基于ADSP21060的并行信號處理系統設計_邵禎

2017-03-19 11:31:31 1

1 基于FPGA和多DSP的多總線并行處理器設計

2017-10-19 13:40:31 4

4 帶有多個處理單元的soc器件目前是產品設計鏈上的重要一環。本文綜合各種因素評估了不同處理單元的優缺點,并通過衛星無線電接收器的設計實例幫助開發人員理解soc所涉及處理任務之間的復雜平衡并有效掌握系統

2017-10-21 10:37:46 1

1 多DSP的高速通用并行處理系統研究與設計

2017-10-23 15:19:06 6

6 。并行計算是提高處理速度最有效的技術之一,圖像并行處理技術為提高圖像處理效率提供了廣闊的空間。圖像并行處理包括并行算法和多處理器并行硬件系統,圖像處理并行算法的執行效率依賴于多處理器系統的硬件結構。通常,一種并行

2017-10-24 11:39:15 0

0 等突出優點,特別是在夜間、霧天及能見度不良、通視度較差的情況或者復雜電磁環境下,是戰場信息感知不可缺少的重要手段之一。 并行DSP處理的目的是采用多個處理單元(DSP)同時對任務處理以減少任務的執行時間。多DSP并行處

2017-10-31 11:50:02 1

1 為針對受限玻爾茲曼機處理大數據時存在的訓練緩慢、難以得到模型最優的問題,提出了基于CJPU的RBM模型訓練并行加速方法。首先重新規劃了對比散度算法在CJPU的實現步驟;其次結合以往CJPU并行方案

2017-11-07 14:38:46 12

12 ,可以完成并行化的測試構架。具有此結構的測試系統利用PCI Express提高了數據吞吐量,使用LabVIEW、多核處理器和FPGA增強了處理能力,最后利用NI TestStand軟件降低了每個待測單元的總體測試時間和費用。

2017-11-16 20:31:57 10951

10951

異構(CPU+ MIC)并行算法。布爾矩陣相對于普通矩陣主要體現在矩陣元素取值區間不一樣上,由于布爾矩陣元素(O,1)導致矩陣乘操作的特殊性,普通矩陣乘的優化方法不能很好地滿足布爾矩陣乘的需求。分別從布爾矩陣的存儲、OpenMP多線程組織、訪存

2017-11-21 15:32:59 3

3 方面并行性的優勢,提出了基于OpenCL的JPEG壓縮算法并行化設計方法。將JPEG算法功能分解為多個內核程序,內核之間通過事件信息傳遞進行順序控制,并在GPU+CPU的異構平臺上完成了并行算法的仿真驗證。實驗結果表明,與CPU串行處理方式

2017-11-21 16:57:15 4

4 從相關時差估計的基本原理出發,提出了一種并行時域相關結構,基于這種 并行結構 設計實現了一種簡單高效的時差估計器。與傳統頻域相關時差估計器相比,這種時差估計器的主要優點是提高了運算效率,運算周期大為

2017-11-24 18:46:51 2291

2291

重復計算稀疏矩陣向量乘,提出了新的并行計算結構。實驗分析表明,提出的架構提高了Wiedemannn算法中稀疏矩陣向量乘的并行性,同時充分利用了FPGA的片內存儲器和吉比特收發器,與目前性能最好的部分可重構計算PR模型相比,實現了2.65倍的加速性能。

2017-11-27 10:45:14 0

0 )的并行處理特性,而且提供了完全支持向量操作指令和符合IEEE32位浮點格式的頂點處理能力和像素處理能力,已經成為了一個強大的并行計算單元。研究人員將其應用于加速科學計算和可視化應用程序,取得了令人鼓舞的研究成果。 與CPU相比,GPU具有以下優勢:強大的并行處理能力和高效率的數據傳輸能

2017-12-01 12:23:05 902

902

帶有全球定位系統( GPS)功能設備的增多,產生大量的時空軌跡數據,給數據的存儲、傳輸和處理帶來了沉重的負擔。為了減輕這種負擔,各種軌跡壓縮方法也隨之產生。提出了一種基于MapReduce的并行化

2017-12-03 09:51:19 0

0 并行處理器指可以一次可處理多個運算的處理器。雙核處理器也是并行處理器,因為其一次可運行兩個運算(以此類推),但其本質上還是串行處理器的組合,所以提起并行處理器,一般指經特殊設計的多線程處理器。

2017-12-08 10:40:20 4382

4382 本文主要介紹了一種基于DSP+FPGA視頻圖像采集處理系統的設計與實現,DSP-BF561作為主處理器,負責整個算法的調度和數據流的控制,完成圖像數據的采集與顯示及核心算法的實現,FPGA作為DSP的協處理器,依托其高度的并行處理能力,完成圖像預處理中大量的累乘加運算。實驗證明系統達到了實時性要求。

2017-12-25 10:39:47 5649

5649

描述了浮點型算法的加、減、乘、除的verilog代碼,編寫了6位指數位,20位小數位的功能實現并且通過仿真驗證

2018-01-16 14:15:54 1

1 ,其速度直接影響DSP的速度,因此國內外學者對提高浮點乘加單元的性能進行了大量的研究。浮點運算單元的設計主要是在速度和所占用資源之間進行權衡。 本文以實時信號處理為應用背景,首先介紹了單精度浮點格式,然后從速度和占用

2018-04-10 10:47:21 8

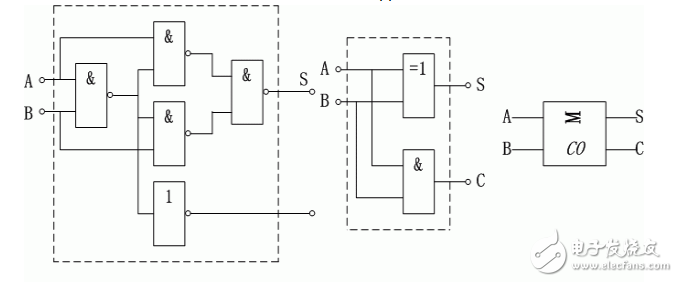

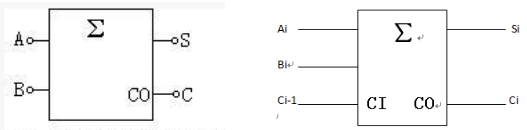

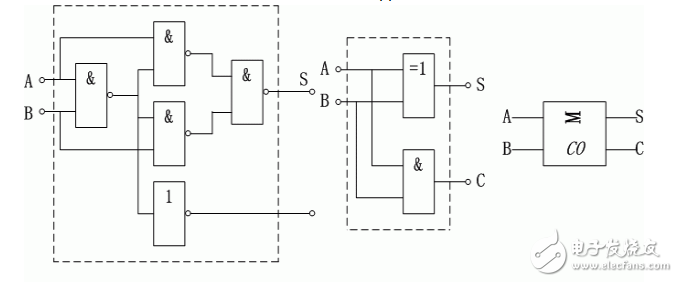

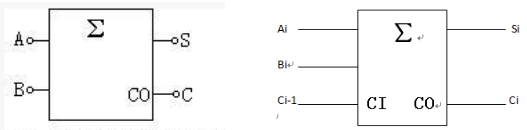

8 半加器+半加法和全加法是算術運算電路中的基本單元,它們是完成1位二進制相加的一種組合邏輯電路。

2018-07-25 11:37:16 345724

345724

計算機最基本的任務之一是進行算數,在機器中四則運算——加、減、乘、除——都是分解成加法運算進行的,因此加法器便成為計算機中最基本的運算單元。

2018-07-25 15:14:09 45170

45170

A)算術和邏輯運算,可對半字節(一個字節是8位,半個字節就是4位)和單字節數據進行操作。

B)加、減、乘、除、加1、減1、比較等算術運算。

C)與、或、異或、求補、循環等邏輯運算。

D)位處理功能(即布爾處理器)。

2019-09-14 17:20:00 5235

5235 指令均勻地分配給芯片中的眾多執行單元。本設計是針對VLIW微處理器的基本功能設計實現的,是針對64位指令字和192位數據進行操作處理,主要功能是將指令和數據分別劃分到3個并行操作單元中,在執行單元中根據3個并行指令控制,對3個并行操作單元的數據進行并行處理,同時對操作處理數據進行存儲處理管理。

2020-01-31 16:55:00 1576

1576

及布局布線,并用ModelSim和Matlab對設計作了聯合仿真。結果表明,通過利用FPGA器件中大量的乘法器、邏輯單元及存儲器等硬件資源,采用全并行加流水結構,可在一個時鐘節拍內完成32點FFT運算的功能,設計最高運算速度可達11 ns,可實現對高速A/D采樣數據的實時處理.

2021-03-31 15:22:00 11

11 乘的可擴展性是當前研究的熱點之一。本文提出一種新型的分布式并行稠密矩陣乘算法,即2.5D版本的PUMMA( Parallel Universal matrix Multiplication Algorithm)算法,該算法是通過將初始的進程分成c組,利用計算節點的額外內存,在每個進程組上同時

2021-06-01 14:33:43 5

5 基于MapReduce并行處理的機電特種設備故障診斷

2021-06-23 11:29:42 13

13 由STC89C52單片機+5乘4按鍵模塊+LCD1602液晶顯示屏+電源構成具體功能:利用輸入采用5×4矩陣鍵盤,可以進行加、減、乘、除等十幾種數字運算,并在LCD1602上顯示操作過程及結果。

2021-11-04 14:06:00 1

1 由STC89C52單片機+4乘4按鍵模塊+LCD1602液晶顯示屏+電源構成具體功能:利用輸入采用4×4矩陣鍵盤,可以進行加、減、乘、除等幾種數字運算,并在LCD1602上顯示操作過程及結果。

2021-11-05 10:50:59 1

1 系統由STC89C52單片機+4乘4按鍵模塊+LCD1602液晶顯示屏+電源構成。具體功能:利用輸入采用4×4矩陣鍵盤,可以進行加、減、乘、除等幾種數字運算,并在LCD1602上顯示操作過程及結果。

2021-11-23 16:51:21 2

2 基帶單元 (BBU) 是電信網絡中處理基帶信號的設備。BBU 充當基站的集中“樞紐”,處理上行鏈路和下行鏈路數據流量,并通過光纖控制 RRU(遠程無線電單元)功能。

2022-09-01 18:13:48 17837

17837 高性能圖形處理單元 (GPU) 的內部計算架構已從固定功能圖形執行單元發展為完全可編程的單指令多數據 (SIMD) 處理器陣列。這種演變是由視頻游戲社區的需求推動的,即并行執行通用物理計算,以使煙霧、碎片、火災和流體等行為更加逼真。

2022-11-07 15:12:33 981

981 和移位操作。這些結構需要占用器件較多的LE(邏輯元件)資源,設計周期長,工作頻率低,實時性差。本文提出一種基于Stratix系列FPGA器件的新的實時高速脈動FIR濾波器的快速實現方法。利 用FGPA集成的DSP(數字信號處理器)乘加模塊定制卷積運算單元,利用VHDL(甚高速集成電路硬件描述

2022-12-01 10:20:05 2154

2154 。Achronix為了解決這一大困境,創新地設計了機器學習處理器(MLP)單元,不僅支持浮點的乘加運算,還可以支持對多種定浮點數格式進行拆分。 MLP全稱Machine Learning Processing單元

2023-03-11 13:05:07 1285

1285 本文是本系列的第三篇,本文主要介紹FPGA常用運算模塊-乘加器,xilinx提供了相關的IP以便于用戶進行開發使用。

2023-05-22 16:17:12 2959

2959

電子發燒友網站提供《帶有初始化信號的0-9加/減計數器.zip》資料免費下載

2023-06-16 14:39:59 0

0 一種方法是分支預測,類似于預測下一個操作的方式,就像互聯網搜索引擎一樣。然而,與任何并行架構一樣,關鍵是確保各種處理單元充分運行,以最大限度地提高性能和效率。

2023-09-27 14:17:48 1476

1476

和功率調節功能。飽和變壓器的特點有很多,下面詳細介紹一下。 首先,飽和變壓器具有高精度的穩壓能力。由于它采用了飽和磁芯,其磁化曲線特性非常穩定,使得輸出電壓能夠在輸入電壓波動范圍內保持相對穩定。這就意味著飽和

2023-11-23 14:26:07 2131

2131 微處理器的執行單元(Execution Unit,簡稱EU)是微處理器中負責執行指令的核心部分,它集成了多種功能單元,共同協作完成算術運算、邏輯運算以及指令的譯碼和執行等任務。

2024-10-05 15:19:00 2287

2287 半加器和全加器是數字電路中的基本組件,用于執行二進制數的加法運算。它們在計算機、微處理器和其他數字系統中扮演著重要角色。 半加器的功能特點 半加器是一種簡單的數字電路,它能夠實現兩個一位二進制數

2024-10-18 11:10:50 6075

6075 摘要:汽車主動安全功能的日益發展,不僅豐富了車輛功能,也對其性能提出了更高的要求。自動駐車功能是主動安全功能中的一種,它能夠使車輛短暫駐車,但是該功能釋放過程中駕乘用戶會有頓挫感。分析了自動駐車功能

2025-02-14 10:21:37 1133

1133

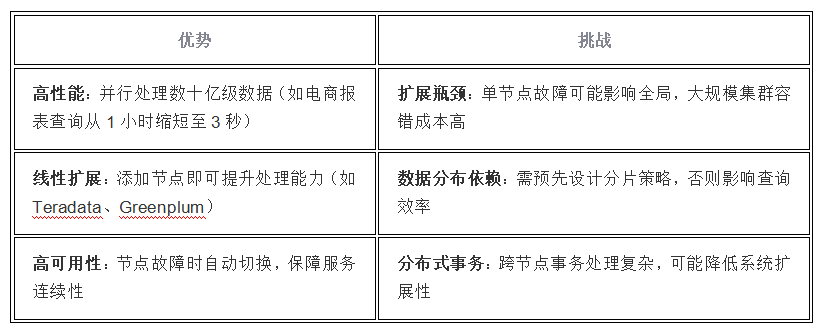

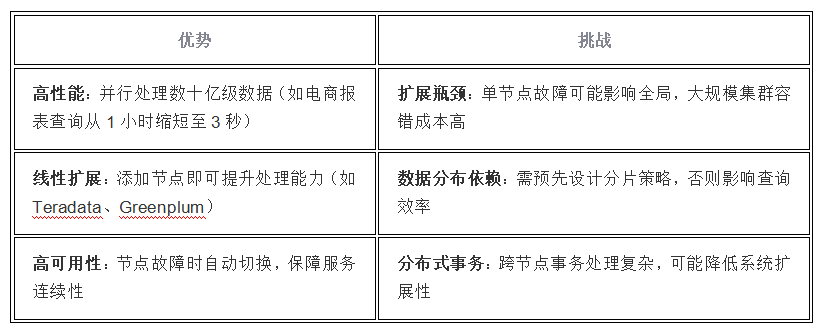

多節點并行處理架構(如MPP架構)通過分布式計算和存儲實現高性能數據處理,其核心設計及典型應用如下: 一、核心架構特征 非共享架構(Share Nothing)? 每個節點擁有獨立的計算資源(CPU

2025-06-12 08:18:36 532

532

電子發燒友App

電子發燒友App

評論