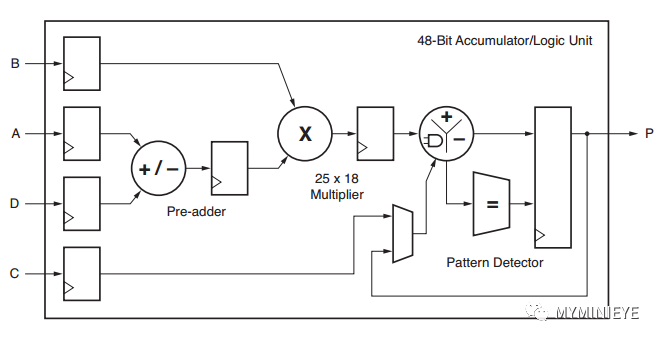

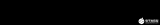

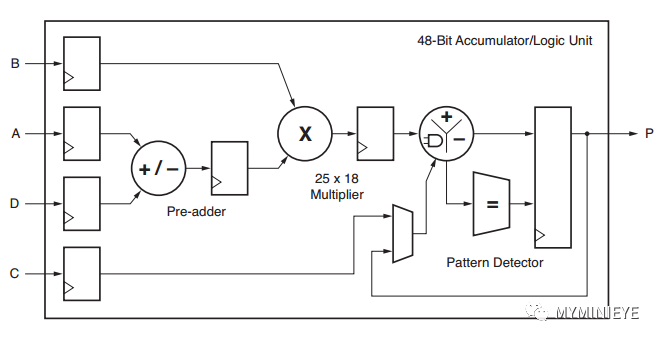

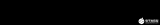

充分利用DSP資源,我們需要對DSP48E1有所了解。 1.DSP48E1介紹 DSP48E1是7系列的最小計算單元,DSP資源,支持許多獨立的功能,其基本功能如下所示 DSP48E1簡易模型 包括: 帶有D寄存器的25位預加法器 25*18二進制乘法 48位累加 三輸入加法 其他的一些功能還包括

2020-09-30 11:48:55 32566

32566

Kintex-7 FPGA的內部結構相比傳統FPGA的內部結構嵌入了DSP48E1,PCIE,GTX,XADC,高速IO口等單元,大大提升了FPGA的性能。

2023-08-24 09:26:56 3325

3325

和Spartan-6。我無法使用任何一個軟件套件編程任何設備。之前我使用Artix 100T編程了類似的設置,但似乎新的50T無法識別我的iMPACT。我也嘗試添加設備,但它沒有用。有沒有辦法更新ISE

2020-05-29 11:52:31

7 series FPGAs MultiBoot功能指讓FPGA從2個或者多個BIT文件中加載一個BIT文件運行程序,本文檔介紹基于個人參考設計例程K7MultiBoot的應用筆記

2019-04-05 00:25:27

模式下,48位加法器/減法器也支持雙24位或雙12位SIMD算術運算。在這種配置中,動態ALUMODE控制信號也支持對兩個48位二進制數的按位邏輯操作。 在DSP48E1列中,級聯各個DSP48E1片

2021-01-08 16:46:10

7系列FPGA DSP48E1片的特點什么

2021-03-05 06:26:41

我正在實例化DSP切片并進行簡單的乘法然后加法((A * B)+ C)。根據DSP48E1用戶指南,當使用所有三個流水線寄存器時,它給出了最高頻率為600 MHz。但就我而言,它使用流水線寄存器

2020-06-12 06:32:01

嗨,我有一個如下的指令:(D-A)* B + C.端口A,B,C,D與DSP48E1輸入引腳相對應。我試圖將整個操作打包在DSP單元中。 (順便說一句,我的數據寬度是8位)在布局和布線完成后,我

2019-04-01 14:25:40

在我的設計中,我需要延遲一些數據(32位寬)一段時間。我一直在使用SRL16而不是FFs,它可以很好地延遲超過幾個周期。我還注意到,使用DSP48E1片很容易將數據延遲到48位寬,延遲三個周期,因此

2019-04-18 06:40:33

DSP48E1屬性

2021-01-27 06:21:23

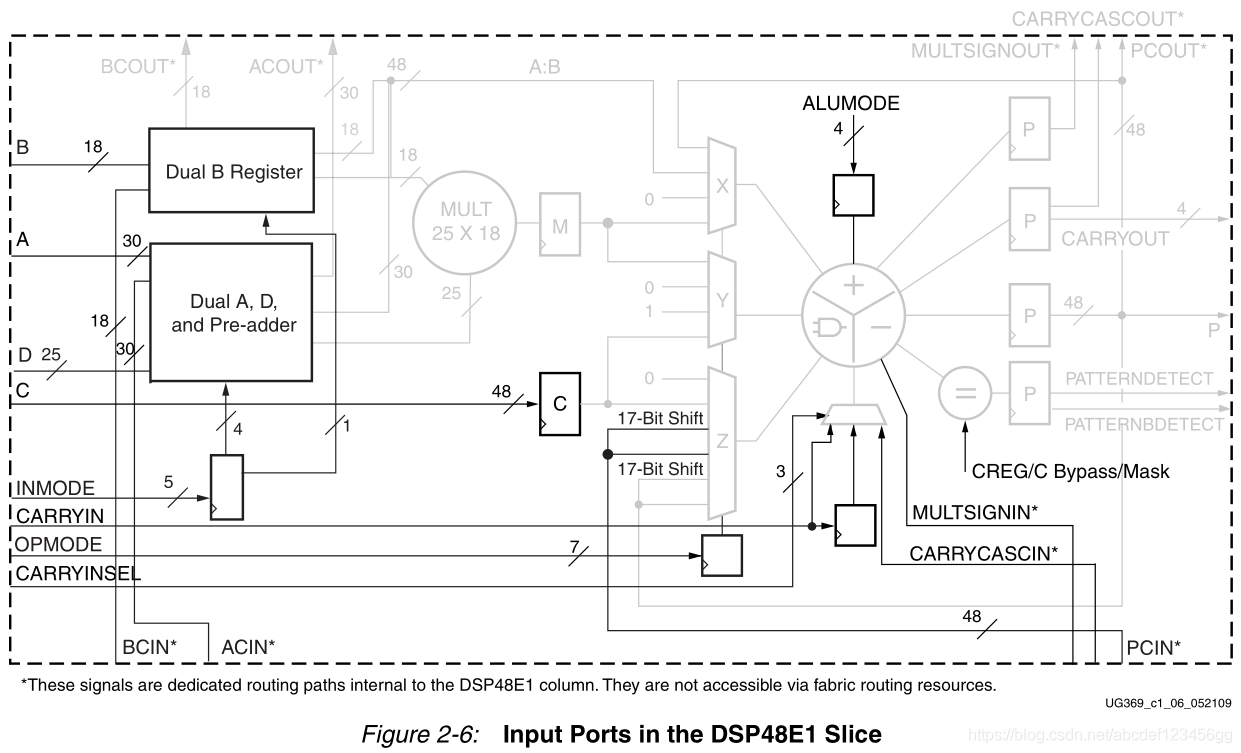

和RSTB復位(如圖2-7和圖2-8所示)。 P端口 每個DSP48E1片都有一個48位的輸出端口p。這個輸出可以通過PCOUT路徑內部連接(級聯連接)到相鄰的DSP48E1片。PCOUT連接

2020-12-23 16:54:08

Avnet 設計的 Artix-7 50T FPGA評估套件是完全可定制的開發工具套件,非常適合嵌入式設計人員對靈活低功耗平臺的需求。Artix–7 50T FPGA評估板是一套完整的系統,它把嵌入式處理器系統所需的所有功能和接口都集成到一個小小的芯片上。相關資料打包下載

2016-08-19 15:32:34

充分利用DSP資源,我們需要對DSP48E1有所了解。

1.DSP48E1介紹

DSP48E1是7系列的最小計算單元,DSP資源,支持許多獨立的功能,其基本功能如下所示

DSP48E1簡易模型

包括

2023-06-20 14:29:51

1600Mbps。其與FPGA的接口如下圖,主要引腳有:Data[0:15],DM[0:1],DQS[0:1],Address和Control 具體的FPGA引腳分配如下圖 對應FPGA中的BANK 15

2016-12-13 11:02:54

此篇先細致探索一下板卡的硬件資源。 如下圖所示,主要以Artix-7 50T FPGA為核心,外圍有電源管理和時鐘電路,通信、輸入輸出端口,和存儲器。電源管理: 板卡電源輸入有兩種方式1) 由DC

2016-12-12 22:12:39

嵌入式開發板,有豐富的外設,如網卡,u***2uart等,上手就純粹的接線就可以了。烙鐵是用不上的,杜邦接口也不用了,感覺清爽了很多。然后非常感謝同樣獲取試用機會的lijinqiu1(抱歉不會@),參考他

2016-10-24 18:50:16

工程時,在器件板卡選型時,可以選擇Boards面板,選擇Artix-7 50T Evaluation Board板卡。無需知道FPGA芯片詳細信息。5、在Block Design設計時,可以直接拖動板卡資源到設計面板中。這就是簡單的LED實例化過程,在嵌入式設計時,相當方便用戶使用。

2016-11-28 15:15:16

Digilent 的 PmodArtix-7 50T FPGA 評估套件 接口,支持 48 個用戶 I/O 引腳 8 個用戶 DIP 開關 雙 10/100 以太網接口 JTAG 編程/配置端口 配對適應雙倍寬度

2016-11-23 22:36:52

的設計維護和改進變得更為輕松。比如并沒有找到artix-7 50T驅動,逛ni、Avnet、xilinx都呵呵感謝ni的技術支持回復我的郵件!!!用labview,xilinx的編譯器就不要裝太高的版本ba

2016-12-21 10:56:25

模塊資料多一點,在TI官網可以下載到。FPGA采用安富利的Artix-7 50T開發板,具有52160個邏輯單元、2.7Mbit BRAM以及120個DSP48 slice,還有4個速度為

2016-12-29 11:25:39

bin_file!!! 在打開硬件管理器(Hardware Manager),并連接上板卡。 在hardware面板中右擊FPGA器件(xc7a50t),選擇Add Configuration Memery

2016-12-27 20:22:29

了Xilinx Artix-7FPGA的基本結構和性能,在此基礎上,就可以充分發揮該器件的特性,設計實用的系統了。 到此為止,關于7A50T開發板上的硬件資源就已經基本學習完成,下一節,將開始Xilinx 的FPGA開發流程的學習。 小梅哥2016年11月1日星期二于成都市電子科技大學

2016-11-01 15:52:18

收到一個白色紙箱,作為剁手party,拆快遞箱那快感不用多說了,打開紙箱,一塊板子,幾張說明書,還有數據線等配件 相比其它搭載高端FPGA芯片的開發板,Artix-7 50T開發板算是比較迷你的,當然

2016-11-01 14:40:21

外設資源等,如下幾篇博文:【Artix-7 50T FPGA試用體驗】二 板卡細探(一)【Artix-7 50T FPGA試用體驗】二 板卡細探(二) 一切就緒,開始上手FPGA調試和開發了,第一步

2016-12-19 08:12:39

以太網可以說是現今應用最廣泛的數據通信協議之一,本篇從物理層對以太網在Artix-7 50T開發板上應用進行評測。一、原理:按照技術發展以太網可以分為:標準以太網、快速以太網、千兆以太網和萬兆以太網

2016-12-13 20:07:58

LwIP在Artix-7 50T上的應用。 直接在官網上下載Artix-7 50T的LwIP參考設計,使用vivado 2014.4打開。 如下圖,為系統模塊圖,核心是microblaze軟核 具體可看如下

2016-12-14 15:56:23

接口連接到Artix-7FPGA上,從而實現了給7A50T板卡擴展16個485接口的功能。到此為止,關于通信管理機的硬件接口就已經全部搭建好了。系統框架也已經介紹完畢,下一步,該搭建該系統了。

2016-12-16 10:45:36

計(二)【Artix-7 50T FPGA試用體驗】基于7A50T FPGA開發套件的工業通信管理機設計(三)AXI接口【Artix-7 50T FPGA試用體驗】基于7A50T FPGA開發套件的工業

2016-12-27 10:36:50

本帖最后由 chy520cvv 于 2016-12-14 19:05 編輯

利用官方的板卡進行PetaLinux開發的好處之一就是文件資料豐富,同時會有相關支持。但是Artix-7 50T

2016-12-14 19:04:11

\2016.2\data\boards\board_parts Vivado軟件安裝的板卡文件下。拷貝xdc文件重啟Vivado,創建工程時,在器件板卡選型時,可以選擇Boards面板,選擇Artix-7 50T

2016-12-16 23:19:04

,進行IIC測試~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ ~~Artix-7 50T - IIC EEPROM Write/Read

2016-10-20 22:33:22

具體型號特點 FPGA主芯片XC7A50T-1FTG256C高性能低成本FPGA器件,含高速收發器 DDR3存儲器MT41K128M16JT-125:E256M字節DDR3存儲器 QSPI FLASH存儲器

2016-10-27 18:35:03

,Y 方向的投影數值保存下來,假如取8位寬 、,那么1個數字就是8bit*16的字符模板。2. 把這些模板矩陣存入FPGA 的內部RAM中作為標準模板庫。采用8×16 bit 大小的數組作為標準模板

2016-12-19 01:19:43

0x00000000Processor started. Type "stop" to stop processor RUNNING>E:\Artix-7 FPGA\開發板資料\7A50T

2016-10-29 15:05:43

`7A50T開發板試用報告之開箱這是我第一次接觸Xilinx的板卡和軟件,顯得誠惶誠恐,各種新概念迎面撲來,非常擔心力所不逮。然而為了感謝電子發燒友論壇,感謝Xilinx,感謝安富利公司對我的信任

2016-10-22 19:33:44

。 反面二、簡單測試接下來是串口測試,學生party不像老司機拿到板卡就調試串口,測試板卡的資源情況。希望以后養成這種習慣吧!我用的是串口調試助手1.3,測試數據如下:Artix-7 50T - IIC

2016-12-07 08:46:04

能夠符合Xilinx最新的工具軟件和器件系列,因此選擇7系列FPGA作為原型平臺。經朋友推薦,本開發板復雜度適中,學習開發,因此特申請使用該開發板進行學習開發相應的資料教程。本人擬從以下幾個方面展開試用

2016-10-11 18:15:20

申請理由:項目描述:本人將使用Artix-7 50T開發板進行圖像處理相關的開發測評,計劃如下:1. 通過PMOD接口連接圖像采集卡,圖像采集卡上有模擬攝像頭,通過ADC芯片將模擬信號轉化為數字信號

2016-10-11 18:15:33

,在此基礎上設計過基于FPGA的電子琴。同時此前在電子發燒友成功申請獲得過云路由和樹莓派的試用,認真對待每次試用機會,認真撰寫心得體會。如果獲得Artix-7 FPGA的試用機會,試用進度如下:1、認真閱讀

2016-11-10 12:34:54

為什么BUFG驅動DSP48E1的CE會出現問題?警告:LIT:683 - DSP48E1符號“Inst_control_loop / u_Subsystem11

2020-06-12 11:45:43

嗨,我想使用DSP45E1模塊實現Multply-Add操作,其中一個要求是我需要DSP模塊上的3級流水線。查看UG479 7系列DSP48E1 Slice用戶指南(UG479) - Xilinx

2020-07-21 13:52:24

48位動態比較。這使得諸如A:B NAND C = = 0或A:B(按位邏輯)C = =模式等函數得以實現。 圖2-5以非常簡化的形式顯示了DSP48E1片。7個OPMODE位控制X、Y和Z多路復用

2021-01-08 16:36:32

簡化DSP48E1片操作

2021-01-27 07:13:57

我一直在嘗試將DSP48E1原語用于具有自動終端計數重置的計數器。大部分工作都很好,但我看到的一個問題是我無法讓DSP48E1進行模式檢測0.如果我將C輸入設置為48'd0,則在P =開始時

2020-07-28 10:38:40

據我所知,乘法默認由FPGA中的DSP48E1片處理。有沒有什么方法可以禁用或自定義DSP48E1元素用于自己的新算法?我的目標是使用我的乘法算法,而不是使用FPGA中的現有DSP算法。請指教。謝謝。

2020-05-04 15:22:35

,這是新型xilinx產品的基礎架構,因此DSP-Slices和CLB的寬度可能相等,但我找不到確認的信息。如果有人能夠提供有關7系列FPGA中CLB,DSP48E1和BRAM36K / BRAM18K之間水平關系的信息,將會非常有幫助。

2020-07-25 11:04:42

基于Artix-7 50T FPGA開發板的近距離感應器Pmod設計示例(Vivado 2014.4 - Proximity Sensor Pmod Example Design

2016-08-03 20:40:36 52

52 Artix-7 50T FPGAEthernetLite應用實例,This example design utilizes the light-weight IP (lwIP) protocol

2016-08-04 09:04:27 204

204 Artix-7 50T FPGA開發板接口功能測試實例,This document describes a MicroBlazeTM design implemented and tested on the Xilinx Artix-7 50T Evaluation board。

2016-08-04 09:17:07 198

198 概述 Xilinx的DSP48E1模塊在7系列的fpga芯片中經常被用于DSP應用當中。他能夠有效提高設計的靈活性和效率,提高產品的性能。 DSP48E1支持許多獨立的功能。包括:乘法、乘加

2017-02-08 01:07:12 1174

1174

概述 利用4個dsp48e1模塊,實現四路加法器,dsp48e1模塊在手冊中表示比較復雜,找了兩個圖,可以大致看懂他的基本功能。 圖1 dsp48e1端口說明 圖2 簡化的DSP48E1結構 軟件

2017-02-08 01:10:08 994

994

作為Xlinx-FPGA的學習者,學習之路頗為坎坷。在感慨Xilinx高大上的同時不得不吐槽真貴,特別是好的開發板(在這里真誠感謝xilinx電子創新網提供的試用板)。同時高冷的Xilinx在學

2017-02-08 02:09:03 525

525

基于Artix-7 50T的多傳感器數據融合 6 徐鵬 基于FPGA的動態視頻監控(安防) 試用須知: 1、收到開發板之日起每2周必須發布一篇

2017-02-08 12:13:34 439

439 為了適應越來越復雜的DSP運算,Virtex-6中嵌入了功能更強大的DSP48E1 SLICE,簡化的DSP48E1模塊如圖5-16所示。

2017-02-11 09:17:13 1946

1946

在本視頻中,您將了解Artix-7 FPGA的整體系統功耗和成本。

我們將快速回顧一下Artix-7 FPGA架構,邏輯架構,第四代DSP48E1片,6.6 Gbps GTP收發器,PCIe Gen2硬塊,存儲器接口,模擬..

2018-11-21 06:10:00 4336

4336 Artix-7 A100T FPGA提供同類產品中最高的DSP帶寬。

2018-11-27 07:00:00 5391

5391 本用戶指南詳細介紹了Spartan?6 FPGA中DSP48A1芯片的功能。

本章提供了Spartan-6 FPGA(DSP48A1芯片)中數字信號處理(DSP)元件的技術細節。每個DSP48A1

2019-02-15 14:42:38 31

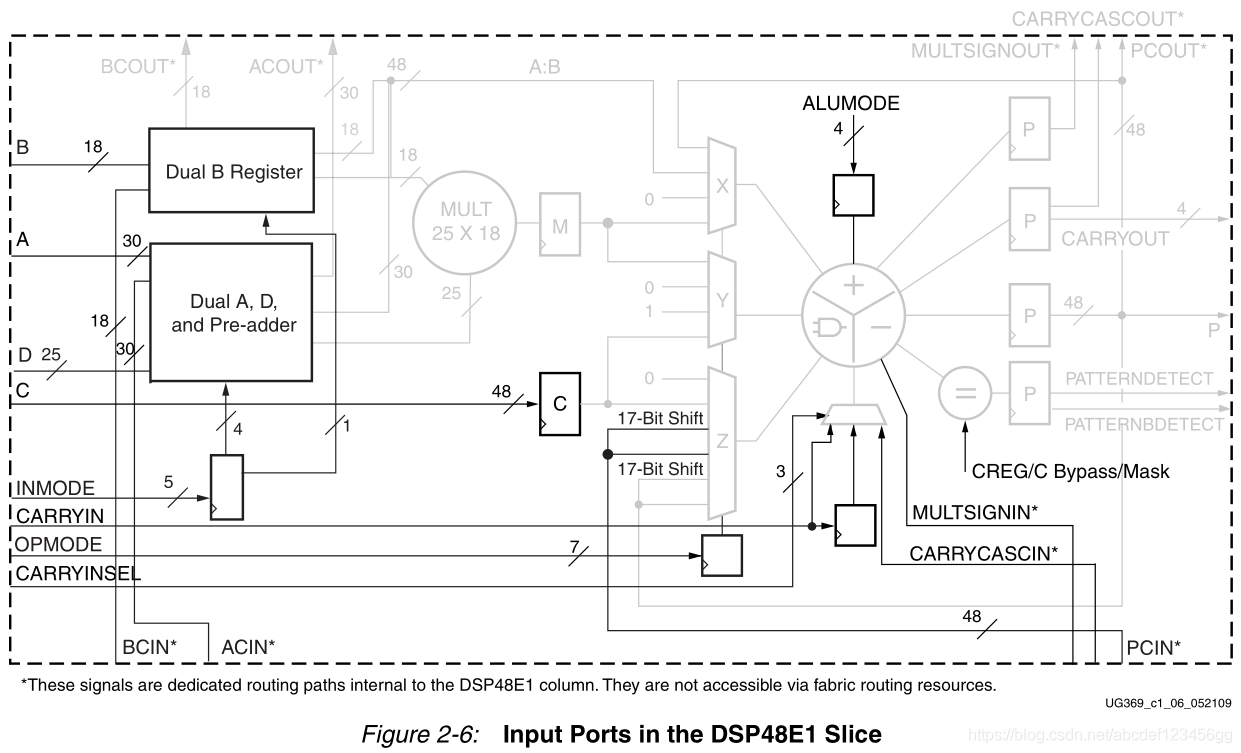

31 A、B、C、CARRYIN、CARRYINSEL、OPMODE、BCIN、PCIN、ACIN、ALUMODE、CARRYCASCIN、MULTSIGNIN以及相應的時鐘啟用輸入和復位輸入都是保留端口。D和INMODE端口對于DSP48E1片是唯一的。本節詳細描述DSP48E1片的輸入端口

2022-07-25 18:00:18 6751

6751

DSP48E1片的數學部分由一個25位的預加器、2個25位、18位的補法器和3個48位的數據路徑多路復用器(具有輸出X、Y和Z)組成,然后是一個3輸入加法器/減法器或2輸入邏輯單元(參見圖2-5)。使用2輸入邏輯單元時,不能使用乘法器。

2022-01-21 14:14:26 1829

1829 在DSP48E1列中,級聯各個DSP48E1片可以支持更高級的DSP功能。兩個數據路徑(ACOUT和BCOUT)和DSP48E1片輸出(PCOUT、MULTSIGNOUT和CARRYCASCOUT)提供級聯功能。級聯數據路徑的能力在過濾器設計中很有用。

2022-06-21 08:55:00 3249

3249 在DSP48E1列中,級聯各個DSP48E1片可以支持更高級的DSP功能。兩個數據路徑(ACOUT和BCOUT)和DSP48E1片輸出(PCOUT、MULTSIGNOUT和CARRYCASCOUT)提供級聯功能。級聯數據路徑的能力在過濾器設計中很有用。

2021-01-27 07:34:32 10

10 A、B、C、CARRYIN、CARRYINSEL、OPMODE、BCIN、PCIN、ACIN、ALUMODE、CARRYCASCIN、MULTSIGNIN以及相應的時鐘啟用輸入和復位輸入都是保留端口。D和INMODE端口對于DSP48E1片是唯一的。本節詳細描述DSP48E1片的輸入端口

2021-01-27 08:18:02 2

2 DSP48E1片的數學部分由一個25位的預加器、2個25位、18位的補法器和3個48位的數據路徑多路復用器(具有輸出X、Y和Z)組成,然后是一個3輸入加法器/減法器或2輸入邏輯單元(參見圖2-5)。使用2輸入邏輯單元時,不能使用乘法器。

2021-01-29 08:19:37 13

13 電子發燒友網站提供《ES7P7021應用筆記.pdf》資料免費下載

2022-09-22 14:52:57 3

3 電子發燒友網站提供《ES7P2131應用筆記.pdf》資料免費下載

2022-09-22 14:46:38 2

2 電子發燒友網站提供《ES7P0693應用筆記.pdf》資料免費下載

2022-09-22 14:34:12 8

8 電子發燒友網站提供《ES7P2032應用筆記.pdf》資料免費下載

2022-09-22 11:22:45 0

0 電子發燒友網站提供《ES7P1751應用筆記.pdf》資料免費下載

2022-09-22 10:58:44 0

0 電子發燒友網站提供《HR7P275應用筆記.pdf》資料免費下載

2022-09-22 10:20:30 0

0 電子發燒友網站提供《HR7P195應用筆記.zip》資料免費下載

2022-09-22 10:19:17 1

1 電子發燒友網站提供《HR7P154應用筆記.zip》資料免費下載

2022-09-22 10:13:15 0

0 電子發燒友網站提供《ES7P003應用筆記.pdf》資料免費下載

2022-09-22 10:05:16 2

2 電子發燒友網站提供《ES7P001應用筆記.pdf》資料免費下載

2022-09-22 10:02:10 4

4 電子發燒友網站提供《ES7P1391應用筆記.pdf》資料免費下載

2022-09-22 09:58:39 0

0 電子發燒友網站提供《HR7P153應用筆記.zip》資料免費下載

2022-09-22 09:29:16 3

3 電子發燒友網站提供《HR7P201應用筆記.pdf》資料免費下載

2022-09-22 09:23:05 3

3 STK682-010-E 應用筆記

2022-11-14 21:08:09 8

8 STK541UC62K-E 應用筆記

2022-11-14 21:08:10 0

0 STK672-440AN-E、STK672-442AN-E 應用筆記

2022-11-15 19:55:47 2

2 STK681-360-E 應用筆記

2022-11-15 20:31:04 0

0 本應用筆記提供了使用達拉斯半導體/Maxim通信產品T1/E1單芯片收發器(SCT)和T1/E1成幀器的小數T1和E1電路設計示例。

2023-01-10 14:09:48 2590

2590

以運用。 運行狀況檢查器件 本應用筆記目標軟件的運行狀況使用以下器件進行檢查。 RA6T2 (R7FA6T2BD3CFP) 目錄 1.概

2023-05-17 13:35:01 1573

1573

上文 FPGA數字信號處理之濾波器2_使用dsp48e1的fir濾波器設計完成了結構設計。

2023-06-02 12:36:22 2487

2487

AG256SL100PINtoPINEMP240T100CxNAG256SL100PINtoPINEMP240T100IxNAG1280Q48替代AlteraEPM1270AG1KLPQ48替代LatticeICE5LP1KFPGAfamilydevice-AG1Kisultra-lowcostandpowerwithaslowas50uAstandbycu

2022-03-01 10:40:02 2547

2547

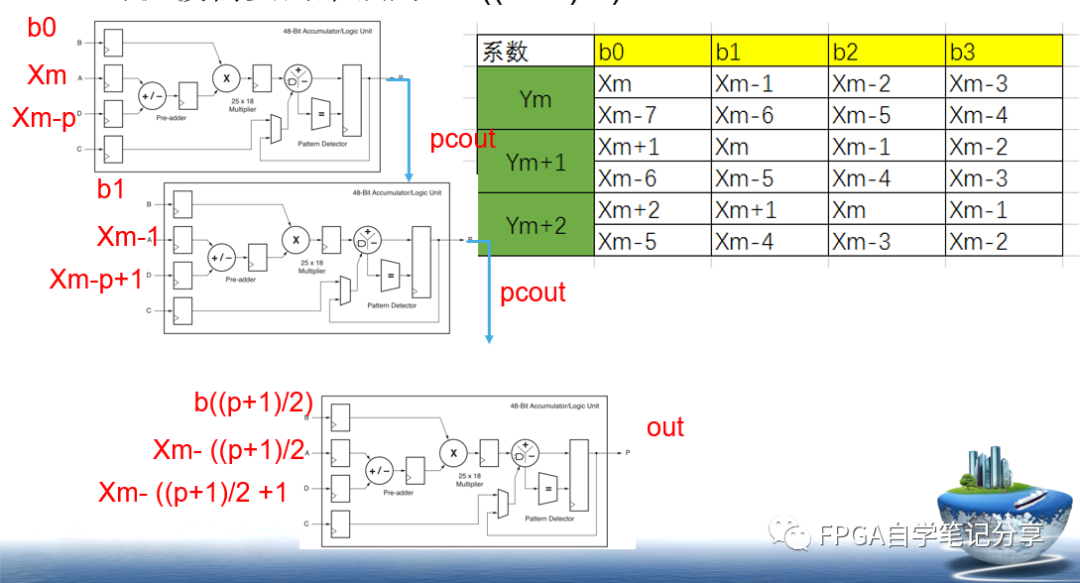

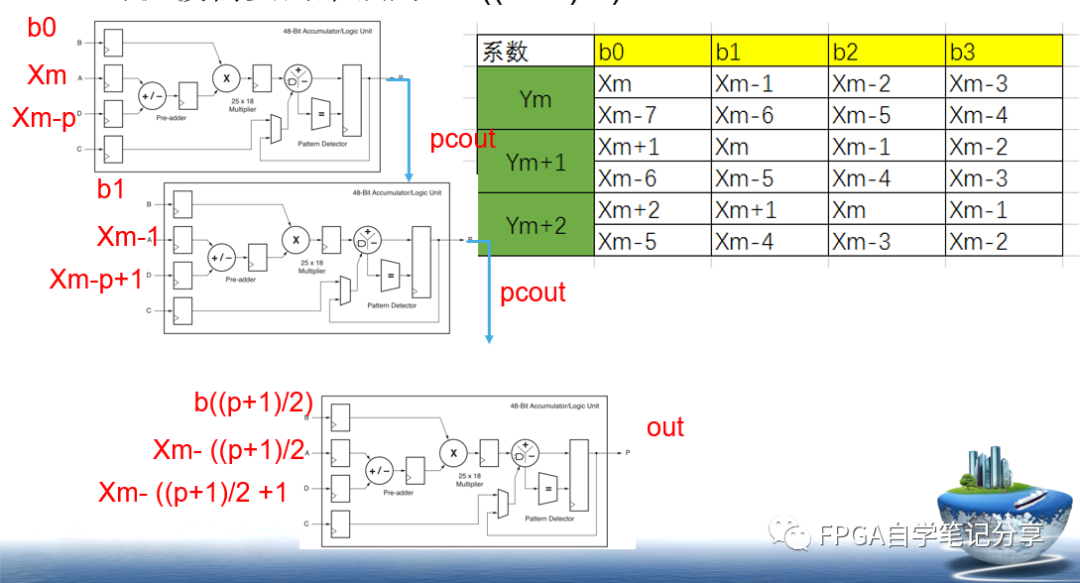

HK32MCU應用筆記(二十)| HK32F103xC/D/E USB枚舉情況分析(二)

2023-09-18 10:58:22 1373

1373

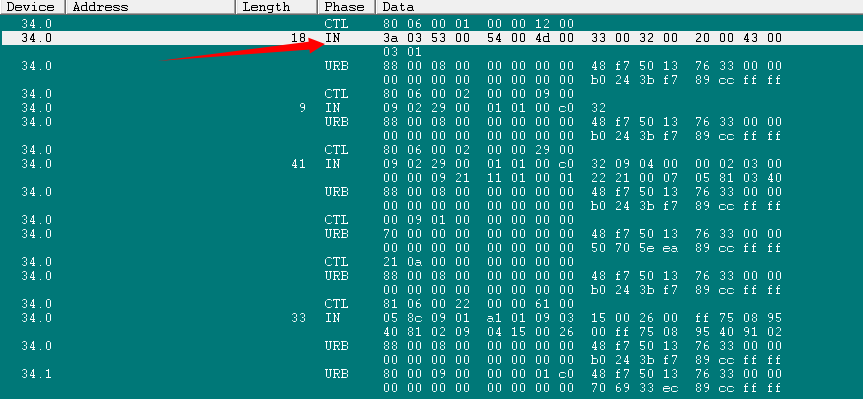

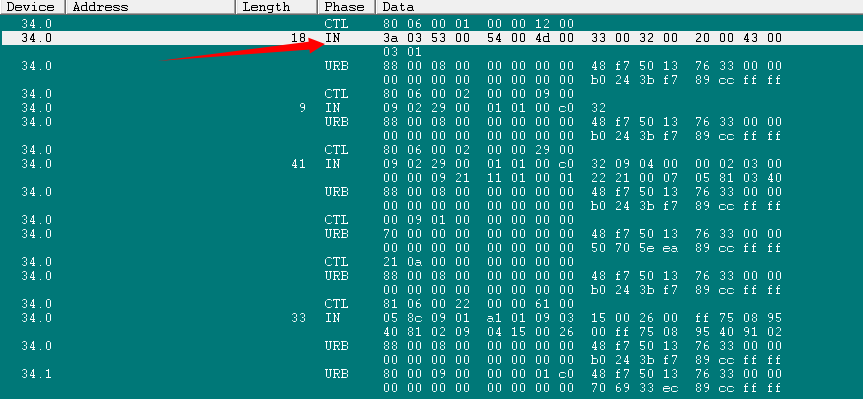

HK32MCU應用筆記(十四)| HK32F103x/C/D/E-TIM1的應用及注意事項

2023-09-18 10:58:36 1645

1645

電子發燒友網站提供《ES7P0214應用筆記.pdf》資料免費下載

2025-01-16 16:06:21 0

0 電子發燒友網站提供《ES7P0213應用筆記.pdf》資料免費下載

2025-01-16 15:26:55 0

0

電子發燒友App

電子發燒友App

評論