賽靈思公司今天宣布推出全球最大容量的 FPGA – Virtex UltraScale+ VU19P,從而進一步擴展了旗下 16 納米 (nm) Virtex? UltraScale+? 產品系列。

2019-08-24 09:09:07 4288

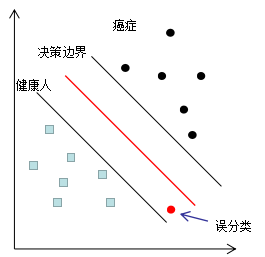

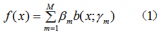

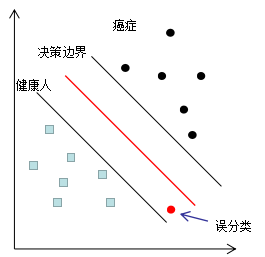

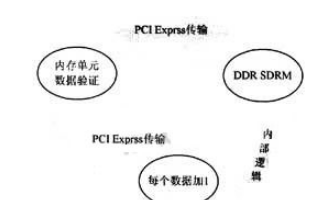

4288 Adaboost 算法是Freund 和Schapire 于1995 年提出的,全稱為Adaptive Boosting。它是 Boosting 算法的改進,意為該算法通過機器訓練與學習不斷自適應地調整假設的錯誤率,這 種靈活性使得Adaboost 算法很容易與實際應用聯系起來。

2019-08-28 07:05:11

VIRTEX-5FPGA - DC and Switching Characteristics - Xilinx, Inc

2022-11-04 17:22:44

使用Virtex5就可以了。我嘗試了Xilinx ISE 10.1.02和9.2.04i - 結果相同。我讀了AR#31574。我認為這不是我的情況。我使用“-ignore_keep_hierarchy”選項

2020-06-01 16:50:55

Virtex5無法正確讀取XCF32P。 Impact可以編程到PROM和VIRTEX5,但是當Virtex5上電時,看起來PROM只在D0上輸出串行數據,D1..D7為高電平(3.3V

2020-05-27 13:35:05

類型為'ABC_sig_div_16_5_2clk'的邏輯根塊'ABC_sig_div_16_5_2clk'未展開。目標'virtex5'不支持符號'ABC_sig_div_16_5_2clk'。我在

2018-09-28 11:35:48

嗨,我正在使用virtex5,我想設置rocketIO。我紅了很多文檔和用戶指南,但因為有太多的東西我迷路了,我不知道如何開始。感謝向導,我能夠生成IP核,但是在我失去了實現IP核之后。在生成的例子

2020-06-04 11:19:14

嗨,我正在一個項目中工作,我需要直接使用我的設計ICAP_VIRTEX5。我記得2年前曾讀過關于這個街區的事情,但現在我再也找不到了。此外,我不只是談論Virtex5的HDL文檔或其中一個

2020-06-17 16:35:39

嗨,我想在FPGA中捕獲串行ADC樣本。我將ADS5281(12位,50Msps)連接到Virtex5 SX95T。ADC時鐘和數據饋入Virtex5中的iDDR。如果adc時鐘低至120 MHz

2020-04-17 09:26:34

18 幅圖像的速度每秒處理 3,015 幅圖像。? 這些數字表明,英特爾 Stratix 10 FPGA 在處理大批量任務時完全可媲美其他高性能計算(HPC)器件(如 GPU), 在處理小批量任務時則比其他器件更快。

2019-07-17 06:34:16

? Spartan6是否包含基板高性能電容器,如Virtex5和6?具有推薦的旁路上限值的其他人的經驗是什么?謝謝!以上來自于谷歌翻譯以下為原文We're laying outa Spartan 6

2019-05-29 07:36:22

Stratix III FPGA與Xilinx Virtex-5的體系結構對比Stratix III FPGA與Xilinx Virtex-5的性能對比

2021-05-07 07:00:14

產物。Xilinx Virtex-II 系列平臺 FPGA 提供了現有任何可編程邏輯解決方案的最高性能和最高密度。基準測試程序表明,該系列產品在系統性能上比最相近的競爭器件高出 38%。盡管容量從四萬到八百萬系統

2013-09-06 16:28:27

你好,我使用Xilinx Virtex5,我安裝了ISE Suit Desgin。系統生成器配置有Matlab R2013a。當我啟動系統生成器時,matlab打開,幾秒鐘后它會自動關閉。有時它會給我一個錯誤:未知的軟件異常0xc00000d。你能幫我解決這個問題嗎?親切的

2020-05-18 08:39:45

你好,我正在通過平臺電纜USB使用帶有iMPACT的Virtex5編程公司板。我正在使用JTAG模式,“初始化鏈”可以識別微處理器和FPGA并提示輸入bsd / bit文件。提供這些后,我可以成功

2020-06-02 10:30:49

你好,我正在嘗試在zynq設備上實現一個設計。我已經在Virtex5設備上實現了它,它的工作非常好。但是當我更改設備時,我在放置和路由階段得到了以下錯誤。我更改了UCF文件,但我不明白這個錯誤

2018-10-15 11:52:53

為什么推出Virtex-5LXT FPGA平臺和IP解決方案?如何打造一個適用于星形系統和網狀系統的串行背板結構接口FPGA?

2021-04-29 06:18:31

嗨, 我正在開發一種設計,我們的主板有1個virtex5 fpga和9個從屬卡,每個都有1個V5 fpga。我想同步所有9個從卡的操作。我還希望主卡和從卡之間的數據傳輸速率為300-400Mbps

2019-01-30 06:52:36

嗨,Actuallay我正在研究Xilinx大學計劃的Virtex5評估委員會,我有兩個問題:第一個是,以太網應用需要與Virtex5一起使用的硬件資源是什么,換句話說,如果我應該傳輸基于V5

2020-06-02 06:20:56

各位前輩好!我在用Xilinx Virtex5 FPGA做通過千兆網和上位機通信,有幾個問題想請教:1、tri-mode ethernet mac 和 virtex-5 embedded

2016-05-31 22:41:53

嗨我正在回讀并擦洗XC5VFX130T,當在Virtex5中清除部分配置存儲器時,DONE引腳的行為是什么?保持高電平還是取消激活?不管怎么說,還是要謝謝你!handoujack。

2020-06-16 16:11:39

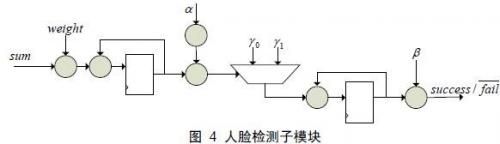

【作者】:鄭夜星;林其偉;【來源】:《電視技術》2010年02期【摘要】:提出在增強層中引入一種快速的AdaBoost人臉檢測算法,定位出人臉區域,進行位平面提升,優先傳輸。在基本層引入基于增強層

2010-04-23 11:23:20

的數據可以被寫入 Virtex-5 FPGA 中的內置 FIFO36 模塊。基于 CQ 的數據采集機制要求將讀時鐘(CQ 和 CQ)置于 clock-capable I/O (CCIO) 中,時鐘從這

2019-04-22 07:00:07

嗨, 我使用的是Virtex-5 FPGA,DDR2 MIG,我的ISE版本是13.2。 我的phy_init_done信號沒有被斷言。我發現校準序列卡在階段2.階段3從未到達。請提供有關上述原因的信息?

2020-06-15 11:52:03

是否可以將Spartan3 FPGA的3.3V LVCMOS o / ps連接到Virtex 5的2.5V LVCMOS輸入,反之亦然。

2020-06-16 14:42:03

AdaBoost算法實現

2019-11-07 09:19:29

你好我在virtex5 FX200T中使用LogiCORE IP SerialRapidIO v5.6 ipcore。1)我的查詢是提供的用戶指南,ug503不包含任何模擬結果,任何人都可以幫我驗證我的設計。2)如果可能,請參閱包含ipcore詳細說明的文件。謝謝&問候,馬杜

2020-03-17 09:46:07

大家好我們必須寫一個vhdl解碼器代碼解碼器特別是用狀態機構建我們怎么知道對于一個FPGA的好工作有多少狀態(例如virtex5 FX100t)?謝謝你的回答沙洛姆以上來自于谷歌翻譯以下為原文

2019-01-17 09:18:12

大家好,我對FPGA技術還不熟悉,而且我正在學習。我對DDR2 SRAM感到困惑,當我創建一個程序時...說一個寄存器,fifo等,數據是存儲在Virtex5部分還是存儲在板上的SRAM內存中?謝謝!-Mike!

2020-05-27 12:20:31

嗨,我是學生 我嘗試使用virtex5與部分重新配置教程UG702,但本教程設計為virtex6(ML605)所以我需要修復它 為virtex5創建新的綜合和網表(從源代碼復制.v文件并運行合成

2020-06-16 07:28:38

剛剛學習FPGA,不知道怎么用virtex5,想看看例程,網上找不到,想問問各位大神,能給給看看么

2014-12-03 21:56:05

請問有沒有基于太空級Virtex FPGA的靈活高性能計算平臺?

2021-04-15 06:01:10

大家好我正在使用Virtex5 FPGA,我在設計中添加了一個OFFSET IN約束,如下所示。NET“Sysclk”TNM_NET =“Sysclk”;TIMESPEC“TS_Sysclk

2020-06-13 19:23:05

“u_fifo_generator_v9_3”。引腳名稱拼寫錯誤可能導致此問題,缺少edif或ngc文件,塊名稱與edif或ngc文件名之間的大小寫不匹配,或者類型名稱的拼寫錯誤。目標'virtex5'不支持符號'fifo_generator_v9_3'。你能幫我解決一下這個問題嗎?

2020-04-26 12:14:08

你好朋友, 我已經獲得了Virtex5 FPGA應用筆記XAPP856,根據圖6和表3,我們不能使用DCM和BUFG驅動OSERDES來實現SFI-4.1。因為Virtex 5系列中的DCM最多可以

2020-06-10 12:48:08

誰有Virtex5 FPGA到TI公司64系列的EMIF設計文檔??如果有的話,發給我一下,多謝啦

2012-11-22 15:24:57

【來源】:《電子設計工程》2010年02期【摘要】:<正>賽靈思公司與聯華電子共同宣布,采用聯華電子高性能40nm工藝的Virtex-6FPGA,已經完全通過生產前的驗證

2010-04-24 09:06:05

我在同一JTAG鏈上有一個帶有8個器件的電路板:4個Xilinx XCF32P閃存,2個Xilnix Virtex-5 LX155和2個Broadcom PHY。4個Xilinx EPROMS和2個

2020-06-03 12:38:25

賽靈思多平臺Virtex-4 FPGA的性能及應用

賽靈思(Xilinx)的Virtex-4現場可編程門陣列(FPGA)是首款基于ASMBL(Advanced Silicon Modular Block)架構的多平臺FPGA系列。通過采用不同的平臺(LX、FX

2009-06-26 08:11:39 41

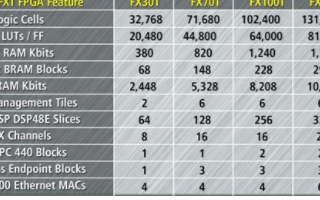

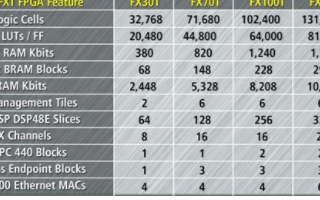

41 Xilinx公司的Virtex-5 FXT FPGA器件在業界率先集成了嵌入式PowerPC 440處理器模塊、高速RocketIO GTX收發器和專用XtremeDSP 處理能力。作為65nm Virtex-5系列的第四款平臺,Virtex-5 FXT提供了極高的

2009-11-24 11:17:22 33

33 賽靈思宣布開始向市場交付針對高性能數字信號處理(DSP)而優化的65 nm Virtex-5 SXT現場可編程門陣列(FPGA)器件的首批產品。SXT平臺創造了DSP性能的行業新紀錄--550MHz下性能達352 GMAC

2009-11-28 14:08:02 23

23 Virtex 一5LXl10 的ASlC 原型開發平臺設計北京工業大學 駱名森 樓煌摘要: 本文基于Viitex 一5 LX110 驗證平臺的設計,探索了高性能FPGA 硬件系統設計的一般性方法及流程,以提

2010-02-08 09:54:54 14

14 Virtex-5FPGA系列器件自帶的系統監測器模塊為數字多普勒接收機中片上溫度和供應電壓的監測提供一種簡單而高效的解決方案。在Xilinx ISE10.1開發平臺中,利用Xilinx提供的系統監測器模

2010-02-11 11:09:59 24

24 Virtex-5, Spartan-DSP FPGAs Application Note

This application note demonstrates how efficient

2010-03-08 09:47:48 71

71 Virtex-4 FPGA應用指南

使用Virtex-4器件的DDR2控制器(267MHz及以上)

DDR2SDRAM器件提供了比DDRSDRAM指標所要求的更好的新功能,并允許DDR2器件以666Mb/s的數據

2010-05-13 14:14:26 39

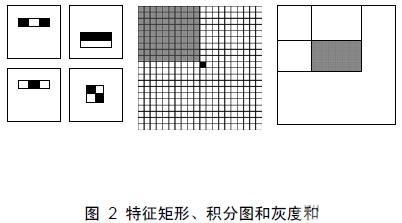

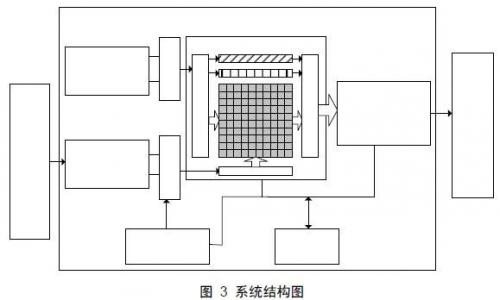

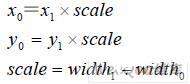

39 Adaboost算法采用由弱到強的級聯型分類器用以快速檢測人臉。但在實際應用中計算量巨大。在PC機上用純軟件實現該算法得到的目標檢測速度也難以達到實時。本文論述了一種采用像

2010-07-17 18:11:57 22

22

針對傳統模擬電路閾值檢測方法存在的缺點,設計出采用高速A/D轉換器和高性能Virtex5 FPGA實現激光測距系統。該系統可以大大降低系統誤差,提高測距精度。

2010-12-17 16:29:11 47

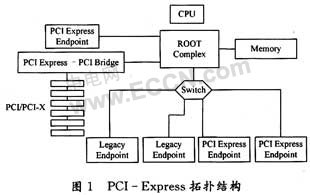

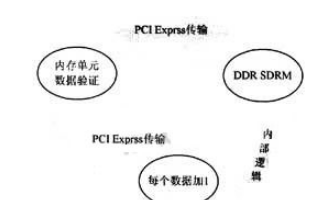

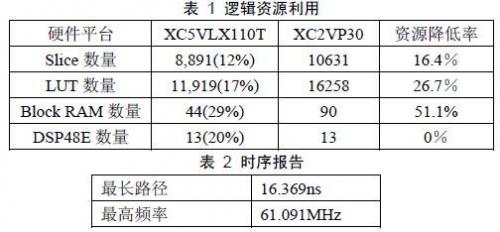

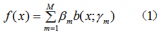

47 基于Virtex5的PCI-Express總線接口設計

PCI Express是由Intel,Dell,Compaq,IBM,Microsoft等PCI SIG聯合成立的Arapahoe Work Group共同草擬并推舉成取代PCI總線標準的

2009-10-05 10:25:20 1203

1203

賽靈思高性能40nm Virtex-6 FPGA系列即將轉入量產

賽靈思公司(Xilinx, Inc.)與聯華電子(UMC)今天共同宣布,采用聯華電子高性能40nm工藝的Virtex-6 FPGA,已經完全通過生產前的驗

2010-01-26 08:49:17 1145

1145 Opal Kelly推出基于Virtex-5的USB集成模塊

?總部位于俄勒岡州波特蘭的 Opal Kelly 公司專門從事基于 FPGA 的 USB 模塊開發,現推出了基于賽靈思 Virtex?-5 FPGA 的 USB 集成模

2010-02-08 10:11:13 1355

1355 基于電源模塊、外部存儲器和FPGA 器件等具體分析了融合系統的低功耗設計。FPGA 器件選擇了Xilinx 公司針對高性能信號處理的Virtex24 SX35 三百萬門級芯片,電源模塊采用TI 公司的兩片TPS5

2011-05-14 11:09:24 34

34 Xilinx Virtex-5 SXT FPGA 平臺提供了獨特的單芯片解決方案,充分利用大規模并行計算達到超高性能,同時將功耗降到最低。

2011-08-20 15:22:35 5576

5576

Virtex-7 2000T FPGA的容量是市場同類最大28nm器件的2倍,而且比賽靈思最大型Virtex-6 FPGA大2.5倍。雖然2000T由4個切片組成,但它仍然保持著傳統FPGA的使用模式,設計人員可通過賽靈思工具流程

2011-10-26 09:11:30 5573

5573 Virtex-5 系列可提供 FPGA 市場中最新最強大的功能。Virtex-5 系列采用第二代高級芯片組合模塊 (ASMBLTM) 列式架構,包含 5 個截然不同的平臺(子系列),是 FPGA 系列中選擇最為豐富的系列

2012-01-17 15:11:06 7

7 由于Virtex-5 器件的基礎架構與以往的FPGA 器件不同,因此,要為特定設計選擇合適的Virtex-5 器件并非易事。大多數情況下,設計應采用類似的陣列大小(器件數量)并且比以前的目標器

2012-01-17 17:36:22 33

33 Virtex-5 器件包括基于第二代高級硅片組合模塊 (ASMBL) 列架構的多平臺 FPGA 系列。集成了為獲得最佳性能、更高集成度和更低功耗設計的若干新型架構元件,Virtex-5 器件達到了比以往更高

2012-02-17 14:39:56 51

51 為解決北斗導航接收機干擾功率強、有效信號弱的不足,提出了一種基于功率倒置自適應算法的抗干擾設計方案。該方案以自適應天線系統為平臺,采用FPGA處理器Virtex5芯片實現自適應

2012-03-20 10:48:17 68

68 針對GPS接收機有效信號弱,易受窄帶干擾影響的不足,提出了一種基于FPGA的窄帶干擾抑制算法的實現方案。該方案以Xilinx公司的Virtex5芯片為硬件平臺,采用重疊加窗頻域濾波算法和自

2013-09-23 15:16:43 45

45 基于AdaBoost_Bayes算法的中文文本分類系統_徐凱

2017-01-07 18:56:13 2

2 Virtex? UltraScale+? FPGA VCU118 評估套件采用可在 FinFET 節點提供最高性能及各種集成功能的 Virtex UltraScale+ FPGA,是加速超高帶寬應用的理想開發環境。

2017-01-13 12:52:11 3491

3491 Virtex UltraScale? FPGA VCU108 評估套件是評估 Virtex UltraScale 器件所提供前所未有高性能、高系統集成度以及高帶寬的完美開發環境。該套件是需要海量

2017-02-08 14:19:11 748

748 部分可重構技術是Xilinx FPGA的一項重要開發流程。本文結合Virtex5 FPGA,詳細講解在ISE + Planahead上完成部分可重構功能的流程和技術要點。

2018-07-04 02:17:00 4583

4583

/100/1000Mbps,同時具有系統監視器和ADC,增強性配置和比特流保護,廣泛用在有線通信,無線通信和廣播設備。Virtex-6 FPGA是目標設計平臺的可編程的芯片基礎,這一平臺提供了集成的軟件和硬件產品,從而使設計者可以從他

2017-11-24 16:26:40 2715

2715 SelectIO?技術相結合,能夠讓用戶與各種網絡設備進行連接。Virtex-5器件中,以太網MAC 模塊作為一個硬件塊集成在FPGA內部。

2018-07-22 09:28:00 3189

3189

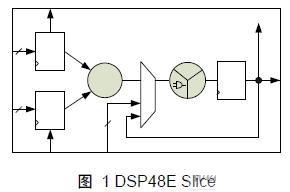

在FPGA系統設計中,要達到性能最大化需要平衡具有混合性能效率的元器件,包括邏輯構造(fabric)、片上存儲器、DSP 和I/O帶寬。在本文中,我將向你解釋怎樣能在追求更高系統級性能的過程中受益于Xilinx? 的Virtex?-5 FPGA構建模塊,特別是新的ExpressFabric?技術。

2018-07-22 09:30:00 2320

2320

隨著FPGA應用范圍的不斷擴大以及對速度需求的不斷提升,集成高速串行模塊的FPGA已經應用于市場。以Xilinx的Virtex5系列為代表的集成GTPRocketIO模塊的FPGA受到廣泛關注。以

2018-07-20 11:42:00 2009

2009

多類指數損失函數逐步添加模型( SAMME)是一種多分類的AdaBoost算法,為進一步提升SAMME算法的性能,針對使用加權概率和偽損失對算法的影響進行研究,在此基礎上提出了一種基于基分類器對樣本

2017-12-01 16:50:47 1

1 AdaBoost是數據挖掘領域最常見的提升算法之一。對傳統AdaBoost將各個基分類器線性相加所存在的不足進行分析,并針對AdaBoost各個弱分類器的加權方式提出新的改進,將傳統的線性相加改為

2018-01-04 16:58:00 0

0 商湯科技算法平臺團隊和北京大學高能效實驗室聯合提出一種基于 FPGA 的快速Winograd算法,可以大幅降低算法復雜度,改善 FPGA 上的 CNN 性能。

2018-02-07 11:52:06 10225

10225

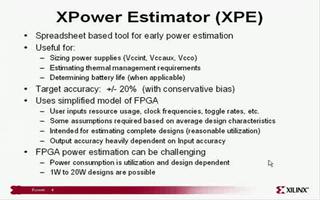

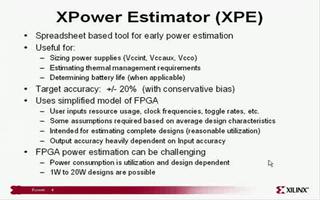

本演示中,我們將介紹利用 XPower 估計器(XPE)工具精確估計 Virtex?-5 器件的功耗所需的步驟。我們還通過在 ML550 開發板 - 進行詳細的功耗測量的首選平臺 - 上進行測量演示了 Virtex?-5 器件的低功耗特性。

2018-06-06 02:45:00 3952

3952

Xilinx 公司Virtex5 系列的FPGA 具有多重配置的特性,允許用戶在不掉電重啟的情況下,根據不同時刻的需求,可以從FLASH 中貯存的多個比特文件選擇加載其中的一個,實現系統功能的變換。

2018-12-04 08:37:00 6255

6255

ICHEC討論了FPGA對HPC應用的適用性,并重點介紹了能夠利用特定FPGA上所有DSP的器件的最佳數據模式。

利用Xilinx Virtex-7 FPGA和Kintex KU115,ICHEC充分利用了re

2018-11-20 06:42:00 3256

3256 在本視頻中,了解Xilinx采用高帶寬存儲器(HBM)和CCIX技術的16nm Virtex UltraScale + FPGA的功能和存儲器帶寬。

2018-11-27 06:20:00 4617

4617 了解如何將復雜的SoC平臺映射到單個Virtex?-7 2000T FPGA

2018-11-23 06:38:00 3189

3189 集成學習的Boosting算法通過結合多個弱學習器組成強學習器,AdaBoost算法是Boosting算法中的一種,本文詳細的總結了AdaBoost算法。

2018-12-29 16:08:08 3496

3496

本文詳細總結了AdaBoost算法的相關理論,本文詳細推導了AdaBoost算法的參數求解過程以及討論了模型的過擬合問題。

2019-01-07 18:26:07 4780

4780

選擇。每個平臺包含不同比例的功能,以滿足各種高級邏輯設計的需要。除了最先進、高性能的邏輯結構外,Virtex-5 FPGas還包含許多硬IP系統級塊,包括功能強大的36kbit塊RAM/FIFOS、第二代

2019-10-21 08:00:00 26

26 Genesys Virtex-5 FPGA開發板集成了功能強大的Xilinx Virtex?-5 FPGA,為廣大用戶帶來了一個功能強大、方便實用的設計平臺。板上還有千兆以太網,高速內存,高分辨率

2019-11-14 17:01:37 5442

5442

和x32的數據帶寬。x1的通道能實現單向312.5 MB/s(2.5 Gb/s)的傳輸速率。Xilinx公司的Virtex5系列FPGA芯片內嵌PCI-ExpressEndpoint Block硬核,為實現單片可配置PCI-Express總線解決方案提供了可能。

2020-01-19 16:52:00 3073

3073

本文檔的主要內容詳細介紹的是FPGA的硬件電路設計教程和FPGA平臺資料簡介包括了:FPGA技術概述;主流FPGA器件介紹;VIRTEX-5 FPGA電路設計;V4LX160 FPGA平臺介紹;

2020-07-06 18:11:22 177

177 上市時間、降低風險、適應不斷演化的標準以及降低系統成本。 Virtex-5平臺建立在這些豐富價值的基礎上,再加上高速串行連接功能和嵌入式處理能力,從而構成了終極系統集成平臺。

2020-07-24 15:25:00 1819

1819

xilinx公司推出的兩種新Virtex-4 FPGA器件LX60和SX35.LX60是邏輯最佳LX平臺的第二個器件,SX35是DSP最佳SX平臺的第一個器件.和今年六月份提供的Virtex-4 LX25一起,Xilinx公司現在可提供三種革命性的FPGA系列.

2020-09-10 08:47:00 2432

2432 鏈路預測是復雜網絡的重要研究方向,當前的鏈路預測算法因可利用的網絡信息有限,導致預測算法的精確度受限為了提高預測算法的性能,采用改進的 Adaboost算法進行鏈路預測。首先根據復雜網絡樣本建立

2021-04-08 11:21:28 15

15 入侵檢測系統在大數據量的情況下誤報率高、泛化能力弱,且單一機器學習算法不能較好地應對多種攻擊類型。為此,設計一個基于支持向量機(SM)與 Adaboost算法的入侵檢測系統。依托 Snort系統

2021-05-25 16:35:43 6

6 針對語音判別系統中單個分類器分類能力有限的問題,提出一種基于 Adaboost算法的回放語音檢測方法。以常量Q倒譜系數和均值超矢量分別作為特征參數和 Adaboost算法的輸人,將多個分類器的檢測

2021-06-03 11:34:57 10

10 基于直流和開關特性的Virtex-5 FPGA產品介紹

2021-07-12 14:11:09 18

18 電子發燒友網站提供《基于Virtex-5FPGA的系統監測器設計.pdf》資料免費下載

2023-10-19 10:49:30 0

0

![]()

電子發燒友App

電子發燒友App

評論