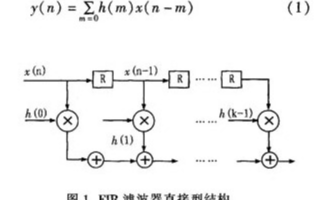

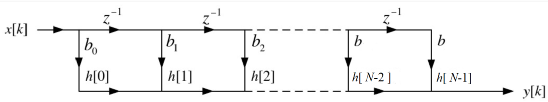

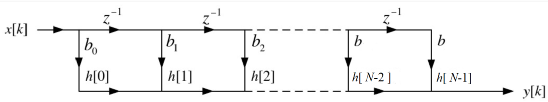

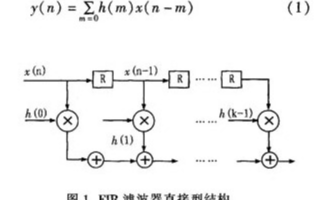

FIR 濾波器廣泛應用于數(shù)字信號處理中,主要功能就是將不感興趣的信號濾除,留下有用信號。##全并行FIR濾波器結構

2014-06-27 10:02:56 10763

10763 流水線是為了提高效率,能并發(fā)同時進行多個任務。

2023-09-05 15:39:56 3344

3344

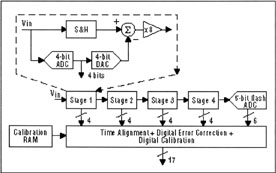

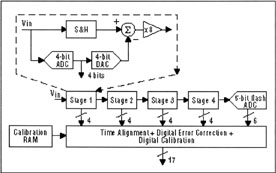

、分辨率、動態(tài)性能和功耗方面有了很大的提高。對于幾Msps到100Msps的8位高速和16位低速模數(shù)轉(zhuǎn)換器(ADC),流水線已經(jīng)成為最流行的模數(shù)轉(zhuǎn)換器結構,它可以涵蓋很廣的應用范圍,包括CCD成像

2023-09-26 10:24:32 2542

2542

,所以經(jīng)濟而效率高。但是這個高效率是以相位的非線性為代價的。選擇性越好,則相位非線性越嚴重。相反,FIR濾波器卻可以得到嚴格的線性相位,然而由于FIR濾波器傳輸函數(shù)的極點固定在原點(輸出只與有限項輸入

2016-08-08 08:49:32

數(shù)字濾波器的類型有FIR(有限長沖擊與IIR(無限長。離散數(shù)字系統(tǒng)中,濾波器的表述為差分方程。FIRFIR基本特性:FIR 濾波器永遠是穩(wěn)定的(系統(tǒng)只有零點);FIR 濾波器的沖激響應是有限長序列

2021-08-17 06:19:17

本文將簡單介紹FIR濾波器的原理,詳細介紹使用Verilog HDL設計并行FIR濾波器的流程和方法。接下來幾篇會介紹串行結構FIR的Verilog設計、使用Quartus和Vivado的IP核

2020-09-25 17:44:38

流水線技術基本原理是什么?設計DSP流水線應注意哪些問題?

2021-04-28 06:10:03

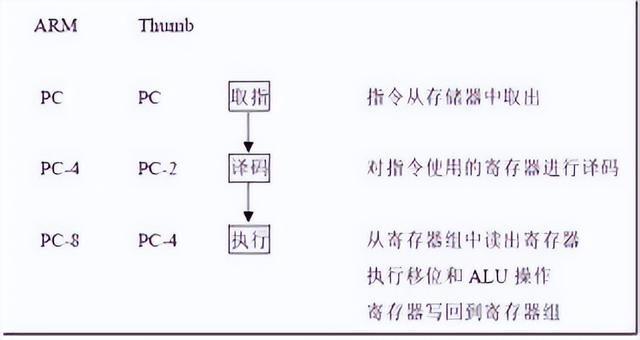

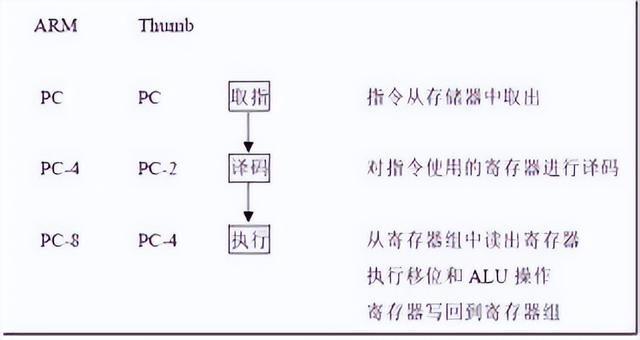

3級流水線(Cortex-M0)

分為以下三個階段:

取指(Fetch):從存儲器中讀取指令。

解碼(Decode):解析指令的操作類型和操作數(shù)。

執(zhí)行(Execute):執(zhí)行指令(如算術運算、內(nèi)存

2025-11-21 07:35:31

圖中的DFG(Data Flow Graph)節(jié)點已經(jīng)標出了傳輸延遲,求該電路中流水線寄存器的最佳放置位置?求問大神解答這個題

2021-11-20 11:02:57

看到匯編中很多關于程序返回與中斷返回時處理地址都很特別,仔細想想原來是流水線作用的效果。所以,決定總結學習下ARM流水線。ARM7處理器采用3級流水線來增加處理器指令流的速度,能提供0.9MIPS

2021-07-16 06:53:06

ARM 系列的流水線設計都不同。流水線是一種設計技術或過程,它在提高計算機和微控制器處理器中的數(shù)據(jù)處理效率方面發(fā)揮著重要作用。通過將處理器保持在一個連續(xù)的獲取、解碼和執(zhí)行過程中,稱為

2022-04-11 17:23:19

令預取、 譯碼、 執(zhí)行、 寫回結果, openrisc采用的是 5 級整數(shù)流水線。當然它們的核心思想都是利用并行執(zhí)行提高效率。總結一下,流水線就是插入寄存器,以面積換取速度。`

2020-10-26 14:38:12

有的單核RISC-V MCU支持四級流水線,有的只支持三級流水線,是不是級數(shù)越多,帶來的開銷越大,功耗也越高呢?

2024-05-20 16:01:17

FIR濾波器如何定義?為什么要使用FIR濾波器?

2021-04-06 07:48:45

如何理解fpga流水線

2015-08-15 11:43:23

前段時間發(fā)了個關于fpga的PID實現(xiàn)的帖子,有個人說“整個算法過程說直白點就是公式的硬件實現(xiàn),用到了altera提供的IP核,整個的設計要注意的時鐘的選取,流水線的應用”,本人水平有限,想請教一下其中時鐘的選取和流水線的設計應該怎么去做,需要注意些什么,請大家指導一下。

2015-01-11 10:56:59

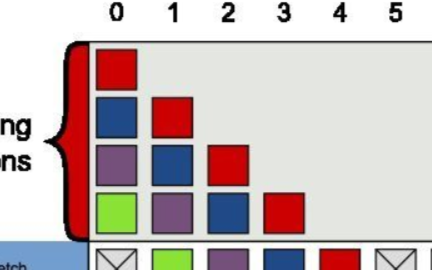

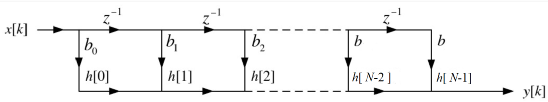

本文首先介紹了FIR濾波器和脈動陣列的原理,然后設計了脈動陣列結構的FIR濾波器,畫出電路的結構框圖,并進行了時序分析,最后在FPGA上進行驗證。結果表明,脈動陣列的模塊化和高度流水線的結構使FIR

2021-04-20 07:23:59

流水線模數(shù)轉(zhuǎn)換器(ADC)有哪些優(yōu)點?流水線ADC中常用的運算放大器有哪些?流水線ADC的放大器結構及工作原理是什么?

2021-04-22 06:18:28

設計實現(xiàn)低通FIR濾波器一步設計和實現(xiàn)過濾器獲得濾波器系數(shù)可調(diào)諧低通FIR濾波器高級設計選項:最佳非等效低通濾波器Equiripple設計增加阻帶衰減最小相位低通濾波器設計使用多級技術的最小

2018-08-23 10:00:16

實現(xiàn)FPGA數(shù)字下變頻的多類濾波器分組級聯(lián)技術分析1 引 言 本文針對以下高效算法做了總結,進行合理的分組級聯(lián)并引入流水線技術以便于在FPGA上實現(xiàn)。數(shù)字下變頻(DDC)就是通過混頻、抽取和濾波等

2009-10-23 10:26:53

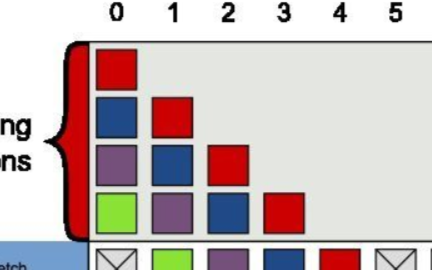

并行流水結構FIR的原理是什么基于并行流水線結構的可重配FIR濾波器的FPGA實現(xiàn)

2021-04-29 06:30:54

相對無限沖擊響應(IIR)濾波器,有限沖擊響應(FIR)能夠在滿足濾波器幅頻響應的同時獲得嚴格的線性相位特性,而數(shù)據(jù)通信、語音信號處理等領域往往要求信號在傳輸過程中不能有明顯的相位失真,所以FIR

2019-08-23 06:39:46

相對無限沖擊響應(IIR)濾波器,有限沖擊響應(FIR)能夠在滿足濾波器幅頻響應的同時獲得嚴格的線性相位特性,而數(shù)據(jù)通信、語音信號處理等領域往往要求信號在傳輸過程中不能有明顯的相位失真,所以FIR

2019-08-27 07:16:54

: 2.1 FIR數(shù)字濾波器與流水線結構 現(xiàn)代微處理器、數(shù)字信號處理器、高速數(shù)字系統(tǒng)設計中都廣泛應用了流水線(Pipelining)技術,其核心設計思想是把一個周期內(nèi)執(zhí)行的邏輯操作分成幾步較小的操作,在

2011-02-24 14:20:18

作Stretch計算機)。后來的CDC 6600同時采用了流水線和多功能部件。到了20世紀80年代,流水線技術成為RISC處理器設計方法中最基本的技術之一。RISC設計方法的大部分技術都直接或者間接以提高流水線

2023-03-01 17:52:21

在ARM中,關于 LDR流水線,分支流水線,中斷流水線,其和 PC 之間的關系一直沒整明白,求大神詳解!!!

2019-04-30 07:45:25

針對并行爬蟲系統(tǒng)在多任務并發(fā)執(zhí)行時所遇到的模塊間負載平衡問題,提出流水線負載平衡模型(PLB),將不同的任務抽象為獨立模塊而達到各模塊的處理速度相等,采用多線程的方式

2009-03-31 10:19:30 19

19 流水線結構的高效SAR快視成像處理器

2009-05-08 17:16:47 23

23 并行FIR濾波器具有速度快、容易設計的特點,但是要占用大量的資源。在多階數(shù)的亞高頻系統(tǒng)設計中,使用并

2009-07-21 16:55:06 0

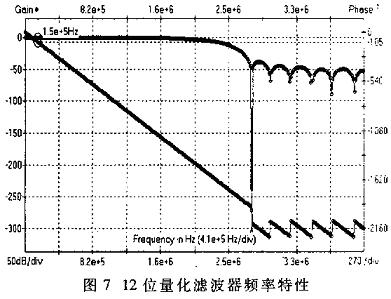

0 本文綜合介紹了基于FPGA 軟件Quartus II 和MATLAB 的FIR 濾波器的設計仿真,將兩大軟件綜合運用后大大縮減了設計研發(fā)的時間,在算法結構上利用了流水線等優(yōu)化方式。

2009-11-30 14:21:09 117

117 使用軟件仿真硬件流水線是很耗時又復雜的工作,仿真過程中由于流水線的沖突而導致運行速度緩慢。本文通過對嵌入式處理器的流水線, 指令集, 設備控制器等內(nèi)部結構的分析和

2009-12-31 11:30:21 9

9 FPGA重要設計思想及工程應用之流水線設

流水線設計是高速電路設計中的一 個常用設計手段。如果某個設計的處理流程分為若干步驟,而且整個數(shù)據(jù)處理 流程分

2010-02-09 11:02:20 52

52 什么是fir數(shù)字濾波器

Part 1: Basics1.1 什么是FIR濾波器?FIR 濾波器是在數(shù)字信號處理(DSP)中經(jīng)常使用的兩種

2008-01-16 09:42:22 17577

17577 FIR并行濾波器設計

數(shù)字濾波器可以濾除多余的噪聲,擴展信號頻帶,完成信號預調(diào),改變信號的特定頻譜分量,從而得到預期的結果。數(shù)字濾波器在DVB、

2008-01-16 09:47:09 1669

1669

高效FIR濾波器的設計與仿真-基于FPGA

摘要:該文在介紹有限沖激響應(FIR)數(shù)字濾波器理論及常見實現(xiàn)方法的基礎上,提出了一種基于FPGA的高效實現(xiàn)方案。

2008-01-16 09:56:02 2060

2060

流水線ADC

低采樣速率ADC仍然采用逐次逼近(SAR)、積分型結構以及最近推出的過采樣ΣΔADC,而高采樣速率(幾百MSPS以上)大多用閃速ADC及其各種變型電路。然而

2009-02-08 11:02:50 10420

10420

摘要: 提出了一種采用現(xiàn)場可編碼門陣列器件(FPGA)并利用窗函數(shù)法實現(xiàn)線性FIR數(shù)字濾波器的設計方案,并以一個十六階低通FIR數(shù)字濾波器電路的實現(xiàn)

2009-06-20 14:05:46 1679

1679

什么是流水線技術

流水線技術

2010-02-04 10:21:39 4305

4305 流水線操作,應用處理器,應用處理器的結構和原理是什么?

與哈佛結構相關,DSP芯片廣泛采用流水線以減少指令執(zhí)行時間.從而增強

2010-03-26 15:03:48 1380

1380 流水線中的相關培訓教程[1]

學習目標

理解流水線中相關的分類及定義;

2010-04-13 15:56:08 1244

1244 流水線中的相關培訓教程[3]

(1) 寫后讀相關(RAW:Read After Write) (命名規(guī)則) :j 的執(zhí)行要用到 i 的計算結果,當它們在流水線中重疊執(zhí)行時,j 可

2010-04-13 16:02:57 1025

1025 流水線中的相關培訓教程[4]

下面討論如何利用編譯器技術來減少這種必須的暫停,然后論述如何在流水線中實現(xiàn)數(shù)據(jù)相關檢測和定向。

2010-04-13 16:09:15 5088

5088 基于流水線技術,利用FPGA進行并行可重復配置高精度的 FIR濾波器 設計。使用VHDL可以很方便地改變濾波器的系數(shù)和階數(shù)。在DSP中采用這種FIR濾波器的設計方法可以充分發(fā)揮FPGA的優(yōu)勢。

2011-07-18 17:09:28 63

63 本文計論了高階FIR型正交鏡像濾波器的設計問題。根據(jù)FIR 正交鏡像濾波器 設計的基本原理,將高階正交鏡像濾波器的設計問題轉(zhuǎn)換為單變量的優(yōu)化設計問題。利用一雛尋優(yōu)的算法,可

2011-08-29 16:16:25 29

29 cpu流水線技術是一種將指令分解為多步,并讓不同指令的各步操作重疊,從而實現(xiàn)幾條指令并行處理,以加速程序運行過程的技術。

2011-12-14 15:29:24 5114

5114 行為級仿真是提高流水線(Pipeline)ADC設計效率的重要手段。建立精確的行為級模型是進行行為級仿真的關鍵。本文采用基于電路宏模型技術的運算放大器模型,構建了流水線ADC的行為

2012-04-05 15:37:55 21

21 fir濾波器的有關資料 fir_濾波器sourc.rar

2015-12-14 14:12:56 25

25 電鍍流水線的PLC控制電鍍流水線的PLC控制電鍍流水線的PLC控制

2016-02-17 17:13:04 37

37 基于MATLAB的FIR濾波器設計與濾波。

2016-12-14 22:08:25 68

68 裝配流水線控制系統(tǒng)設計

2016-12-17 15:26:59 14

14 基于位并行DA結構的高速FIR濾波器_周云

2017-01-07 21:39:44 4

4 數(shù)字濾波器廣泛應用于硬件電路設計,一般分為FIR濾波器和IIR濾波器。那么FIR濾波器和IIR濾波器有什么區(qū)別呢?本文通過幾個例子做一個簡單的總結。

2017-05-03 11:36:31 20

20 流水線狀態(tài)機20進制,101序列檢測,8位加法器流水線的程序

2017-05-24 14:40:47 0

0 在航空微電子中心的某預研項目中,需要開發(fā)設計某32位浮點通用數(shù)字信號處理器(DSP)。本系統(tǒng)控制通路部分的設計采用超級哈佛及五級流水線結構。本文分析了該流水線的設計過程,并對遇到的數(shù)據(jù)相關問題提出

2017-10-23 10:35:35 0

0 摘要:有限沖擊響應(FIR)濾波器是數(shù)字通信系統(tǒng)中常用的基本模塊。文章設計了一種流水結構的FIR濾波器,通過FPGA對其進行硬什加速控制。仿真結果驗證了所設計的FIR流水結構濾波器功能的正確性

2017-11-18 06:15:02 2101

2101

線性相位FIR濾波器的對稱性減小了硬件規(guī)模;利用分割查找表的方法減小了存儲空間;采用并行分布式算法結構和流水線技術提高了濾波器的速度,在FPGA上實現(xiàn)了該濾波器。

2017-11-24 15:17:27 3615

3615 如果一個FIR濾波器的脈沖響應函數(shù)具有對稱性或反對稱性,則其相位響應是頻率的線性函數(shù)r或附加一個固定的初始相位),這樣的濾波器稱為線性相位FIR濾波器。由于系數(shù)的對稱性,實現(xiàn)線性相位FIR濾波器所需

2017-12-21 14:24:51 5

5 本文針對快速、準確選擇參數(shù)符合項目要求的濾波器設計方法的目的,通過系統(tǒng)的介紹有限脈沖響應( Finite Impulse Response,FIR)濾波器的原理、結構形式以及幾種FIR濾波器設計方法

2017-12-21 14:53:14 14

14 本文將討論處理器的一個重要的基礎知識:流水線。熟悉計算機體系結構的讀者一定知道,言及處理器微架構,幾乎必談其流水線。處理器的流水線結構是處理器微架構最基本的一個要素,猶如汽車底盤對于汽車一般具有基石性的作用,它承載并決定了處理器其他微架構的細節(jié)。

2018-04-08 08:16:00 23563

23563

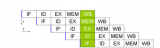

顏色表示了不同階段的可配置性或可編程性:綠色表示該流水線階段是完全可編程控制的,黃色表示該流水線階段可以配置但不是可編程的,藍色表示該流水線階段是由GPU固定實現(xiàn)的,開發(fā)者沒有任何控制權。實線表示該shader必須由開發(fā)者編程實現(xiàn),虛線表示該Shader是可選的.

2018-05-04 09:16:00 4111

4111

第一部分什么是流水線 第二部分什么時候用流水線設計 第三部分使用流水線的優(yōu)缺點 第四部分流水線加法器舉例 一. 什么是流水線 流水線設計就是將組合邏輯系統(tǒng)地分割,并在各個部分(分級)之間插入寄存器

2018-09-25 17:12:02 7694

7694 流水線的平面設計應當保證零件的運輸路線最短,生產(chǎn)工人操作方便,輔助服務部門工作便利,最有效地利用生產(chǎn)面積,并考慮流水線安裝之間的相互銜接。為滿足這些要求,在流水線平面布置時應考慮流水線的形式、流水線安裝工作地的排列方法等問題。

2019-11-28 07:07:00 2868

2868 流水線在工業(yè)生產(chǎn)中扮演著重要的角色,優(yōu)化流水線直接關系著產(chǎn)品的質(zhì)量和生產(chǎn)的效率,因此成為企業(yè)不得不關注的話題。

2019-11-28 07:05:00 2701

2701 流水線又稱為裝配線,一種工業(yè)上的生產(chǎn)方式,指每一個生產(chǎn)單位只專注處理某一個片段的工作。以提高工作效率及產(chǎn)量;按照流水線的輸送方式大體可以分為:皮帶流水裝配線、板鏈線、倍速鏈、插件線、網(wǎng)帶線、懸掛線及滾筒流水線這七類流水線。

2019-11-28 07:04:00 4174

4174 必要在性能和實現(xiàn)復雜性之間做出選擇,也就是選擇不同的濾波器實現(xiàn)結構。這里運用并行流水線結構來實現(xiàn)速度和硬件面積之間的互換和折衷。

2020-03-04 09:22:01 5857

5857

一、背景 自20世紀初美國人亨利路福特首次采用流水線的生產(chǎn)方法至今,流水線的發(fā)展已經(jīng)歷了百年。 由于流水線作業(yè)的高效,穩(wěn)定等優(yōu)勢,不斷被應用于各類生產(chǎn)型企業(yè)。這個過程中不斷衍生優(yōu)化,逐漸形成了單一產(chǎn)品流水線

2020-11-02 13:55:21 1765

1765 倍,其中L為并行的路數(shù),并且運算延遲小。首先從理論上分析了基于多相濾波器的并行濾波原理,并以八路并行為例,對FIR濾波運算做了浮點仿真驗證。然后用經(jīng)典符號數(shù)表示以及優(yōu)化定點濾波器系數(shù),并針對濾波器系數(shù)設計了流水線結構。最后在Ahera的Stratix II系列芯片上

2021-01-28 17:22:00 15

15 倍,其中L為并行的路數(shù),并且運算延遲小。首先從理論上分析了基于多相濾波器的并行濾波原理,并以八路并行為例,對FIR濾波運算做了浮點仿真驗證。然后用經(jīng)典符號數(shù)表示以及優(yōu)化定點濾波器系數(shù),并針對濾波器系數(shù)設計了流水線結構。最后在Ahera的Stratix II系列芯片上

2021-01-28 17:22:00 7

7 EE-383:基于MDMA的雙SHARC+并行流水線音頻直通

2021-04-29 17:30:34 0

0 所謂流水線處理,如同生產(chǎn)裝配線一樣,將操作執(zhí)行工作量分成若干個時間上均衡的操作段,從流水線的起點連續(xù)地輸入,流水線的各操作段以重疊方式執(zhí)行。這使得操作執(zhí)行速度只與流水線輸入的速度有關,而與處理所需

2021-05-27 16:57:52 3133

3133 按照流水線的輸送方式大體可以分為:皮帶流水裝配線、板鏈線、倍速鏈、插件線、網(wǎng)帶線、懸掛線及滾筒流水線這七類流水線。

2021-07-05 11:12:18 9128

9128

在工程建造中,滾筒流水線演著重要的角色。在一些工程建造過程中,經(jīng)常看到滾筒流水線的身影。在工業(yè)不斷發(fā)展下的今天,滾筒流水線日益增長,走向多元化。滾筒流水線能夠長距離的輸送,而且支持重量大的貨物。

2021-07-08 09:32:56 2268

2268 LED生產(chǎn)流水線輸送形式分為平面直線傳輸流水線、各種角度平面轉(zhuǎn)彎傳輸流水線、斜面上傳流水線、斜面下傳流水線這四種輸送方式,企業(yè)也是可以根據(jù)LED燈具生產(chǎn)狀況選擇合適自己的LED生產(chǎn)流水線輸送方式。選擇LED生產(chǎn)流水線時應了解流水線各部分組成及功用。

2021-08-06 11:53:51 1354

1354 流水線一、定義流水線是指在程序執(zhí)行時多條指令重疊進行操作的一種準并行處理實現(xiàn)技術。各種部件同時處理是針對不同指令而言的,他們可同時為多條指令的不同部分進行工作。? 把一個重復的過程分解為若干個子過程

2021-10-20 20:51:14 6

6 本文解釋了流水線及其對 FPGA 的影響,即延遲、吞吐量、工作頻率的變化和資源利用率。

2022-05-07 16:51:10 7417

7417

1989 年推出的 i486 處理器引入了五級流水線。這時,在 CPU 中不再僅運行一條指令,每一級流水線在同一時刻都運行著不同的指令。這個設計使得 i486 比同頻率的 386 處理器性能提升了不止一倍。

2022-09-22 10:04:23 2911

2911 為什么有些CPU的主頻更低,但運算效率卻更高呢? 比如:51單片機30M主頻,STM32單片機20M主頻,執(zhí)行相同一段代碼可能主頻更低的STM32所花的時間更短。 這里就牽涉到CPU流水線的問題,本文圍繞CPU流水線描述相關內(nèi)容。

2022-10-24 14:34:48 5619

5619 1.根據(jù)沖激響應的不同,將數(shù)字濾波器分為有限沖激響應(FIR)濾波器和無限沖激響應(IIR)濾波器。對于FIR濾波器,沖激響應在有限時間內(nèi)衰減為零,其輸出僅取決于當前和過去的輸入信號值。對于IIR

2022-12-30 23:45:05 5174

5174 stage:和聲明式的含義一致,定義流水線的階段。Stage 塊在腳本化流水線語法中是可選的,然而在腳本化流水線中實現(xiàn) stage 塊,可以清楚地在 Jenkins UI 界面中顯示每個 stage 的任務子集。

2023-01-13 15:34:18 1587

1587 流水線型ADC是采樣速率從幾Msps到100Msps+的首選架構。設計復雜性僅隨位數(shù)線性(非指數(shù))增加,因此同時為轉(zhuǎn)換器提供高速、高分辨率和低功耗。流水線ADC在廣泛的應用中非常有用,尤其是在數(shù)

2023-02-25 09:28:18 6909

6909

上堂課講到FIR濾波器的線性相位特點,分析了線性相位帶來的延時特性。本堂課繼續(xù)講解FIR濾波器的幅度特性,再理論聯(lián)系實際的看看FIR濾波器到底長什么樣?

2023-03-14 17:45:33 6440

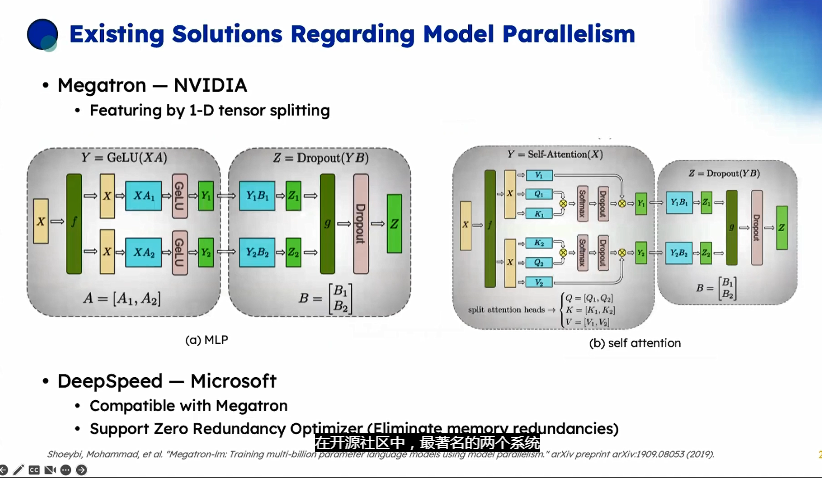

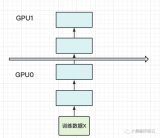

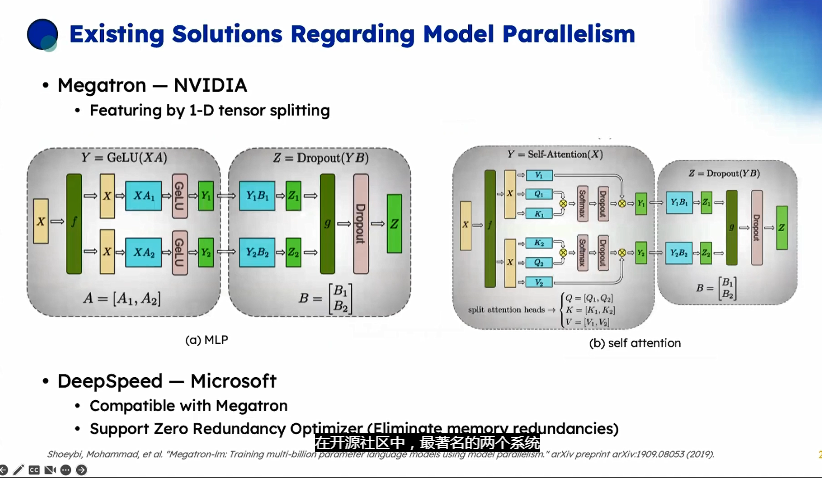

6440 張星并行和流水線并行技術通常被描述為模型并行,在開源社區(qū)中,最著名的兩個系統(tǒng)是NVIDIA的Megatron- M和Microsoft的DeepSpeed。

2023-03-23 17:21:29 2523

2523

FIR(Finite Impulse Response)濾波器是一種有限長單位沖激響應濾波器,又稱為非遞歸型濾波器。FIR 濾波器具有嚴格的線性相頻特性,同時其單位響應是有限長的,因而是穩(wěn)定的系統(tǒng),在數(shù)字通信、圖像處理等領域都有著廣泛的應用。

2023-03-27 11:33:53 1596

1596

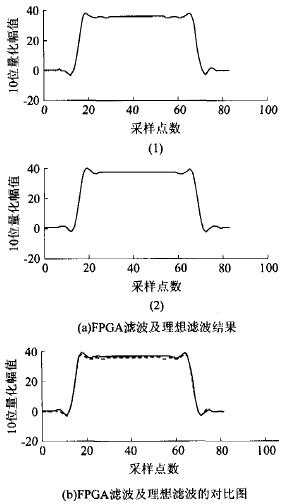

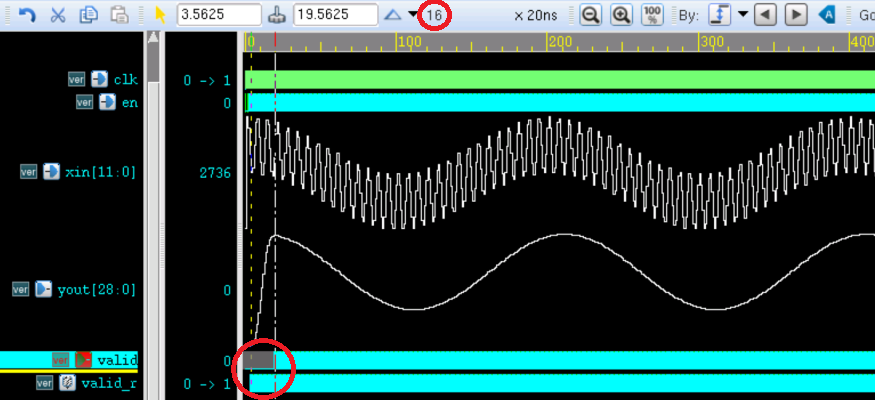

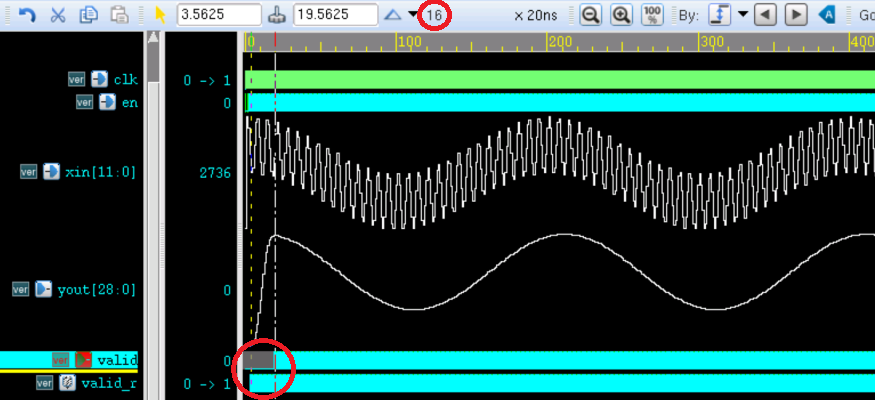

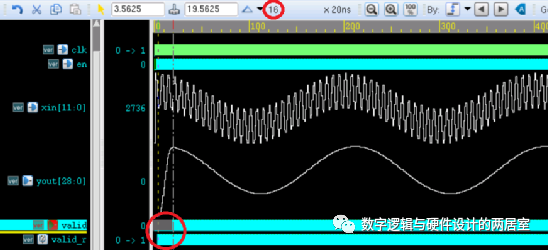

設計參數(shù)不變,與并行 FIR 濾波器參數(shù)一致。即,輸入頻率為 7.5 MHz 和 250 KHz 的正弦波混合信號,經(jīng)過 FIR 濾波器后,高頻信號 7.5MHz 被濾除,只保留 250KMHz 的信號。

2023-03-27 11:36:46 1544

1544

jenkins 有 2 種流水線分為聲明式流水線與腳本化流水線,腳本化流水線是 jenkins 舊版本使用的流水線腳本,新版本 Jenkins 推薦使用聲明式流水線。文檔只介紹聲明流水線。

2023-05-17 16:57:31 1552

1552 本文介紹了設計濾波器的FPGA實現(xiàn)步驟,并結合杜勇老師的書籍中的并行FIR濾波器部分進行一步步實現(xiàn)硬件設計,對書中的架構做了復現(xiàn)以及解讀,并進行了仿真驗證。

2023-05-24 10:57:36 1825

1825

和充沛優(yōu)質(zhì)的硬件資源 算法的迭代創(chuàng)新 在大模型訓練這個系列里,我們將一起探索學習幾種經(jīng)典的分布式并行范式,包括 流水線并行(Pipeline Parallelism),數(shù)據(jù)并行(Data

2023-05-25 11:41:21 1914

1914

點擊上方 藍字 關注我們 本文將回顧對稱 F IR ? 濾波器 的高效 FPGA 實現(xiàn)的注意事項。 本文將推導對稱 FIR 濾波器的模塊化流水線結構。我們將看到派生結構可以使用? Xilinx

2023-05-26 01:20:02 1633

1633

但在實際應用中,流水線并行并不特別流行,主要原因是模型能否均勻切割,影響了整體計算效率,這就需要算法工程師做手調(diào)。因此,今天我們來介紹一種應用最廣泛,最易于理解的并行范式:數(shù)據(jù)并行。

2023-05-26 14:40:20 1920

1920

設計參數(shù)不變,與并行 FIR 濾波器參數(shù)一致。即,輸入頻率為 7.5 MHz 和 250 KHz 的正弦波混合信號,經(jīng)過 FIR 濾波器后,高頻信號 7.5MHz 被濾除,只保留 250KMHz 的信號。

2023-06-01 11:08:38 1520

1520

FIR(Finite Impulse Response)濾波器是一種有限長單位沖激響應濾波器,又稱為非遞歸型濾波器。

2023-06-01 11:11:34 1842

1842

數(shù)字濾波器是數(shù)字信號處理中最常用的一種技術,可以對數(shù)字信號進行濾波、降噪、增強等處理,其中最常見的兩種數(shù)字濾波器是IIR濾波器和FIR濾波器。本文將從IIR濾波器和FIR濾波器的原理、特點和應用等方面進行詳細介紹,以便更好地理解兩種濾波器的區(qū)別。

2023-06-03 10:21:43 20531

20531 stage:和聲明式的含義一致,定義流水線的階段。Stage 塊在腳本化流水線語法中是可選的,然而在腳本化流水線中實現(xiàn) stage 塊,可以清楚地在 Jenkins UI 界面中顯示每個 stage 的任務子集。

2023-07-20 16:43:16 1209

1209 新大陸固定式掃碼器作為一種高效的條碼掃描設備,廣泛應用于各個行業(yè)中,尤其是在SMT(表面貼裝技術)流水線中有重要的作用。以下是新大陸固定式掃碼器在SMT流水線中的具體使用情況。提高生產(chǎn)效率和質(zhì)量

2024-07-03 10:18:03 1399

1399

在汽車制造領域,生產(chǎn)流水線的高效、穩(wěn)定運行是保障產(chǎn)品質(zhì)量與生產(chǎn)效率的關鍵。隨著工業(yè) 4.0 和智能制造理念的深入,汽車生產(chǎn)企業(yè)對流水線自動化控制提出了更高要求,不僅要實現(xiàn)設備間的精準協(xié)同作業(yè),還需

2025-06-11 15:26:49 577

577

電子發(fā)燒友App

電子發(fā)燒友App

評論