由于FPGA技術和ARM技術應用越來越廣泛,通過設計并行總線接口來實現兩者之間的數據交換,可以較容易地解決快速傳輸數據的需求,因此設計滿足系統要求的FPGA并行總線顯得尤為重要。本文設計的FPGA的ARM外部并行總線接口,滿足了總線的時序要求,并在某航空機載雷達應答機中進行了應用.

2013-08-15 10:44:19 9149

9149

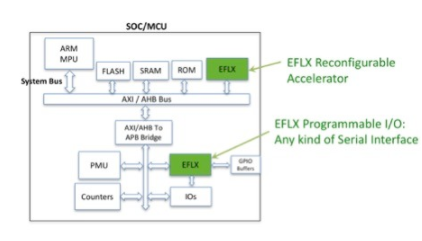

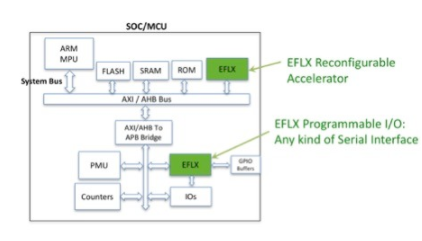

FPGA+ARM是ZYNQ的特點,那么PL部分怎么和ARM通信呢,依靠的就是AXI總線。這個實驗是創(chuàng)建一個基于AXI總線的GPIO IP,利用PL的資源來擴充GPIO資源。通過這個實驗迅速入門

2020-12-25 14:07:02 6725

6725

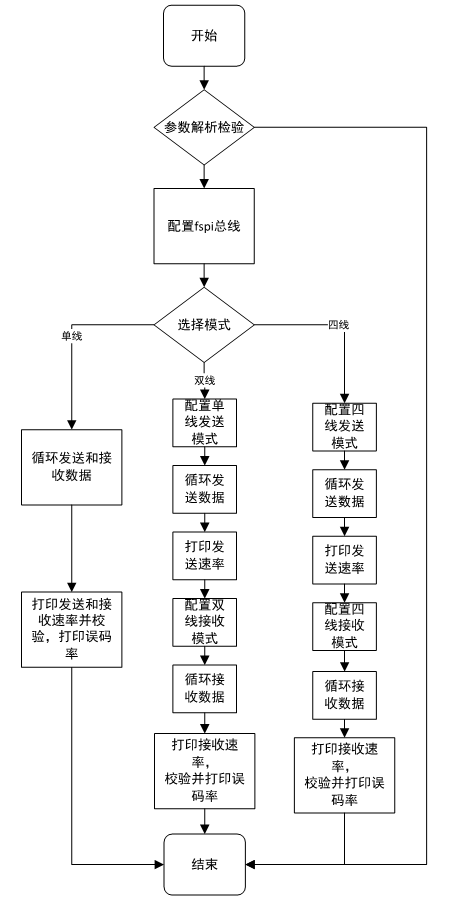

隨著現代處理解決方案對靈活性和性能的需求日益增長,eFPGA 可以使用少量高速邏輯輕松連接到任何類型和寬度的 ARM 總線。

2022-06-09 10:52:46 4677

4677

作為一名PCB設計工程師,具備一些高速方面的知識是非常有必要的,甚至說是必須的。就信號來說,高速信號通常見于各種并行總線與串行總線,只有知道了什么是總線,才能知道它跑多快,才能開始進行布線。

2022-12-29 14:23:12 2707

2707

的處理器平臺來實現例如多路 / 高速 AD 采集、多路網口、多路串口、多路 / 高速并行 DI/DO、高速數據并行處理等特定功能,因此 ARM + FPGA 架構處理器平臺愈發(fā)受市場歡迎。 ARM + FPGA 架構能帶來性能、成本、功耗等綜合比較優(yōu)勢,ARM 與 FPGA 既可各司其職,各自發(fā)揮原本架構

2024-01-29 15:13:43 3517

3517

ADC和DAC是FPGA與外部信號的接口,從數據接口類型的角度劃分,有低速的串行接口和高速的并行接口。

2024-02-22 16:15:03 5869

5869

1、Cortex-M0、端口與總線介紹與配置在ARM DesignStart網址下載的Cortex-M0 DesignStart Eval文件資源中找到名為“cortexm0ds_logic.v

2022-08-08 16:30:08

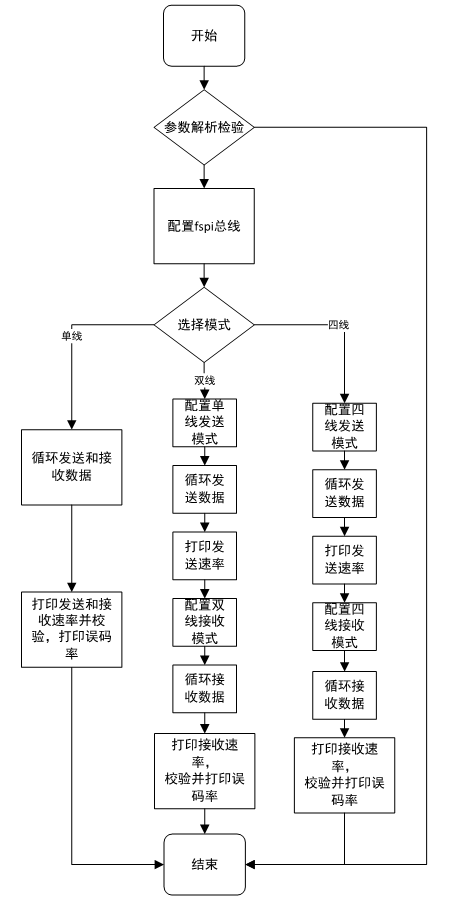

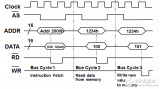

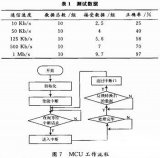

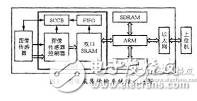

)結合使用完成多通道檢控任務的一種實現方法。 各部分功能簡介 圖1為此系統的結構連接框圖。如圖所示,ARM芯片與FPGA芯片之間通過數據總線、地址總線及讀寫控制線相連,而與終端PC則通過串口通信

2008-06-17 12:00:27

·諾依曼結構。所謂哈佛結構就是將數據與指令分開存儲,獨立編址,可以提高數據調用的效率,TI的DSP也是用這個結構;與之對應的是馮·諾依曼結構,數據與指令共同編址,節(jié)省一條總線ARM(Advanced

2021-09-08 17:49:20

FPGA筆記1-ARM單片機和FPGA有什么區(qū)別–ARMFPGA總線結構哈佛總線或馮諾依曼結構查找表執(zhí)行方式串行執(zhí)行并行執(zhí)行運行層面軟件硬件所用語言C或匯編Verilog HDL/VHDL概念上

2021-07-16 06:54:03

支持GNET、USB固件升級(ARM/FPGA/DSP固件)尺寸87×62×5MM搭配接插件型號FX10A-168P-SV(X1)+FX10A-96P-SV(X2)工作溫度-45至85℃存儲溫度-45至

2017-07-18 10:28:53

V soc以及 Xilinx 的 zynq 7000平臺 將 ARM+FPGA 構建到 一個芯片上,串行計算能力和并行的完美結合。感覺還是有點厲害的。本人小白,,希望大家一起來討論下,FPGA+ARM 這個神奇的東東。。。

2015-08-05 13:48:27

用于:1.與ARM子系統通信2.與DSP子系統通信3.兩個FPGA子系統通信4.兩個96pin擴展插槽,用于擴展外設板卡5.8個26pin的擴展與測試排針,主要用于并行檢測與測試主要應用領域

2010-12-25 15:47:19

FPGA與ARM、DSP的區(qū)別在嵌入式開發(fā)領域,ARM是一款非常受歡迎的微處理器,其市場覆蓋率極高,DSP和FPGA則是作為嵌入式開發(fā)的協處理器,協助微處理器更好的實現產品功能。那三者的技術特點以及

2014-06-26 14:23:43

在嵌入式開發(fā)領域,ARM是一款非常受歡迎的微處理器,其市場覆蓋率極高,DSP和FPGA則是作為嵌入式開發(fā)的協處理器,協助微處理器更好的實現產品功能。那三者的技術特點以及區(qū)別是什么呢?下文就此問題略

2013-05-06 15:56:02

的微處理器,其設計理念是盡量簡化指令集,以提高指令執(zhí)行效率,從而獲得更高的運行速度和更低的功耗。ARM處理器具有低成本、低功耗和高可靠性等特點。

其次,從功能和應用角度來看,FPGA適合用于需要高速并行

2024-04-28 09:00:54

的微處理器,其設計理念是盡量簡化指令集,以提高指令執(zhí)行效率,從而獲得更高的運行速度和更低的功耗。ARM處理器具有低成本、低功耗和高可靠性等特點。

其次,從功能和應用角度來看,FPGA適合用于需要高速并行

2024-04-28 08:56:35

FPGA與ARM進行并行通信,這個接口應該如何設置?是否要考慮異步時鐘域的問題?

2014-11-20 10:50:37

FPGA 中模擬 I2C 接口已成為 FPGA 開發(fā)必要的步驟。I2C 協議作為一個串行總線標準盡管沒有并行總線的數據吞吐能力,但是它的以下特點使其有著廣泛的應用:? 只需要兩條總線—串行數據線 SDA

2018-09-29 09:37:11

輸出。這兩個芯片的管腳雖然很多,但大多數都是與硬件設計有關。其實幾乎所有的并行ADC和并行DAC與FPGA之間的接口只有一條時鐘線與一組數據總線,數據總線的位寬即為ADC/DAC的位數。每個時鐘周期

2020-09-27 09:40:08

fpga的硬件換成我們自己的arm設備。不過經過研究這種設想不可行。個人看法,也許不對哦。!!!!arm是一款多核心,單進程處理器,目前為止arm處理器都不支持多線程。所以多線程概念不能將并行計算優(yōu)化

2015-12-30 14:33:38

`fpga基礎篇(二):三大并行結構最近小編比較忙,所以這期給大家介紹一個基礎篇,比較簡單,但卻是FPGA編程的基礎。我們知道FPGA與單片機最大的區(qū)別就是FPGA是并行執(zhí)行的,而單片機是串行的,說

2017-04-13 10:23:27

AD1847串行端口音頻編解碼器如何與并行總線接口的實例

2009-05-13 09:57:27

嗨,我在我的PC上安裝了PCI并行端口卡以提供LPT2。我想運行XILINX并讓它檢測卡,以便我可以使用XILINX Parallel Cable IV來處理它。 XILINX檢測到該卡但發(fā)出

2019-05-22 09:27:37

數據,驗證、停止,并用其他的輸入端口控制讀寫操作,充分利用片上系統的優(yōu)良功能 ,使FPGA能夠作為主機與外部含IIC總線設備互相通信。

2012-05-16 16:08:36

增強型并行端口EPP的主要特點是:提供了一個并行端口雙向溝通,即一種方法來讀取和寫入外圍設備連接到您的PC的并行端口。交易是8位寬和原子。主機(PC)始終是交易的始作俑者,讀取或寫入。有沒有突發(fā)

2012-03-22 16:56:03

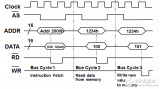

等串行總線接口只能實現FPGA 和ARM 之間的低速通信 ;當傳輸的數據量較大.要求高速傳輸時,就需要用并行總線來進行兩者之間的高速數據傳輸.

2019-09-17 06:21:10

能源電力、工業(yè)控制、智慧醫(yī)療等行業(yè),往往更需要ARM + FPGA架構的處理器平臺來實現例如多路/高速AD采集、多路網口、多路串口、多路/高速并行DI/DO、高速數據并行處理等特定功能,因此ARM

2024-07-17 10:50:32

國外的融合技術專家展示了一項基于FPGA的數據采集系統,用于合成孔徑成像技術。采用了Xilinx ISE設計軟件,支持ARM AMBA AXI4接口。文風犀利,觀點新穎,FPGA中使用ARM及AMBA總線中不可多得的資料在賽靈思FPGA中使用ARM及AMBA總線[hide][/hide]

2012-03-01 15:48:17

ARM跟FPGA通信,要采用8位地址總線、8位數據總線、讀寫控制線,怎么實現,地址總線是要映射到FPGA的內部還是直接ARM的內存空間?最好有ARM端簡單的C程序描述下,謝謝。

2022-11-22 14:58:26

PCI9656,通過CPCI 總線經J1和J2口傳輸到雷達系統的其他功能模塊。對于并行信號而言,32位帶寬的信號首先通過J3口發(fā)送到F-PGA內部寄存器中FPGA接收到數據后 將數據寫入輸入緩存區(qū),并在完成一幀

2019-05-21 05:00:19

如何實現單片機與PCI總線接口的并行通信?

2021-04-29 07:14:26

我想解碼一個以50 MHz時鐘速度運行的8位并行總線。我想使用FPGA開發(fā)板實現這一目標,但我不知道要獲得哪一個。我還需要在計算機屏幕上顯示解碼信息有人能給我一些適合我需要的可用FPGA開發(fā)板的信息嗎?板越便宜越好。如果需要更多信息,請告訴我。謝謝大衛(wèi)。

2019-09-05 10:00:38

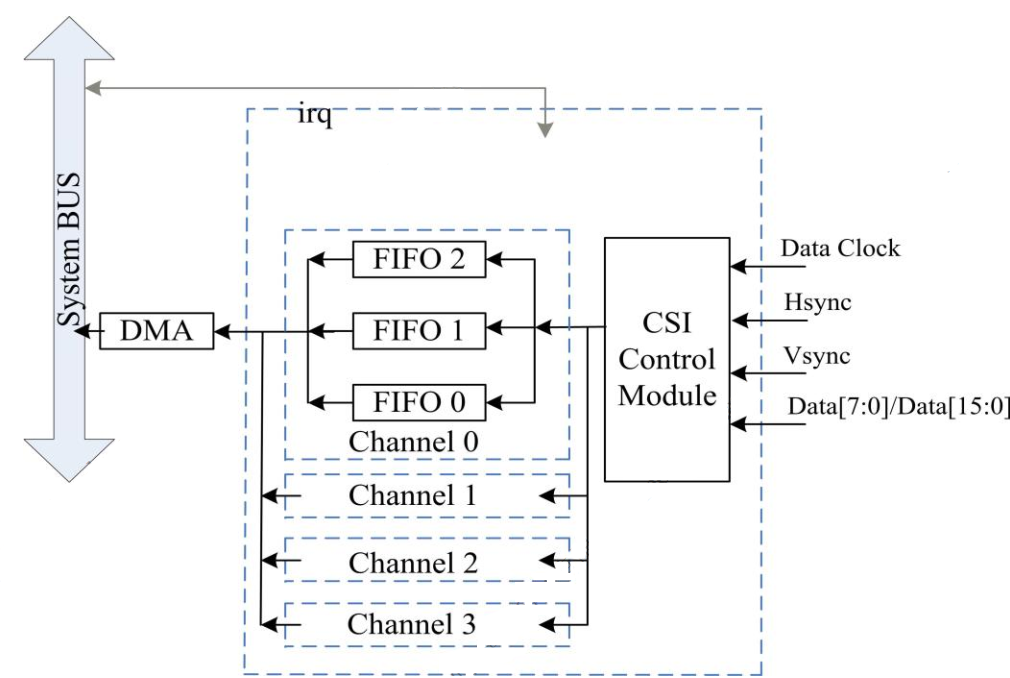

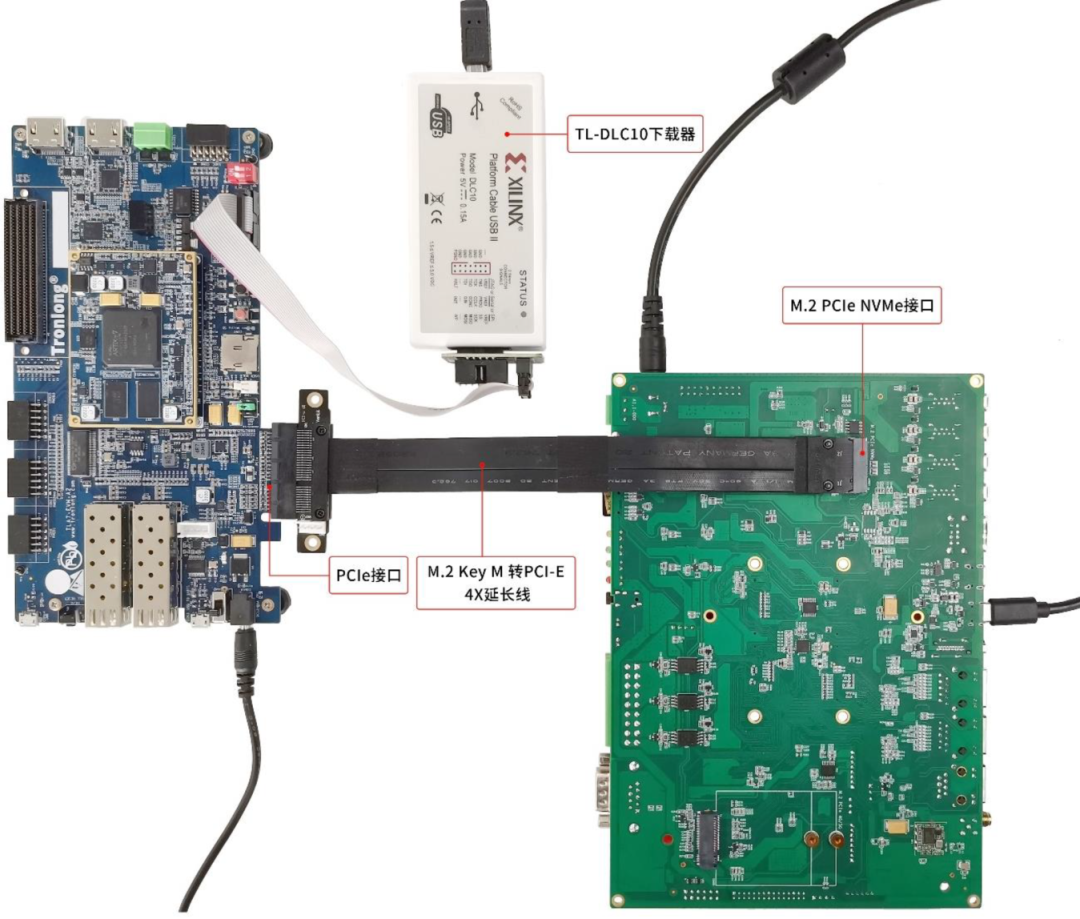

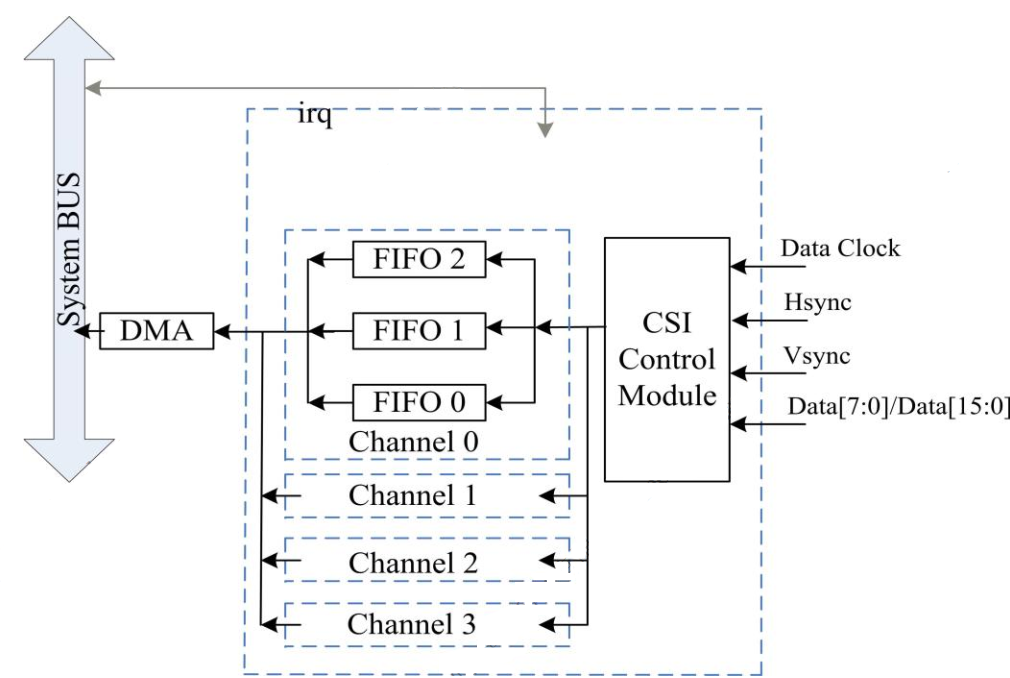

高速AD數據的傳輸需求。開發(fā)難度低:CSI總線采用并行數據和控制信號分離方式,時序簡單,FPGA端接口開發(fā)難度低。低成本:CSI總線采用并行傳輸方式,FPGA端使用資源少,對FPGA器件資源要求低

2024-07-17 11:25:24

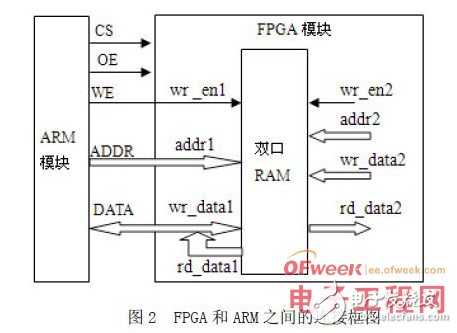

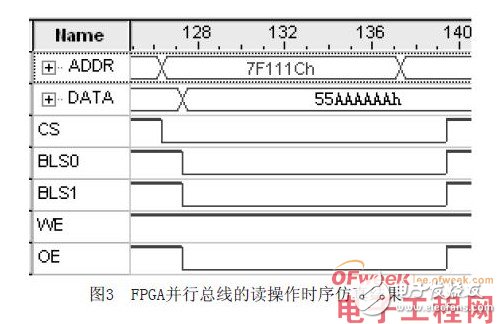

大、通信速率要求較高的情況,就要采用并行總線的方式了。這時把FPGA當做ARM的一個片外的SRAM訪問就可以,可以在FPGA內部生成一個雙口RAM,輸出的數據總線管腿直接連接到ARM的并行總線的數據總線

2017-01-12 19:00:53

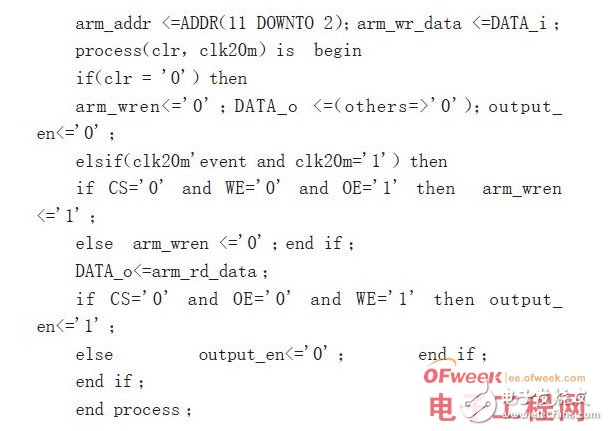

各位前輩,小弟現在剛開始學習ARM,想用ARM與FPGA并行總線通信。實驗過程是這樣的,我現在FPGA內部建立了一個雙口RAM,現在想通過ARM并行總線讀寫RAM,下面的是FPGA中RAM與ARM

2022-11-22 14:53:52

和W/R,左端口數據線(D0L~D15L)和地址線(A0L~A14L)也分別與局部總線的數據和地址線相連。雙口RAM右端口和標準VME總線通信,由FPGA負責譯碼標準VME總線控制信號線產生接口控制

2019-04-22 07:00:07

最近做的東西涉及到將原有的DSP+FPGA架構的程序移植到ZYNQ-7系列FPGA上,請問如何將原DSP程序移植到ZYNQ-7的ARM上,可不可以做一個EMIF總線和AXI總線轉換的模塊呢?

2014-05-12 21:51:09

對于60M10路并行總線一般采取多大的線寬和線間距,保證不會有串擾。芯片手冊上說的是這10路電平的上升和下降沿的時間為1ns,我用Allegro 定義的約束規(guī)則是:傳輸線阻抗70歐姆,傳輸延遲為0.1ns~0.5ns。板材為4層板,FR4。謝謝!

2014-04-12 23:15:26

高速串行總線與并行總線的差別是什么?高速測試方面的挑戰(zhàn)是什么?遠端環(huán)回的優(yōu)點是什么?

2021-05-12 06:31:54

AD1847串行端口音頻編解碼器如何與并行總線接口的實例

2009-05-13 09:54:41 25

25 AD1847串行端口音頻編解碼器如何與并行總線接口的實例

2009-05-15 15:13:14 27

27 采用 ARM7 內核芯片S3C4510 的高性能網絡控制器結合使用CPLD 設計VME 總線控制器邏輯時序,研制出了類似3U VME 的并行設備總線控制器。開發(fā)嵌入式系統uClinux的網絡通訊軟件,實現提供

2009-06-15 08:54:42 14

14 基于FPGA的PCI總線接口設計::PCI是一種高性能的局部總線規(guī)范,可實現各種功能標準的PCI總線卡。本文簡要介紹了PCI總線的特點、信號與命令,提出了一種利用高速FPGA實現PCI總線接

2009-06-25 08:17:18 49

49 PCA9564是一款采用CMOS工藝,支持并行總線與串行I2C總線通信轉換的接口器件,適用于微控制器/處理器使用并行總線擴展I2C總線接口。它支持并行總線與I2C總線雙向通信,在I2C總線上

2010-03-10 15:47:12 51

51 PCA9665是一款并行總線與串行I2C總線接口轉換的器件,適用于微控制器/處理器使用并行總線擴展I2C總線接口。它支持并行總線與I2C總線雙向通信,在I2C總線上,它可以設置為主機或從

2010-03-10 15:49:10 46

46 PCF8584是一款采用CMOS工藝制作的集成電路,微處理器/微控制器通過它可以將并行總線轉換成串行的I2C總線,它支持并行總線和串行I2C總線間的雙向通信。它既可以作為主機也可以作

2010-03-10 15:52:32 35

35 基于ARM的嵌入式軟件設計

駐留監(jiān)控軟件Resident Monitors 是一段運行在目標板上的程序集成開發(fā)環(huán)境中的調試模塊通過以太網口并行端口或者串行端口等通訊端口與

2010-03-31 14:59:20 44

44 基于Actel FPGA 的雙端口RAM 設計雙端口RAM 芯片主要應用于高速率、高可靠性、對實時性要求高的場合,如實現DSP與PCI 總線芯片之間的數據交換接口電路等。但普通雙端口RAM 最大

2010-11-15 17:44:19 83

83 并行端口工作原理

并行端口的基本知識

2009-07-27 12:16:13 3596

3596 本文設計的靶場破片測速系統以ARM處理器為控制核心,利用了FPGA強大的多路并行處理能力進行數據處理,在基于嵌入式Linux的平臺上采用Qt/Embedded設計了友好的人機交互界面。

2011-02-21 09:39:57 1321

1321

本文介紹的基于PCI總線的FPGA計算平臺的系統實現:通過在PC機上插入擴展PCI卡,對算法進行針對并行運算的設計,提升普通PC機對大計算量數字信號的處理速度。本設計采用5片FPGA芯片及

2011-08-21 18:05:31 2415

2415

本設計開發(fā)出了一套基于雙FPGA+ARM架構的高速計算機屏幕圖像壓縮系統。系統通過對圖像壓縮系統任務的劃分,利用FPGA的并行計算能力和靈活的編程方式,完成圖像壓縮算法。

2011-08-22 11:44:31 2613

2613

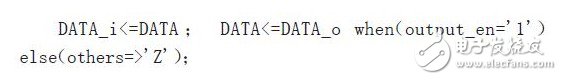

針對現場可編程門陣列(FPGA)芯片的特點,研究FPGA中雙向端口I/O的設計,同時給出仿真初始化雙向端口I/O的方法。采用這種雙向端口的設計方法,選用Xilinx的Spartan2E芯片設計一個多通道圖像信

2011-09-27 16:17:21 89

89 并行端口常為計算機開發(fā)人員作為用戶擴展端口使用。增強型并行端口協議從根本上改變了這一狀況,它不但與SPP兼容,又能進行雙向的高速數據傳輸。

2011-11-23 13:54:49 2893

2893

并行端口在接口設計工程中是最常用的。該端口在任何規(guī)定時間內將允許輸入達到9比特,輸出達到12比特。該端口由4條控制線,5條狀態(tài)線和8條數據線組成。在PC機后部常常可以見到作

2011-11-23 16:51:41 62

62 基于FPGA的ARM并行總線研究與仿真

2017-01-24 16:54:24 21

21 FPGA與ARM、DSP的區(qū)別

2017-03-15 08:00:00 9

9 本文介紹S3C2410芯片通過AHB總線與FPGA進行硬件連接技術和基于QuartuslI環(huán)境下AHB總線控制時序的實現方法以及ARM-Linux平臺下的AHB總線驅動程序的開發(fā)。

2017-08-30 15:37:45 3

3 本文介紹了FPGA電源設計并行工程的合理性,講解了并行工程(CE)技術及其作用,討論了FPGA電源系統設計的復雜性和不確定性。

2017-10-13 13:00:35 5

5 基于FPGA和多DSP的多總線并行處理器設計

2017-10-19 13:40:31 4

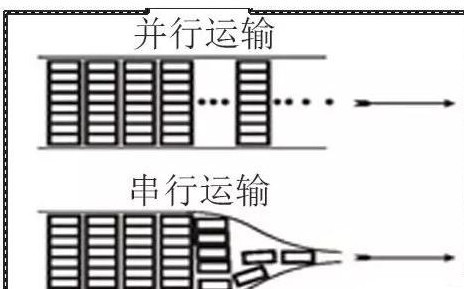

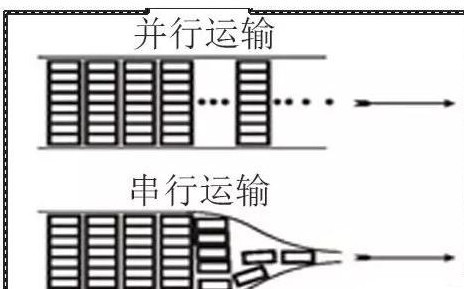

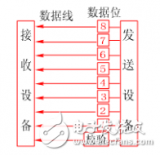

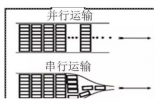

4 并行通信傳輸中有多個數據位,同時在兩個設備之間傳輸。發(fā)送設備將這些數據位通過 對應的數據線傳送給接收設備,還可附加一位數據校驗位。串行數據傳輸時,數據是一位一位地在通信線上傳輸的,先由具有幾位總線的計算機內的發(fā)送設備,將幾位并行數據經并--串轉換硬件轉換成串行方式

2017-11-13 09:15:29 41963

41963

并行總線,就是并行接口與計算機設備之間傳遞數據的通道。采用 并行傳送方式在 微型計算機與 外部設備之間進行 數據傳送的接口叫并行接口。

2017-11-13 09:19:47 86204

86204 并行總線,就是并行接口與計算機設備之間傳遞數據的通道。采用并行傳送方式在 微型計算機與外部設備之間進行數據傳送的接口叫并行接口,它有2個主要特點;一是同時并行傳送的二進位數就是數據寬度;二是在計算機與外設之間采用應答式的聯絡信號來協調雙方的數據傳送操作,這種聯絡信號又稱為握手信號。

2017-11-13 09:55:07 13977

13977

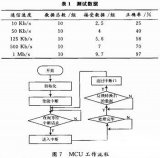

為了擴展VME總線和CAN總線的應用范圍,充分利用兩種總線的不同傳輸特點,采用了模塊設計方法,提出一種基于FPGA和MCU的總線轉換方案。該方案給出了FPGA與上位VME總線部分的VME總線接口

2018-07-17 10:11:00 4234

4234

本文結合實際系統中的前端圖像處理和圖像數據傳輸需要.充分利用ARM的靈活 性和FPGA的并行性特點,設計了一種基于ARM+FPGA的圖像快速采集傳輸系統。所選的ARM體系結構是32位嵌入式RISC

2017-11-24 09:23:21 5034

5034

傳統的基于模擬退火的現場可編程門陣列( FPGA)時序驅動布局算法在時延代價的計算上存在一定誤差,已有的時序優(yōu)化算法能夠改善布局質量,但增加了時耗。針對上述問題,提出一種基于事務內存( TM)的并行

2018-02-26 10:09:04 0

0 增強型并行主端口 (Enhanced Parallel Master Port, EPMP)提供了并行的 4 位 (僅適用于主 模式)、 8 位 (主模式和從模式)或 16 位 (僅適用于主模式

2018-06-22 05:20:00 1

1 PIC32系列中文參考手冊—第13章 并行主端口(PMP)

2018-05-25 17:29:29 14

14 并行總線波形捕獲與分析。

2018-06-25 15:44:00 4205

4205 AT24C04是具有I2C總線接口的EEPROM.大小為512*8bit.單片機AT89S52本身不具有I2C總線結口,所以可編寫程序用并行端口模擬I2C總線協議讀寫AT24C04.

2019-08-14 14:34:25 3192

3192 在以51單片機為核的小型電路設計中,沒有足夠的I/O端口與內部時鐘中斷實現I2C總線功能。本文運用VHDL語言對FPGA進行必要的編程,在不影響51單片機地址分配的同時能夠將8位并行數據轉化為符合

2019-08-19 08:00:00 3

3 簡要介紹了ARM體系及其特點,詳細分析了ARM的流水技術、Cache技術、低功耗技術、代碼壓縮技術等,介紹了AMBA總線,給出了基于ARM和AMBA總線的片上系統的模型.

2019-11-20 17:12:33 9

9 作為一名PCB設計工程師,具備一些高速方面的知識是非常有必要的,甚至說是必須的。就信號來說,高速信號通常見于各種并行總線與串行總線,只有知道了什么是總線,才能知道它跑多快,才能開始進行布線。

2020-07-29 17:43:17 3165

3165 作為一名PCB設計工程師,具備一些高速方面的知識是非常有必要的,甚至說是必須的。就信號來說,高速信號通常見于各種并行總線與串行總線,只有知道了什么是總線,才能知道它跑多快,才能開始進行布線。

2020-10-21 14:14:21 5916

5916

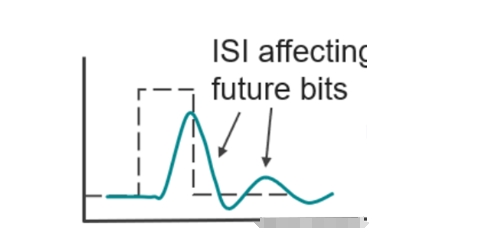

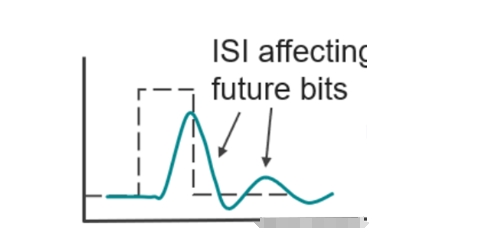

早些年的老式設備都采用并行傳輸,而現在的設備都采用串行傳輸。為什么并行傳輸會被串行傳輸所取代呢?

2021-06-11 15:19:49 20492

20492 ARM、MCU、DSP、FPGA、SOC的比較1、采用架構·? ?? ???ARM:架構采用32位精簡指令集(RISC)處理器架構,從ARM9開始ARM都采用了哈佛體系結構,這是一種將指令與數據分開

2021-11-05 21:05:59 24

24 51單片機系列--并行I/O端口基本概念數據的傳送方式I/O 端口特性基本概念51系列單片機的每個端口都是8位準雙向口,共占32位引腳。每個端口都包括一個鎖存器(一個D觸發(fā)器構成)、一個輸出驅動器

2021-11-20 11:21:05 12

12 CC2530并行I/O端口應用CC2530總共具有21個數字I/O引腳,這些引腳可以組成3個8位端口,分別為端口0、端口1和端口2,通常表示為P0、P1和P2。其中,P0和P1是完全的8位端口,而

2021-11-29 21:06:03 7

7 ADC和DAC是FPGA與外部信號的接口,從數據接口類型的角度劃分,有低速的串行接口和高速的并行接口。FPGA經常用來采集中高頻信號,因此使用并行ADC和DAC居多。本文將介紹如何使用FPGA驅動并行ADC和并行DAC芯片。

2022-04-21 08:55:22 8246

8246 SOT 降壓型 DC-DC 轉換器可有效地從并行端口“竊取”電源,同時 SIM/智能卡電平轉換集成電路 (IC) 完成接口。這允許并行端口為低壓邏輯供電并與之通信。同樣的技術也可以應用于USB設計。

2023-01-10 15:15:26 1780

1780

圖1所示電路從并行端口或任何有限的能量源竊取能量。這種功率轉換應用通常需要非常高的效率來利用可用的能量。例如,并行數據端口在2.6V時每條數據線可提供高達2.4mA的電流。當八條數據線通過軟件配置為

2023-02-09 15:46:48 1201

1201

ZYNQ擁有ARM+FPGA這個神奇的架構,那么ARM和FPGA究竟是如何進行通信的呢?本章通過剖析AXI總線源碼,來一探其中的秘密。

2023-02-16 09:26:57 14889

14889 廣州星嵌DSP/ARM/FPGA 選型手冊2023

2023-05-05 10:24:22 15

15 近年來,隨著中國新基建、中國制造2025的持續(xù)推進,單ARM處理器越來越難滿足工業(yè)現場的功能要求,特別是能源電力、工業(yè)控制、智慧醫(yī)療等行業(yè)通常需要ARM + FPGA架構的處理器平臺來實現特定的功能,例如多路/高速AD采集、多路網口、多路串口、多路/高速并行DI/DO、高速數據并行處理等。

2023-08-01 11:40:32 2694

2694

的靈活性和FPGA的并行性的特點,設計了一種基于ARM+FPGA的高速圖像數據采集傳輸系統。所選用的ARM體系結構是32位嵌入式RISC微處理器結構,該微處理器擁有豐富的指令集且編程靈活;而FPGA則在速度和并行運算方面有很大優(yōu)勢,適合圖像處理的實時性要求

2023-09-27 10:45:02 2692

2692 電子發(fā)燒友網站提供《基于FPGA的ARM并行總線設計原理.pdf》資料免費下載

2023-10-10 09:31:31 1

1 電子發(fā)燒友網站提供《基于ARM9平臺和FPGA的1553B總線測試系統的設計與實現.pdf》資料免費下載

2023-11-08 10:10:29 1

1 并行總線和串行總線的區(qū)別? 并行總線和串行總線是計算機系統中常見的兩種數據傳輸方式,它們有著不同的工作原理和應用場景。在這篇文章中,我將詳細介紹并行總線和串行總線的區(qū)別,并探討它們各自的優(yōu)勢和劣勢

2023-12-07 16:45:27 5838

5838 FPGA雙口RAM的使用主要涉及配置和使用雙端口RAM模塊。雙端口RAM的特點是有兩組獨立的端口,可以對同一存儲塊進行讀寫操作,從而實現并行訪問。

2024-03-15 13:58:14 2074

2074 方式,時序簡單,FPGA端接口開發(fā)難度低。 ? 低成本:CSI總線采用并行傳輸方式,FPGA端使用資源少

2024-03-28 09:03:30 1552

1552

高速并行總線的工作原理及其具體類型是一個涉及硬件技術和數據傳輸的復雜話題。以下是對高速并行總線工作原理的概述以及幾種常見的高速并行總線的介紹。 高速并行總線的工作原理 高速并行總線的工作原理主要涉及

2024-10-06 15:17:00 2322

2322

ADC和DAC是FPGA與外部信號的接口,從數據接口類型的角度劃分,有低速的串行接口和高速的并行接口。FPGA經常用來采集中高頻信號,因此使用并行ADC和DAC居多。本文將介紹如何使用FPGA驅動并行ADC和并行DAC芯片。

2025-03-14 13:54:12 1980

1980

電子發(fā)燒友App

電子發(fā)燒友App

評論