如果你已經(jīng)在用 MATLAB 做深度學習,那一定知道它的訓練和仿真體驗非常絲滑。但當模型要真正落地到 FPGA 上時,往往就會卡住:怎么把網(wǎng)絡(luò)結(jié)構(gòu)和權(quán)重優(yōu)雅地搬到硬件里?

這就是 MathWorks Deep Learning HDL Toolbox 出場的地方。

它能干什么?

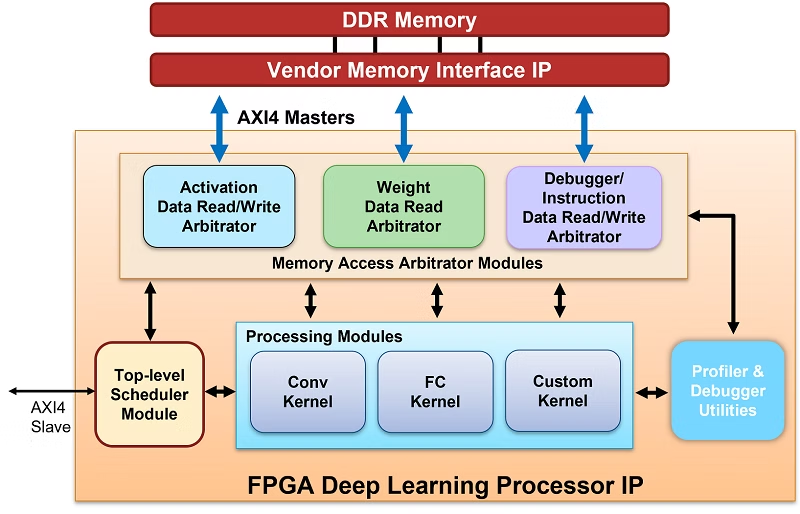

簡單來說,這個工具就是把你的神經(jīng)網(wǎng)絡(luò)“翻譯”成 FPGA 能跑的電路。它提供了一個現(xiàn)成的 Deep Learning Processor (DLP) IP 核,能直接放到 FPGA 里跑模型推理。

主要功能有:

自動生成 FPGA 工程:不需要手寫 RTL,只要在 MATLAB 定義好網(wǎng)絡(luò)結(jié)構(gòu),就能一鍵生成 Vivado 工程。

支持常見網(wǎng)絡(luò)層:卷積層、全連接層、激活層等常見模塊都內(nèi)置好,拖上去就能用。

硬件加速 AI 推理:推理過程完全在硬件里跑,沒有軟件瓶頸,延遲低、確定性強。

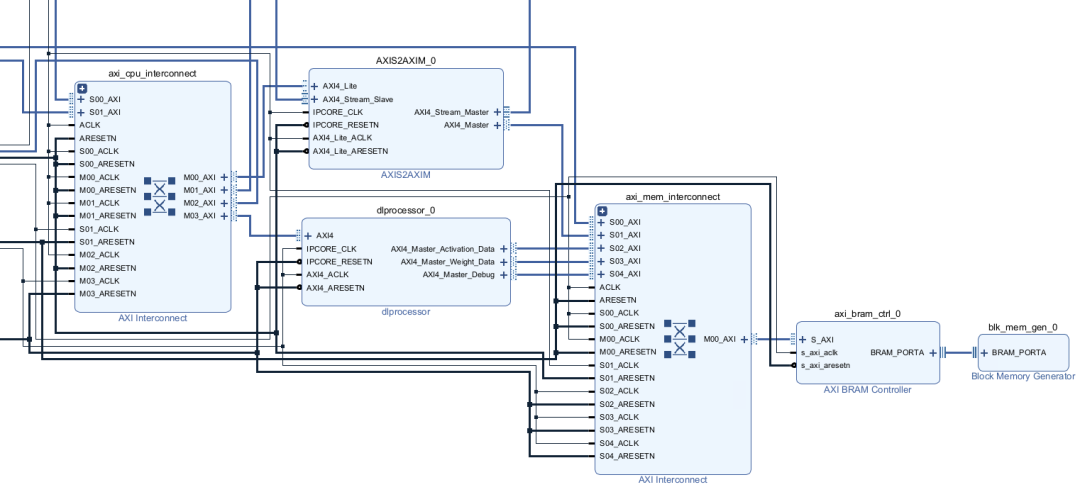

AXI 接口對接:DLP IP 自帶 AXI4-Lite/AXI4-Stream 接口,方便和其他 FPGA 邏輯或外設(shè)對接。

可定制化:支持修改網(wǎng)絡(luò)拓撲、算子精度,還能擴展自定義層。

參考設(shè)計入門

最快捷的入門方法是先在 MATLAB 中生成參考設(shè)計,然后 MATLAB 會生成一個針對 ZCU102 評估板的 Vivado 項目。該設(shè)計可以直接在 MATLAB 中使用 JTAG 接口進行測試。

設(shè)計架構(gòu)概述

該架構(gòu)非常簡單,只需幾分鐘即可運行應(yīng)用程序。

盡管參考設(shè)計使用了 SoC 設(shè)備,但處理器僅負責時鐘和復(fù)位信號。

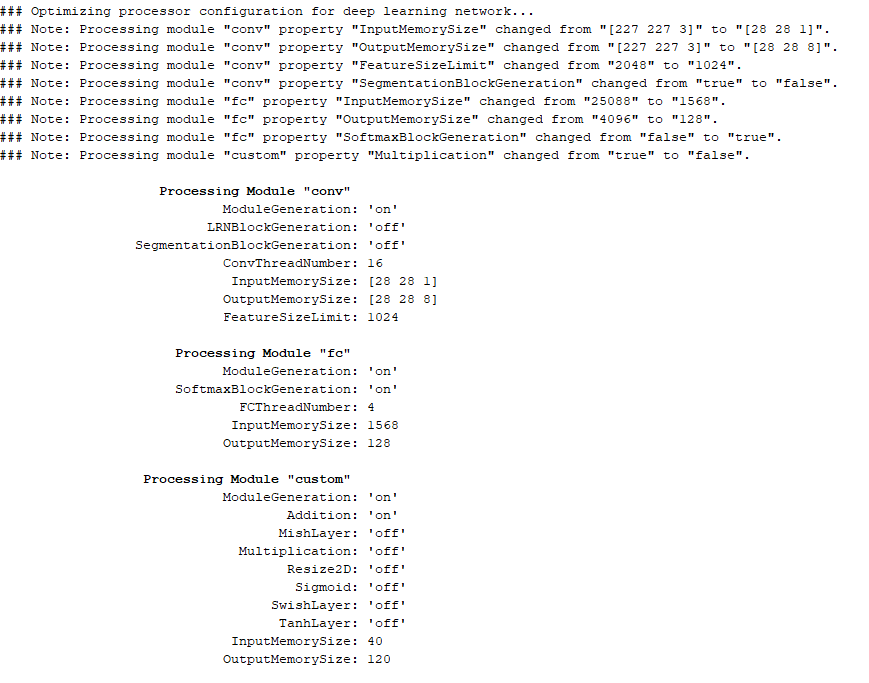

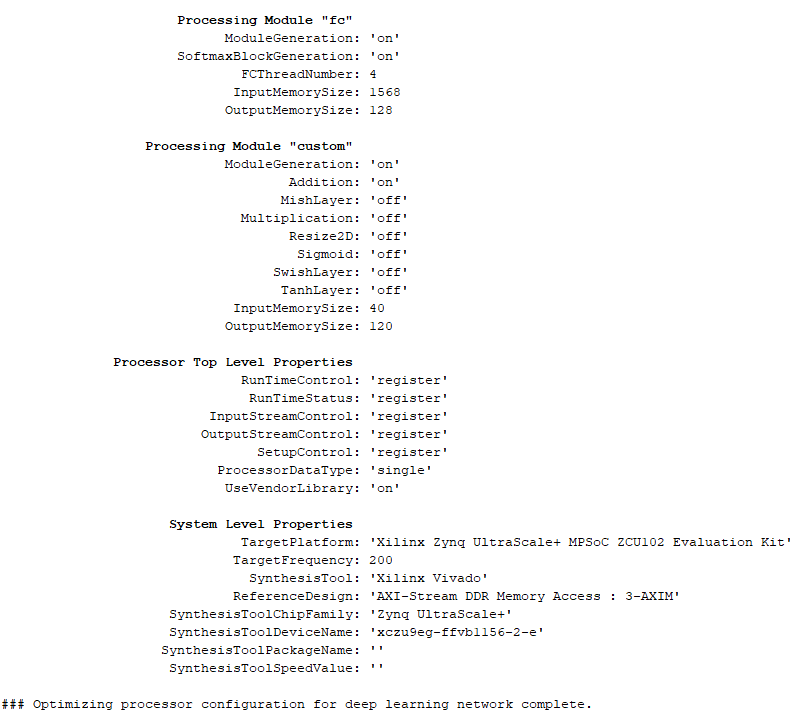

該過程從定義 DLP 及其接口的配置文件開始。

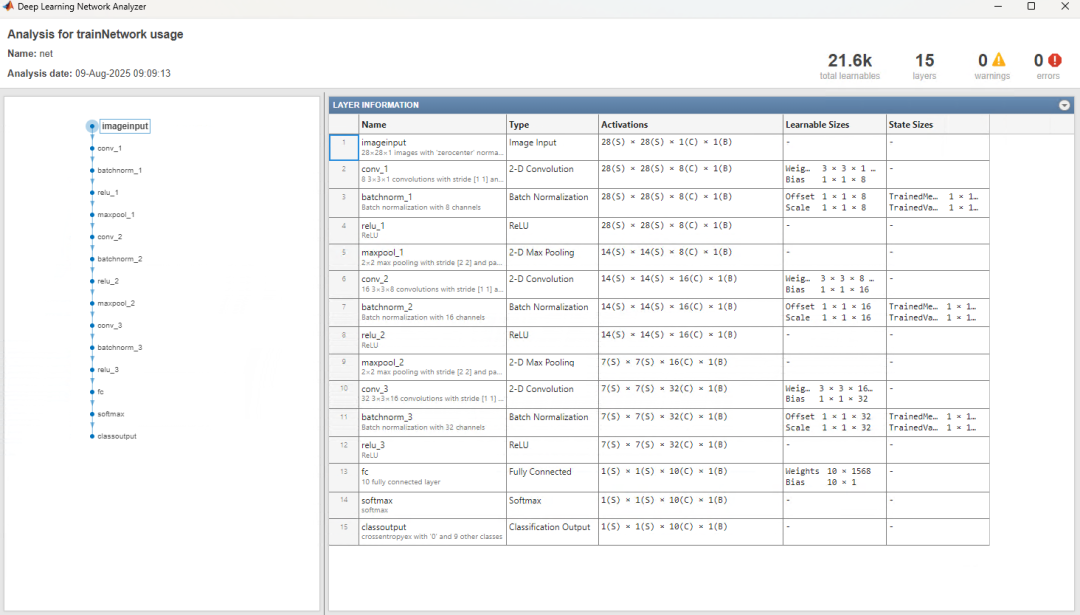

接下來,從 MATLAB 庫中導入了一個預(yù)訓練的MNIST 分類網(wǎng)絡(luò)。通過分析它,我們可以了解待實現(xiàn)網(wǎng)絡(luò)的結(jié)構(gòu)。

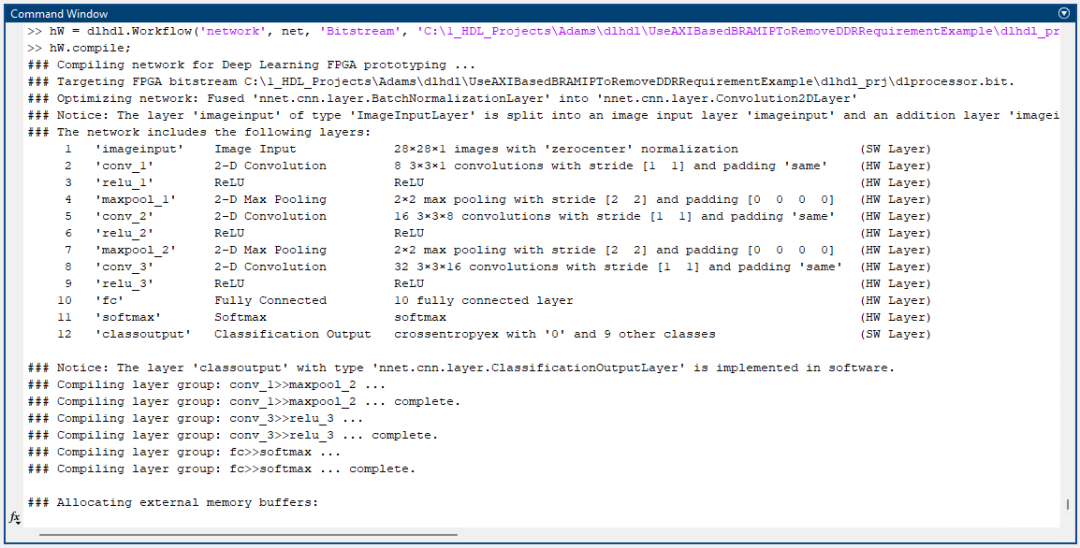

定義網(wǎng)絡(luò)后,處理器就會對其進行配置和優(yōu)化。

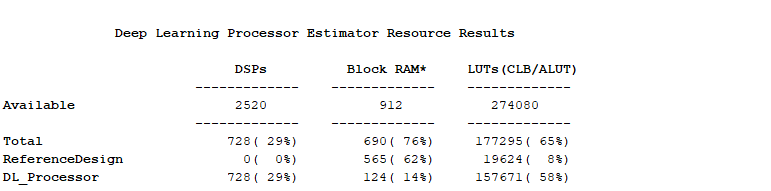

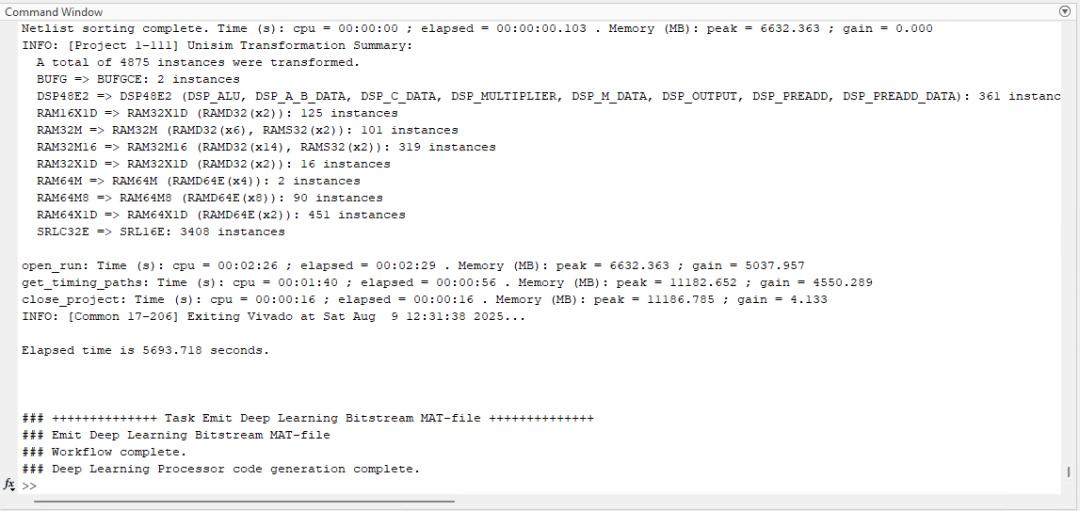

一旦處理器得到優(yōu)化,我們就可以讓 MATLAB 在 Vivado 中構(gòu)建深度學習 IP 設(shè)計。

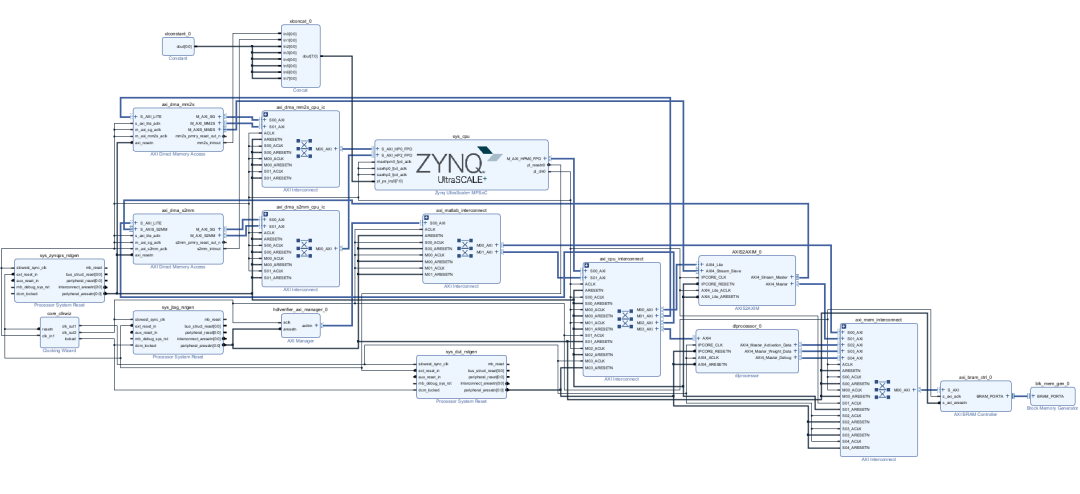

完成后就可以打開 Vivado 并探索該項目。將看到 AXI 互連、深度學習 IP 和 AXI 基礎(chǔ)架構(gòu)。

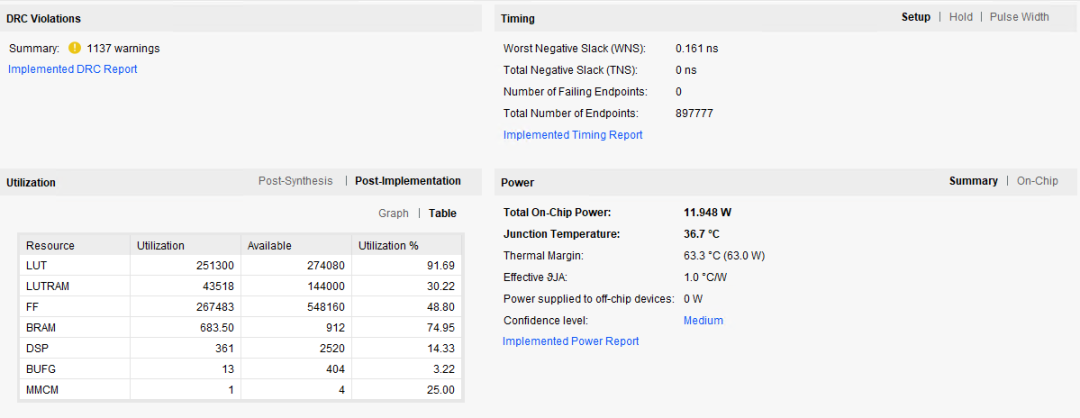

構(gòu)建和運行設(shè)計

優(yōu)化完成后,MATLAB 即可為 Vivado 構(gòu)建 DLP IP 設(shè)計。編譯只需幾分鐘,之后 Vivado 項目將顯示 AXI 互連、DLP IP 以及相關(guān)基礎(chǔ)架構(gòu)。

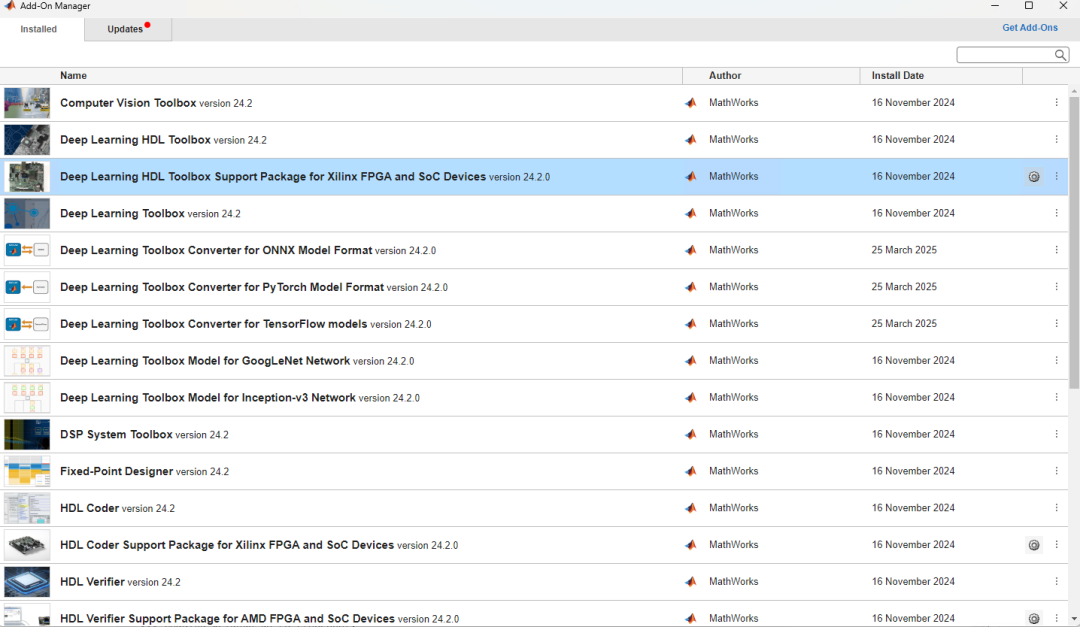

運行硬件示例之前,必須正確配置 Zynq 處理系統(tǒng) (PS),否則將不提供時鐘。這可以通過 從附加組件管理器安裝適用于 Xilinx FPGA 和 SoC 設(shè)備的深度學習 HDL 工具箱支持包來完成。

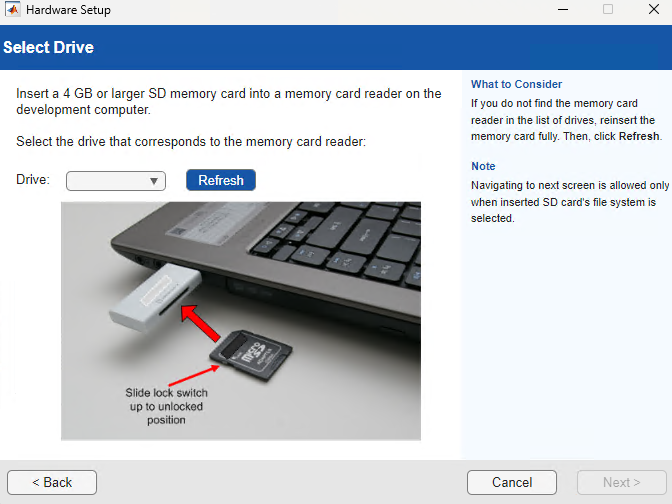

附加管理器還提供為 ZCU102 編程 SD 卡的工具,確保 PS 提供所需的時鐘和復(fù)位信號。

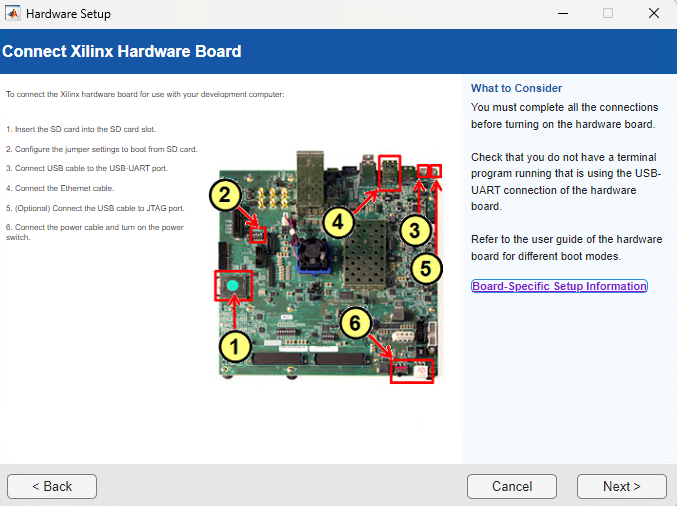

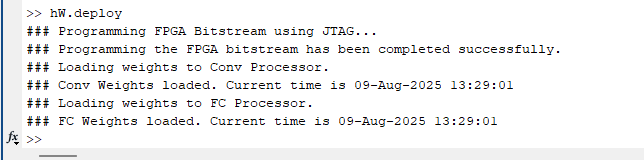

設(shè)置完成后,打開 ZCU102 的電源,將 JTAG 連接到開發(fā)板,并從 MATLAB 下載比特流。這還會使用網(wǎng)絡(luò)的權(quán)重和激活函數(shù)配置 FPGA 存儲器。

測試網(wǎng)絡(luò)

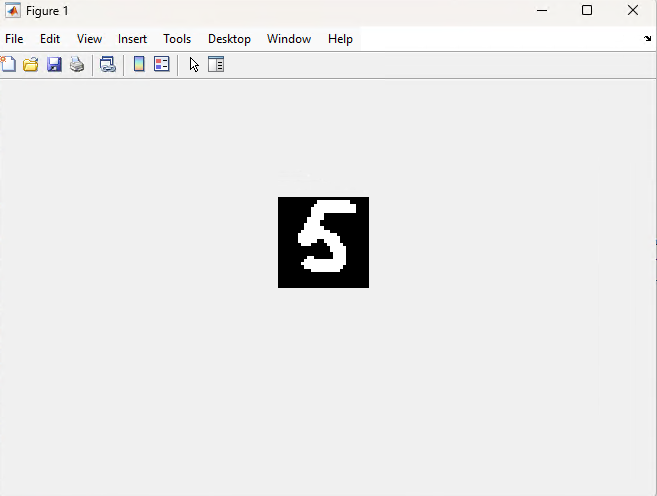

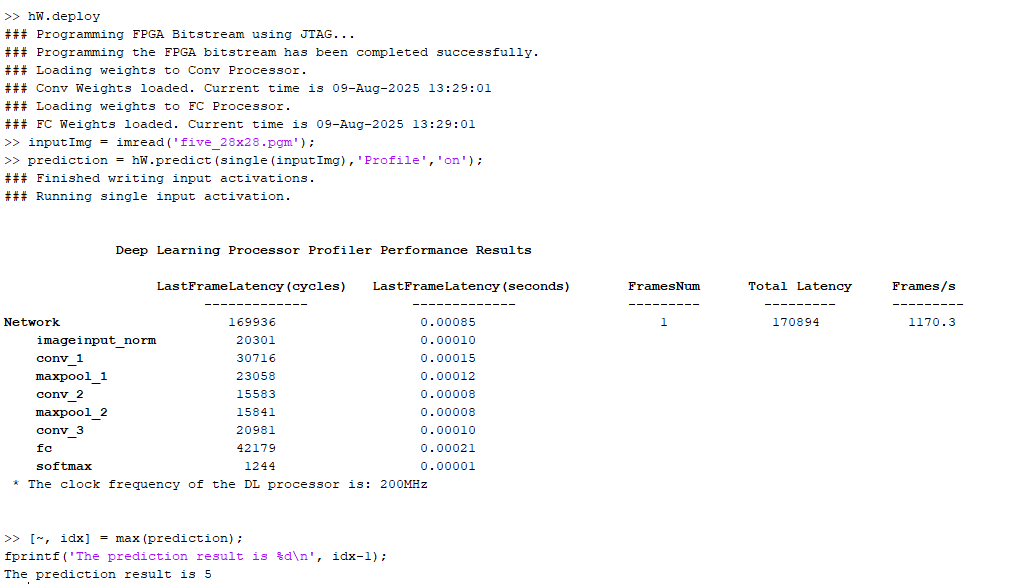

然后,加載一張簡單的圖像并進行推理。經(jīng)過訓練識別手寫數(shù)字的 MNIST 網(wǎng)絡(luò)通過 JTAG 鏈路返回了正確的預(yù)測。

由于啟用了分析功能,可以查看推理結(jié)果和性能指標。雖然這是一個簡單的網(wǎng)絡(luò),但速度還是很快的。

小結(jié)

MathWorks Deep Learning HDL Toolbox 其實就是一條“AI 模型到 FPGA 的高速通道”。

它幫你把 MATLAB 里的深度學習模型,直接翻譯成可運行在 FPGA 上的硬件結(jié)構(gòu),還自帶了一個成熟的 DLP 引擎,降低了從算法到部署的門檻。

一句話:如果你在 FPGA 上搞 AI,這個工具能幫你把“想法”快速變成“硬件”。

來源:本文轉(zhuǎn)載自O(shè)PENFPGA公眾號

-

FPGA

+關(guān)注

關(guān)注

1661文章

22440瀏覽量

637286 -

matlab

+關(guān)注

關(guān)注

189文章

3027瀏覽量

238860 -

深度學習

+關(guān)注

關(guān)注

73文章

5600瀏覽量

124466

原文標題:FPGA 上的 AI“神器”:MathWorks Deep Learning HDL Toolbox

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

如何在FPGA部署AI模型

如何在FPGA部署AI模型

評論