現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)是一種高度靈活的硬件平臺(tái),它允許開(kāi)發(fā)者根據(jù)特定應(yīng)用需求定制硬件邏輯。在實(shí)時(shí)信號(hào)處理和圖像處理領(lǐng)域,F(xiàn)PGA因其獨(dú)特的優(yōu)勢(shì)而受到青睞。

1. 并行處理能力

FPGA的最大優(yōu)勢(shì)之一是其并行處理能力。與傳統(tǒng)的CPU或GPU相比,F(xiàn)PGA可以同時(shí)執(zhí)行多個(gè)操作,這在圖像處理中尤為重要,因?yàn)閳D像處理通常涉及大量的并行數(shù)據(jù)流和復(fù)雜的算法。例如,在進(jìn)行圖像濾波或邊緣檢測(cè)時(shí),F(xiàn)PGA可以同時(shí)處理多個(gè)像素,從而顯著提高處理速度。

2. 低延遲

在實(shí)時(shí)信號(hào)處理中,延遲是一個(gè)關(guān)鍵因素。FPGA的硬件邏輯可以直接在數(shù)據(jù)流上操作,無(wú)需像CPU那樣進(jìn)行復(fù)雜的指令調(diào)度和緩存管理,這使得FPGA能夠?qū)崿F(xiàn)極低的延遲。這對(duì)于需要快速響應(yīng)的應(yīng)用,如視頻監(jiān)控、自動(dòng)駕駛車(chē)輛的視覺(jué)系統(tǒng)等,至關(guān)重要。

3. 可定制性

FPGA的另一個(gè)顯著優(yōu)勢(shì)是其可定制性。開(kāi)發(fā)者可以根據(jù)特定的算法需求設(shè)計(jì)和優(yōu)化硬件邏輯,以實(shí)現(xiàn)最佳的性能。這種定制性不僅包括邏輯設(shè)計(jì),還包括內(nèi)存布局、接口設(shè)計(jì)等,使得FPGA能夠適應(yīng)各種不同的圖像處理任務(wù)。

4. 能耗效率

盡管FPGA在處理速度上可能不如專(zhuān)用的GPU,但其能耗效率通常更高。FPGA只有在需要時(shí)才激活特定的硬件邏輯,這意味著在處理輕量級(jí)任務(wù)時(shí),F(xiàn)PGA可以顯著降低能耗。這對(duì)于電池供電的移動(dòng)設(shè)備或需要長(zhǎng)時(shí)間運(yùn)行的系統(tǒng)尤為重要。

5. 可靠性和穩(wěn)定性

FPGA的硬件邏輯是固定的,這使得它們?cè)谶\(yùn)行時(shí)更加穩(wěn)定和可靠。與軟件相比,硬件邏輯不容易出現(xiàn)bug或受到惡意軟件的影響。在需要高可靠性的應(yīng)用,如醫(yī)療成像或工業(yè)自動(dòng)化中,F(xiàn)PGA的這一特性尤為重要。

6. 實(shí)時(shí)處理能力

FPGA能夠?qū)崿F(xiàn)真正的實(shí)時(shí)處理,這意味著它們可以在數(shù)據(jù)到達(dá)時(shí)立即處理,而不需要緩沖或排隊(duì)。這對(duì)于需要即時(shí)反饋的應(yīng)用,如實(shí)時(shí)視頻分析或監(jiān)控系統(tǒng),是非常有價(jià)值的。

7. 可擴(kuò)展性

FPGA的設(shè)計(jì)允許開(kāi)發(fā)者根據(jù)需要添加更多的邏輯資源,以處理更復(fù)雜的圖像處理任務(wù)。這種可擴(kuò)展性使得FPGA可以適應(yīng)不斷變化的應(yīng)用需求,而無(wú)需更換整個(gè)硬件平臺(tái)。

8. 成本效益

雖然FPGA的初始成本可能高于傳統(tǒng)的處理器,但其在長(zhǎng)期運(yùn)行中的能耗降低和維護(hù)成本降低可以帶來(lái)成本效益。此外,F(xiàn)PGA的可定制性意味著它們可以被優(yōu)化以執(zhí)行特定的任務(wù),從而減少浪費(fèi)的計(jì)算資源。

9. 快速原型開(kāi)發(fā)

FPGA允許開(kāi)發(fā)者快速原型開(kāi)發(fā)和測(cè)試新的算法。由于FPGA的硬件邏輯可以被重新編程,開(kāi)發(fā)者可以在不更換硬件的情況下測(cè)試和優(yōu)化算法,這大大加快了開(kāi)發(fā)周期。

10. 適應(yīng)性

FPGA可以適應(yīng)不同的圖像處理標(biāo)準(zhǔn)和格式,這使得它們?cè)诙嗝襟w應(yīng)用中非常有用。隨著新的圖像處理技術(shù)和標(biāo)準(zhǔn)的出現(xiàn),F(xiàn)PGA可以通過(guò)重新編程來(lái)適應(yīng)這些變化,而無(wú)需更換硬件。

結(jié)論

FPGA在實(shí)時(shí)信號(hào)處理和圖像處理中的應(yīng)用提供了許多優(yōu)勢(shì),包括并行處理能力、低延遲、可定制性、能耗效率、可靠性、實(shí)時(shí)處理能力、可擴(kuò)展性、成本效益、快速原型開(kāi)發(fā)和適應(yīng)性。

-

FPGA

+關(guān)注

關(guān)注

1660文章

22410瀏覽量

636254 -

gpu

+關(guān)注

關(guān)注

28文章

5194瀏覽量

135432 -

圖像處理

+關(guān)注

關(guān)注

29文章

1342瀏覽量

59507 -

信號(hào)處理

+關(guān)注

關(guān)注

49文章

1143瀏覽量

105098

發(fā)布評(píng)論請(qǐng)先 登錄

FPGA 信號(hào)處理板卡設(shè)計(jì)原理圖:618-基于FMC+的XCVU3P高性能 PCIe 載板

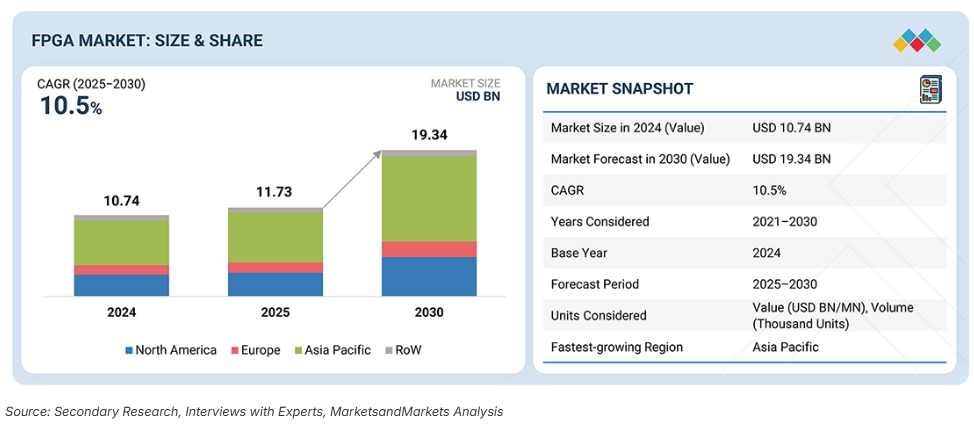

MarketsandMarkets FPGA行業(yè)報(bào)告,2026~2030 FPGA市場(chǎng)洞察

誰(shuí)家在低成本MCU中集成CPLD/FPGA,這有何優(yōu)勢(shì)呢?

AMD Spartan UltraScale+ FPGA的優(yōu)勢(shì)和亮點(diǎn)

FPGA+DSP/ARM架構(gòu)開(kāi)發(fā)與應(yīng)用

【VPX637】青翼凌云科技基于 XCKU115 FPGA+ZU15EG MPSOC 的 6U VPX 雙 FMC 接口通用信號(hào)處理平臺(tái)

【TES817】青翼凌云科技基于XCZU19EG FPGA的高性能實(shí)時(shí)信號(hào)處理平臺(tái)

光纖圖像處理卡設(shè)計(jì)原理圖:520-基于ZU15EG 適配AWR2243的雷達(dá)驗(yàn)證底板 XCZU15EG架構(gòu)高速信號(hào)處理板

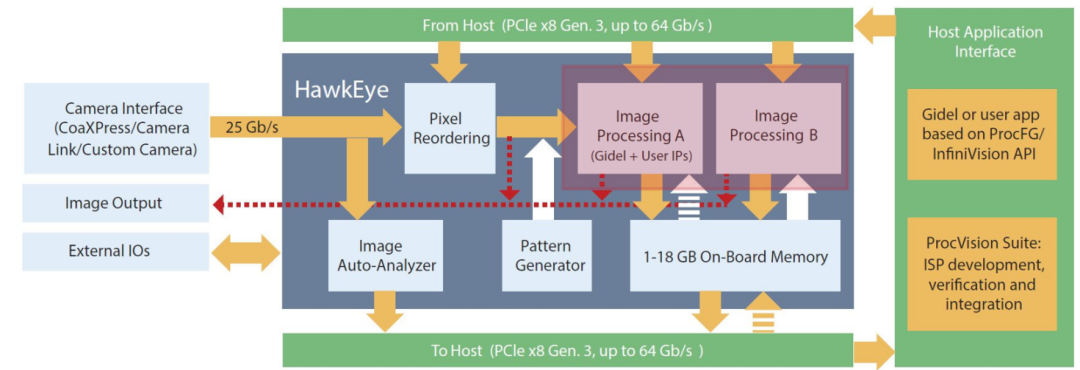

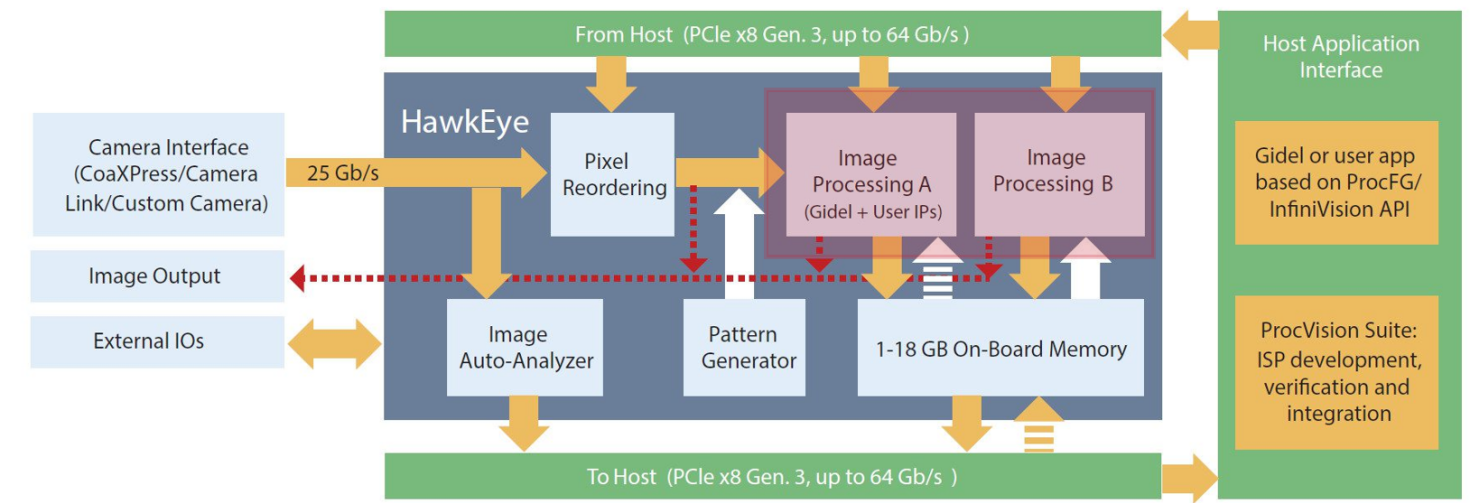

友思特方案 | FPGA 加持,友思特圖像采集卡高速預(yù)處理助力視覺(jué)系統(tǒng)運(yùn)行提速增效

FPGA 加持,友思特圖像采集卡高速預(yù)處理助力視覺(jué)系統(tǒng)運(yùn)行提速增效

FPGA 實(shí)時(shí)信號(hào)處理應(yīng)用 FPGA在圖像處理中的優(yōu)勢(shì)

FPGA 實(shí)時(shí)信號(hào)處理應(yīng)用 FPGA在圖像處理中的優(yōu)勢(shì)

評(píng)論