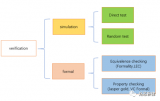

在開發(fā)流程中,設(shè)計(jì)和

驗(yàn)證人員關(guān)注的點(diǎn)肯定是不一樣的,尤其在spec的理解上,

驗(yàn)證人員往往需要有自己獨(dú)立的理解。在拿到spec時(shí),作為

驗(yàn)證人員,應(yīng)該如何提煉其中的功能從而轉(zhuǎn)化為對應(yīng)的inference model以

實(shí)現(xiàn)和詳細(xì)設(shè)計(jì)的交叉

驗(yàn)證。大家有什么經(jīng)驗(yàn)?zāi)苡懻撘幌隆?/div>

2017-10-25 11:16:28 13728

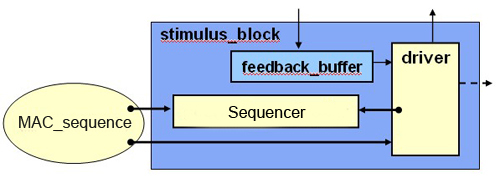

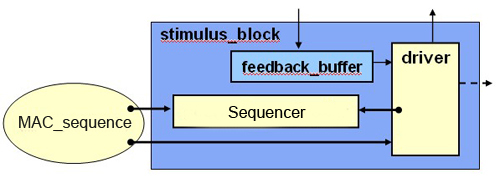

13728 MUC指令需要時(shí)鐘周期較少。##基于VMM的MCU驗(yàn)證結(jié)構(gòu)##驗(yàn)證功能模塊的具體實(shí)現(xiàn)##驅(qū)動(dòng)與模型##結(jié)論

2014-03-24 14:07:47 3820

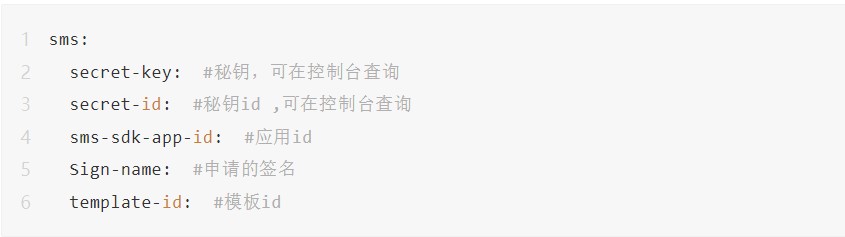

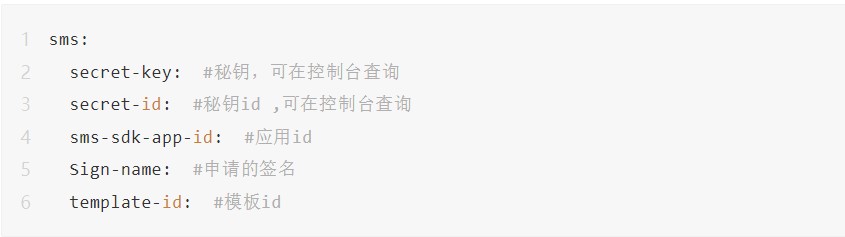

3820 現(xiàn)在大多數(shù)app或wap都實(shí)現(xiàn)了通過手機(jī)號獲取驗(yàn)證碼進(jìn)行驗(yàn)證登錄,下面來看下用go來實(shí)現(xiàn)手機(jī)號發(fā)送短信驗(yàn)證碼登錄的過程,基于的框架是gin 。

2022-07-20 09:36:03 5553

5553

1 簡介

隨著設(shè)計(jì)的復(fù)雜程度不斷增加,要求把更多的資源放到驗(yàn)證上,不但要求驗(yàn)證能夠覆蓋所有的功能,還希望能夠給出大量的異常情況來檢查DUT對應(yīng)異常的處理狀態(tài),這在傳統(tǒng)測試方法下往往是難以實(shí)現(xiàn)

2023-08-25 16:45:55 1547

1547 1 簡介

隨著設(shè)計(jì)的復(fù)雜程度不斷增加,要求把更多的資源放到驗(yàn)證上,不但要求驗(yàn)證能夠覆蓋所有的功能,還希望能夠給出大量的異常情況來檢查DUT對應(yīng)異常的處理狀態(tài),這在傳統(tǒng)測試方法下往往是難以實(shí)現(xiàn)

2023-08-29 17:00:51 1504

1504 和標(biāo)準(zhǔn)化。 在第一個(gè)專用 HVL(硬件驗(yàn)證語言)出現(xiàn)后不久,驗(yàn)證方法就應(yīng)運(yùn)而生。采用方法論(如 UVM)的主要優(yōu)點(diǎn)是? 通過測試臺(tái)重用和驗(yàn)證 IP 實(shí)現(xiàn)即插即用的可重用性? 一種行之有效的方法,具有行業(yè)

2022-02-13 17:03:49

原型驗(yàn)證---用軟件的方法來發(fā)現(xiàn)硬件的問題 在芯片tap-out之前,通常都會(huì)計(jì)算一下風(fēng)險(xiǎn),例如存在一些的嚴(yán)重錯(cuò)誤可能性。通常要某個(gè)人簽字來確認(rèn)是否去生產(chǎn)。這是一個(gè)艱難的決定。ASIC的產(chǎn)品NRE

2019-07-11 08:19:24

C語言接口與實(shí)現(xiàn)--創(chuàng)建可重用軟件的技術(shù)

2016-11-07 17:17:51

DSN(Data Source Name,數(shù)據(jù)源名)。LabSQL與數(shù)據(jù)庫之間的連接就是建立在DSN 基礎(chǔ)之上的。但是這種過于麻煩,在生成操作程序時(shí)不便于安裝,于是需要一種可以在LabView中直接創(chuàng)建數(shù)據(jù)源的方法。通過資料查證和編程驗(yàn)證確定了在LabView中更改注冊表的方法可以實(shí)現(xiàn)動(dòng)態(tài)創(chuàng)建數(shù)據(jù)源。

2012-09-23 01:53:00

求助:Labview 如何實(shí)現(xiàn)多窗口,且窗口可相互切換????

2015-11-16 19:35:44

,點(diǎn)擊下一步(如勾選“數(shù)據(jù)摘要”及/或“標(biāo)頭摘要”選項(xiàng),當(dāng)iSCSI啟動(dòng)器聯(lián)機(jī)iSCSI Target 時(shí)這些選項(xiàng)的內(nèi)容將需要被驗(yàn)證;CHAP防止別人隨便掛載你的ISCSI,需要可填寫賬號密碼驗(yàn)證

2019-12-11 14:14:28

要知道邊界在哪?驗(yàn)證的流程并行于設(shè)計(jì)流程。對于每個(gè)設(shè)計(jì)模塊,設(shè)計(jì)者需要首先閱讀硬件規(guī)范,解析其中的自然語言表述,然后使用RTL代碼之類的機(jī)器語言創(chuàng)建相應(yīng)的邏輯。為了完成這個(gè)過程,設(shè)計(jì)者需要知道輸入格式

2020-12-03 18:45:39

c接口和實(shí)現(xiàn):創(chuàng)建可重用軟件的技術(shù) 源碼分享關(guān)于如何設(shè)計(jì)、實(shí)現(xiàn)和有效使用庫函數(shù)的指南少之又少(如果說還有的話)。這本書作填補(bǔ)了這個(gè)空白。它可以作為下一代軟件的工具書,所有的C語言程序員都應(yīng)該閱讀。

2018-02-07 21:21:27

L5.15.71-2.2.0 — 2023 年 2 月 17 日

在文檔中有構(gòu)建復(fù)合固件的信息。

我沒有找到為 ls1028 構(gòu)建它的方法。

如何創(chuàng)建可啟動(dòng) SD卡?

2023-05-09 08:46:24

。利用形式驗(yàn)證的技術(shù),不用創(chuàng)建testbench就可以探索設(shè)計(jì)的行為。? Bug hunting FPV。針對一個(gè)使用EDA仿真驗(yàn)證的模塊,驗(yàn)證其中的corner case。? “Traditional

2022-06-27 16:40:45

性能的同時(shí),縮短設(shè)計(jì)周期,降低開發(fā)成本,采用了半定制/全定制混合設(shè)計(jì)的方法,對RTL級代碼進(jìn)行優(yōu)化改進(jìn),對處理器內(nèi)核的執(zhí)行單元采用全定制設(shè)計(jì)實(shí)現(xiàn)。混合設(shè)計(jì)的復(fù)雜性,給驗(yàn)證工作帶來了巨大的挑戰(zhàn)。本文針對

2011-12-07 17:40:14

1 簡介隨著設(shè)計(jì)的復(fù)雜程度不斷增加,要求把更多的資源放到驗(yàn)證上,不但要求驗(yàn)證能夠覆蓋所有的功能,還希望能夠給出大量的異常情況來檢查DUT對應(yīng)異常的處理狀態(tài),這在傳統(tǒng)測試方法下往往是難以實(shí)現(xiàn)的。此外

2019-07-03 07:40:26

1 簡介 隨著設(shè)計(jì)的復(fù)雜程度不斷增加,要求把更多的資源放到驗(yàn)證上,不但要求驗(yàn)證能夠覆蓋所有的功能,還希望能夠給出大量的異常情況來檢查DUT對應(yīng)異常的處理狀態(tài),這在傳統(tǒng)測試方法下往往是難以實(shí)現(xiàn)的。此外

2019-07-01 08:15:47

我想使用 AES 密鑰與 se050 創(chuàng)建經(jīng)過身份驗(yàn)證的會(huì)話。nano 包似乎不支持這一點(diǎn)。我的理解正確嗎?

這很重要 b/c 我想為特定密鑰的安全密鑰和數(shù)據(jù)設(shè)置策略。我知道您可以在設(shè)置策略時(shí)將

2023-06-08 08:36:39

找到源文件。本文將解析如何實(shí)現(xiàn)Ozone項(xiàng)目(.jdebug)可移植。1、解決方式在Ozone中,使用項(xiàng)目向?qū)陆?xiàng)目時(shí)(Ozone調(diào)試器使用攻略),如果導(dǎo)入的elf文件和對應(yīng)的源文件位于同一文件夾中

2023-01-05 13:56:53

的,因?yàn)橐坏┠阕龅剑涂梢越鹗癁殚_。”事實(shí)上,設(shè)計(jì)和驗(yàn)證SoC并非易事。一個(gè)原因源于選擇和靈活性,凡事有利必有弊,組裝芯片也如此。例如,就ARM而言,企業(yè)既可購買由英國公司設(shè)計(jì)的現(xiàn)成處理器,也可自己構(gòu)建運(yùn)行

2017-04-05 14:17:46

可重構(gòu)技術(shù)具有什么優(yōu)點(diǎn)?怎么實(shí)現(xiàn)基于FPGA可重構(gòu)智能儀器的設(shè)計(jì)

2021-05-06 06:44:38

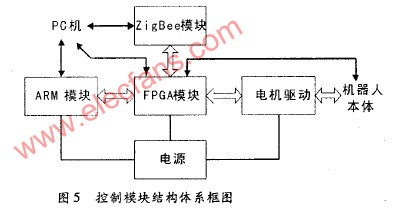

本文提出的通過微處理器加FPGA結(jié)合串行菊花鏈實(shí)現(xiàn)可重構(gòu)的方式,實(shí)現(xiàn)了動(dòng)態(tài)可重構(gòu)FPGA結(jié)構(gòu)設(shè)計(jì)的一種應(yīng)用。

2021-05-10 06:22:19

本文提出了一種基于FPGA的NoC驗(yàn)證平臺(tái)。詳細(xì)討論了該驗(yàn)證平臺(tái)中FPGA硬件平臺(tái)和NoC軟件的基本功能,并闡述了TG/R,MPU,MPI以及NoC軟件的可重用性等特點(diǎn)。通過一個(gè)實(shí)例仿真驗(yàn)證的結(jié)果說明了該驗(yàn)證平臺(tái)的基本功能和優(yōu)越性。

2021-05-06 07:20:48

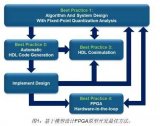

如何去設(shè)計(jì)一款合理的電子硬件解決方案,從而實(shí)現(xiàn)經(jīng)濟(jì)有效的大規(guī)模生產(chǎn)與部署?怎樣去驗(yàn)證可部署目標(biāo)硬件與軟件算法模型之間的算法性能一致性?System Generator是什么?有什么功能?

2021-04-08 06:25:48

實(shí)際產(chǎn)品的測試需要,提出了基于JTAG接口的,包括了上述四中測試手段的可測性設(shè)計(jì)方案。該方案經(jīng)過SMIC 0.18微米工藝流片驗(yàn)證,不僅證明功能正確,而且在保證了一定的覆蓋率的條件下實(shí)現(xiàn)了較低的測試成本,是‘項(xiàng)非常實(shí)用的測試設(shè)計(jì)方案。數(shù)模混合SOC芯片的可測性方案的實(shí)現(xiàn)[hide][/hide]

2011-12-12 17:58:16

當(dāng)今硬件設(shè)計(jì)變得愈加復(fù)雜,如何創(chuàng)建出足夠的測試來保證設(shè)計(jì)的正確性是每個(gè)硬件工程師需要面對的問題。Accellera的可移植激勵(lì)測試規(guī)范(PSS、又稱便攜激勵(lì)標(biāo)準(zhǔn))[1]旨在希望能夠提供一個(gè)獨(dú)立

2020-12-18 06:23:31

驗(yàn)證平臺(tái)中定義的參數(shù)和變量,既可調(diào)整仿真的行為,也可約束配置的范圍,是對驗(yàn)證平臺(tái)的必要的裝點(diǎn)和修飾。若把驗(yàn)證平臺(tái)比作一個(gè)姑娘,那么參數(shù)和變量就像是姑娘身上的發(fā)卡、耳環(huán)、項(xiàng)鏈和手表。 通常驗(yàn)證者會(huì)創(chuàng)建一

2023-04-04 17:20:51

(使用 UVM Acceleration for e 方法)可以創(chuàng)建高度可重用的代碼,尤其是當(dāng)測試臺(tái)是按照通用驗(yàn)證方法 (UVM) 編寫時(shí) Specman 作為工具/編譯器/調(diào)試器提供以使用 E 語言

2022-02-16 13:36:53

C語言接口與實(shí)現(xiàn)(創(chuàng)建可重用軟件的技術(shù))概念清晰、內(nèi)容新穎、實(shí)例詳盡,是一本有關(guān)設(shè)計(jì)、實(shí)現(xiàn)和有效使用C語言庫函數(shù),掌握創(chuàng)建可重用C語言軟件模塊技術(shù)的參考指南。C語言接口與實(shí)現(xiàn)(創(chuàng)建可重用軟件的技術(shù)

2023-09-25 06:42:59

在紅外線的增強(qiáng)處理中,怎么用quartusII進(jìn)行算法的實(shí)現(xiàn)及其仿真驗(yàn)證,重點(diǎn)是直方圖算法,這里面的代碼是什么。

2015-05-06 23:01:22

請問遠(yuǎn)程執(zhí)行IC驗(yàn)證是怎么實(shí)現(xiàn)的?

2021-06-17 10:27:33

可重構(gòu)計(jì)算技術(shù)概述隨著20世紀(jì)80年代中期Xilinx公司推出其第一款現(xiàn)場可編程門陣列(FPGA)以來,另一種實(shí)現(xiàn)手段——可重構(gòu)計(jì)算技術(shù)逐漸受到人們的重視,因?yàn)樗軌蛱峁┯布δ艿男屎蛙浖目删幊绦?隨著可編程器件容量根據(jù)摩爾定律的不斷增大和自動(dòng)設(shè)計(jì)技術(shù)的發(fā)展,可重構(gòu)技術(shù)正迅速地成熟起來。

2019-07-29 06:26:03

摘要: 為了更方便的實(shí)現(xiàn)彈性的資源創(chuàng)建,方便用戶一次運(yùn)行多臺(tái)ECS按量實(shí)例來完成應(yīng)用的開發(fā)和部署,阿里云開放了ECS的批量創(chuàng)建實(shí)例接口RunInstances,可以單次最多創(chuàng)建100臺(tái)實(shí)例,避免重復(fù)

2018-03-05 17:40:04

隨著片上系統(tǒng)SOC設(shè)計(jì)技術(shù)與大規(guī)模可編程邏輯器件的發(fā)展,嵌人式處理器在可編程器件卜的實(shí)現(xiàn)得到了廣泛的應(yīng)用介紹了一款基于Virt-111 XC2V3001〕的星載可重構(gòu)計(jì)算機(jī)硬件驗(yàn)證平臺(tái)的

2009-03-14 18:18:35 31

31 VMM驗(yàn)證方法在AXI總線系統(tǒng)中的實(shí)現(xiàn):本文基于中科院計(jì)算所某項(xiàng)目實(shí)際工作,介紹如何利用高級驗(yàn)證語言、驗(yàn)證基本庫、以及成熟的驗(yàn)證模型,快速建立可隨機(jī)產(chǎn)生測試向量、向量場

2009-12-14 09:26:55 32

32 Open Verification Methodology(OVM)是Mentor Graphics 和Cadence 共同推出的,業(yè)界第一個(gè)基于SystemVerilog、通用開放的驗(yàn)證方法學(xué);其基于事務(wù)交易級的方法學(xué),基于Factory Pattern 的對象生

2010-07-04 11:43:22 7

7 無線溫度驗(yàn)證系統(tǒng) 溫度壓力一體 溫度驗(yàn)證儀分有線系統(tǒng)與無線系統(tǒng)。有線的溫度驗(yàn)證系統(tǒng)精度低,價(jià)格相對于無線產(chǎn)品的價(jià)格要低廉的多,無線驗(yàn)證系統(tǒng)操作方便,節(jié)省時(shí)間,而有線布線特別麻煩。所以在某些全封閉

2023-12-20 10:10:23

包括 7.5 cm 空心線、步進(jìn)阻抗空心線以及 20 dB 和 40 dB 衰減器特點(diǎn)85053B 驗(yàn)證套件配備一個(gè) 3.5 mm 連接器,可覆蓋的頻率范圍為 300 kHz 至 26.5 GHz

2024-09-14 09:44:21

隨著深亞微米工藝技術(shù)日益成熟,基于IP復(fù)用的IC設(shè)計(jì)方法廣泛采用,集成電路芯片的規(guī)模越來越大,這對集成電路驗(yàn)證技術(shù)和方法學(xué)提出了很大的挑戰(zhàn)。就如芯片

2009-04-04 10:58:40 2084

2084

摘要:本應(yīng)用筆記簡I²C總線的驗(yàn)證及實(shí)現(xiàn)單回顧了I²C總線的發(fā)展進(jìn)程,并介紹了I²C配置,以簡化總線上主機(jī)與從機(jī)之間的通信。應(yīng)用實(shí)例提供了原理圖和程序代碼,附錄1

2009-04-23 15:59:05 2141

2141

摘要:本應(yīng)用筆記簡I²C總線的驗(yàn)證及實(shí)現(xiàn)單回顧了I²C總線的發(fā)展進(jìn)程,并介紹了I²C配置,以簡化總線上主機(jī)與從機(jī)之間的通信。應(yīng)用實(shí)例提供了原理圖和程序代碼,附錄1

2009-04-28 10:09:14 1102

1102

設(shè)計(jì)與驗(yàn)證復(fù)雜SoC中可綜合的模擬及射頻模型

設(shè)計(jì)用于SoC集成的復(fù)雜模擬及射頻模塊是一項(xiàng)艱巨任務(wù)。本文介紹的采用基于性能指標(biāo)規(guī)格來優(yōu)化設(shè)計(jì)(如PLL或ADC等)的方

2009-12-26 14:38:13 802

802

摘要:文中詳述了FPGA被動(dòng)串行配置方式的時(shí)序,給出配置流程圖及實(shí)現(xiàn)的程序代碼,并通過實(shí)例驗(yàn)證了該方法的優(yōu)越

2010-07-21 14:48:48 1692

1692

針對數(shù)字信號處理器的不同仿真和驗(yàn)證要求,提出了一種可測性軟硬件協(xié)同仿真和驗(yàn)證平臺(tái)的設(shè)計(jì). 采用可配置IP 模塊和總線結(jié)構(gòu),實(shí)現(xiàn)了硬件平臺(tái)可配置性和可重用性;采用在線仿真模塊

2011-06-09 17:54:21 39

39 基于驗(yàn)證方法手冊(VMM)的驗(yàn)證是行之有效的模塊級驗(yàn)證環(huán)境實(shí)現(xiàn)方法。在系統(tǒng)級利用模塊級驗(yàn)證組件可顯著改善驗(yàn)證質(zhì)量,縮短滿足系統(tǒng)級覆蓋率所需的時(shí)間。系統(tǒng)級測試平臺(tái)帶來了一

2011-10-09 16:27:14 0

0 以創(chuàng)建6位D/A轉(zhuǎn)換器和TTL7458原理圖模型為例,論述創(chuàng)建Proteus原理圖仿真模型的思路與方法、模型存庫與從庫中調(diào)用他的方法和對創(chuàng)建模型進(jìn)行驗(yàn)證的方法。經(jīng)驗(yàn)證證明所建模型和建模方

2012-03-28 15:10:25 95

95 本文介紹全球首款支持UCPS標(biāo)準(zhǔn)、符合HDMI1.3標(biāo)準(zhǔn)的發(fā)送器SHC3201,并探討UCPS協(xié)議與HDMI的驗(yàn)證系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)。

2012-04-09 11:32:37 2543

2543

電子發(fā)燒友網(wǎng)核心提示 :Cadence Allegro通過使用Microsoft SharePoint的高效協(xié)作ECAD環(huán)境加速產(chǎn)品創(chuàng)建。Allegro 16.6 版本促進(jìn)時(shí)序敏感型物理實(shí)現(xiàn)與驗(yàn)證,將高速界面的時(shí)序閉合加快了30-50% 電子

2012-10-11 10:18:58 1572

1572 本文介紹了一種使用軟件作為激勵(lì)以加速系統(tǒng)級驗(yàn)證的方法。使用的激勵(lì)是切合實(shí)際的,并易于快速創(chuàng)建。對設(shè)計(jì)執(zhí)行此激勵(lì)可及早揭露問題,否則,這些問題可能要等到創(chuàng)建虛擬原型

2013-01-04 14:51:44 2015

2015 在系統(tǒng)芯片的設(shè)計(jì)中,傳統(tǒng)的激勵(lì)發(fā)生機(jī)制耗費(fèi)人工多且難以重用,嚴(yán)重影響了仿真驗(yàn)證的效率。針對此問題,構(gòu)建了一種基于可重用激勵(lì)發(fā)生機(jī)制的虛擬SoC驗(yàn)證平臺(tái)。該平臺(tái)利用可重用的激勵(lì)發(fā)生模塊調(diào)用端口激勵(lì)文件

2017-11-28 17:43:39 0

0 jquery ajax實(shí)例代碼:基于jQuery實(shí)現(xiàn)的Ajax 驗(yàn)證用戶名唯一性實(shí)例代碼;jQuery+AJAX實(shí)現(xiàn)遮罩層登錄驗(yàn)證界面(附源碼)。非常不錯(cuò),具有參考借鑒價(jià)值,需要的的朋友參考下吧

2017-12-03 09:42:39 4877

4877

采用System Verilog語言設(shè)計(jì)了一種具有層次化結(jié)構(gòu)的可重用驗(yàn)證平臺(tái),該平臺(tái)能夠產(chǎn)生各種隨機(jī)、定向、錯(cuò)誤測試向量,并提供功能覆蓋率計(jì)算。將驗(yàn)證平臺(tái)在Synopsys公司的VCS仿真工具上運(yùn)行

2018-01-12 11:28:24 3225

3225

消除復(fù)雜網(wǎng)絡(luò) SoC 開發(fā)風(fēng)險(xiǎn)不再是遙遠(yuǎn)的目標(biāo);如今,所有設(shè)計(jì)團(tuán)隊(duì)都可以實(shí)現(xiàn)。 最近,筆者一直在寫關(guān)于在芯片流片成功之前使用硬件加速仿真來驗(yàn)證網(wǎng)絡(luò)片上系統(tǒng) (SoC) 設(shè)計(jì)的益處的系列文章。在本專欄

2018-02-02 15:17:01 1569

1569

為了充分利用系統(tǒng)級芯片(SoC)設(shè)計(jì)帶來的優(yōu)點(diǎn),業(yè)界需要一種可以擴(kuò)展的驗(yàn)證解決方案,解決設(shè)計(jì)周期中各個(gè)階段的問題,縮短驗(yàn)證鴻溝。本文將探討可擴(kuò)展驗(yàn)證解決方案為何能夠以及如何解決SoC設(shè)計(jì)目前面臨的功能方面的嚴(yán)峻挑戰(zhàn),以達(dá)到提高設(shè)計(jì)生產(chǎn)力、保證設(shè)計(jì)質(zhì)量、縮短產(chǎn)品上市時(shí)間以及提高投資回報(bào)率的目的。

2018-06-04 03:13:00 1260

1260

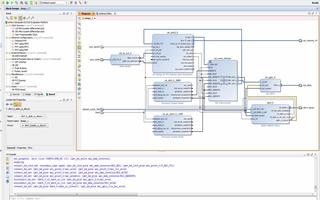

本文是基于FPGA實(shí)現(xiàn)Cordic算法的設(shè)計(jì)與驗(yàn)證,使用Verilog HDL設(shè)計(jì),初步可實(shí)現(xiàn)正弦、余弦、反正切函數(shù)的實(shí)現(xiàn)。將復(fù)雜的運(yùn)算轉(zhuǎn)化成FPGA擅長的加減法和乘法,而乘法運(yùn)算可以用移位運(yùn)算代替

2018-07-03 10:18:00 3415

3415

《C語言接口與實(shí)現(xiàn):創(chuàng)建可重用軟件的技術(shù)》概念清晰、實(shí)例詳盡,是一本有關(guān)設(shè)計(jì)、實(shí)現(xiàn)和有效使用C語言庫函數(shù),掌握創(chuàng)建可重用C語言軟件模塊技術(shù)的參考指南。書中提供了大量實(shí)例,重在闡述如何用一種與語言無關(guān)的方法將接口設(shè)計(jì)實(shí)現(xiàn)獨(dú)立出來,從而用一種基于接口的設(shè)計(jì)途徑創(chuàng)建可重用的API。

2018-08-27 08:00:00 33

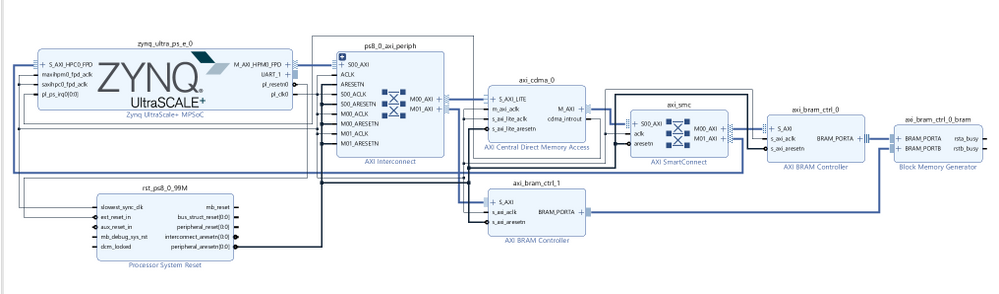

33 了解如何使用Vivado的創(chuàng)建和封裝IP功能創(chuàng)建可添加自定義邏輯的AXI外設(shè),以創(chuàng)建自定義IP。

2018-11-29 06:48:00 7675

7675

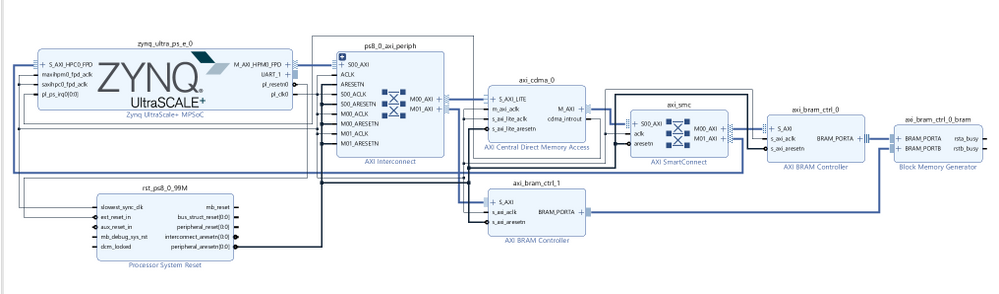

本視頻介紹了使用IP Integrator(IPI)創(chuàng)建簡單硬件設(shè)計(jì)的過程。

使用IPI可以無縫,快速地實(shí)現(xiàn)DDR4和PCIe等塊

連接在一起,在幾分鐘內(nèi)創(chuàng)建硬件設(shè)計(jì)。

2018-11-22 06:13:00 5012

5012

很多網(wǎng)站登錄都需要輸入驗(yàn)證碼,如果要實(shí)現(xiàn)自動(dòng)登錄就不可避免的要識別驗(yàn)證碼。本文以一個(gè)真實(shí)網(wǎng)站的驗(yàn)證碼為例,實(shí)現(xiàn)了基于一下KNN的驗(yàn)證碼識別。

2018-12-24 17:27:22 8489

8489 Signal Chain Designer?是先進(jìn)的選型和設(shè)計(jì)環(huán)境,可用于創(chuàng)建定制設(shè)計(jì),并直接交互訪問200多個(gè)經(jīng)過測試的應(yīng)用電路和經(jīng)驗(yàn)證的產(chǎn)品組合。

2019-08-02 06:05:00 2322

2322 墊標(biāo)準(zhǔn)+和墊專業(yè)使用的強(qiáng)大和易于使用的約束管理系統(tǒng)創(chuàng)建、評審和驗(yàn)證PCB設(shè)計(jì)約束。

2019-11-04 07:02:00 2444

2444 使用墊子集成項(xiàng)目快速、簡單,自動(dòng)創(chuàng)建差分對。觀察墊創(chuàng)建50雙在不到30秒!

2019-10-16 07:02:00 2527

2527 Raconteur 今天發(fā)布的一份信息圖探討了物聯(lián)網(wǎng)(IoT)如何成為創(chuàng)建更高效、可持續(xù)和更具彈性的城市的重要技術(shù),并說明了物聯(lián)網(wǎng)將對人類和地球產(chǎn)生越來越大的影響。

2020-02-27 14:50:22 2129

2129 《C語言接口與實(shí)現(xiàn):創(chuàng)建可重用軟件的技術(shù)》概念清晰、實(shí)例詳盡,是一本有關(guān)設(shè)計(jì)、實(shí)現(xiàn)和有效使用C語言庫函數(shù),掌握創(chuàng)建可重用C語言軟件模塊技術(shù)的參考指南。書中提供了大量實(shí)例,重在闡述如何用一種與語言無關(guān)的方法將接口設(shè)計(jì)實(shí)現(xiàn)獨(dú)立出來,從而用一種基于接口的設(shè)計(jì)途徑創(chuàng)建可重用的API。

2020-05-11 08:00:00 22

22 本篇博文將為您演示如何創(chuàng)建 AXI CDMA Linux 用戶空間示例應(yīng)用。 示例設(shè)計(jì)將在 Zynq UltraScale+ RFSoC ZCU111 評估板上實(shí)現(xiàn)通過 AXI CDMA 把數(shù)據(jù)從

2020-09-28 15:31:06 3090

3090

為了快速實(shí)現(xiàn)算法板級驗(yàn)證,PC端需要通過JTAG或以太網(wǎng)與FPGA形成通路。最簡單便捷的方案是利用協(xié)議棧芯片,用戶可以無視底層,利用簡單的SPI協(xié)議讀寫寄存器實(shí)現(xiàn)復(fù)雜的TCP UDP等網(wǎng)絡(luò)協(xié)議。當(dāng)然

2020-12-25 17:22:19 2776

2776 XSA 以及如何創(chuàng)建在目標(biāo)平臺(tái)上實(shí)現(xiàn)設(shè)計(jì)加速所需的軟件鏡像。 熟悉 OpenCL 的用戶可能對內(nèi)核 (kernel)一詞已耳熟能詳,在 OpenCL 中執(zhí)行功能的位置即被稱為內(nèi)核。 在 Vitis

2020-10-26 15:48:00 1967

1967

第二章 驗(yàn)證flow驗(yàn)證的Roadmap驗(yàn)證的目標(biāo)UVM驗(yàn)證方法學(xué)ASIC驗(yàn)證分解驗(yàn)證策略和任務(wù)的分解AMBA可重用、靈活性、兼容性、廣泛支持一.驗(yàn)證的Roadmap1.ASIC芯片項(xiàng)目流程市場需求

2021-10-25 12:36:01 24

24 ?? 基于安卓平臺(tái)的滑動(dòng)拼圖驗(yàn)證組件 SwipeCaptcha,實(shí)現(xiàn)了鴻蒙化遷移和重構(gòu),代碼已經(jīng)開源,目前已經(jīng)獲得了很多人的 Star 和 Fork ,歡迎各位下載使用并提出寶貴意見

2021-11-01 14:23:18 2394

2394 在STM32上創(chuàng)建鏈表并實(shí)現(xiàn)LCD滾動(dòng)顯示串口消息

2021-12-06 19:21:05 18

18 在爬蟲訪問目標(biāo)網(wǎng)站的過程中,很多網(wǎng)站為了避免被惡意訪問,需要設(shè)置驗(yàn)證碼登錄,這樣是為了避免非人類的訪問。今天我們學(xué)習(xí)下如何使用Python爬蟲實(shí)現(xiàn)驗(yàn)證碼登錄并且將生成的驗(yàn)證碼保存下來,然后人為輸入后

2021-12-11 15:27:15 2888

2888 歷時(shí)4月,可支持18億門SoC全芯片驗(yàn)證的英諾達(dá)硬件驗(yàn)證云平臺(tái)成都中心一期成功實(shí)現(xiàn)滿載運(yùn)行,圓滿達(dá)成云平臺(tái)一期運(yùn)營所有目標(biāo)!英諾達(dá)的云平臺(tái),不同于傳統(tǒng)的IDC機(jī)房,機(jī)器要求高、運(yùn)營復(fù)雜、專業(yè)要求極高

2021-12-17 13:54:49 2703

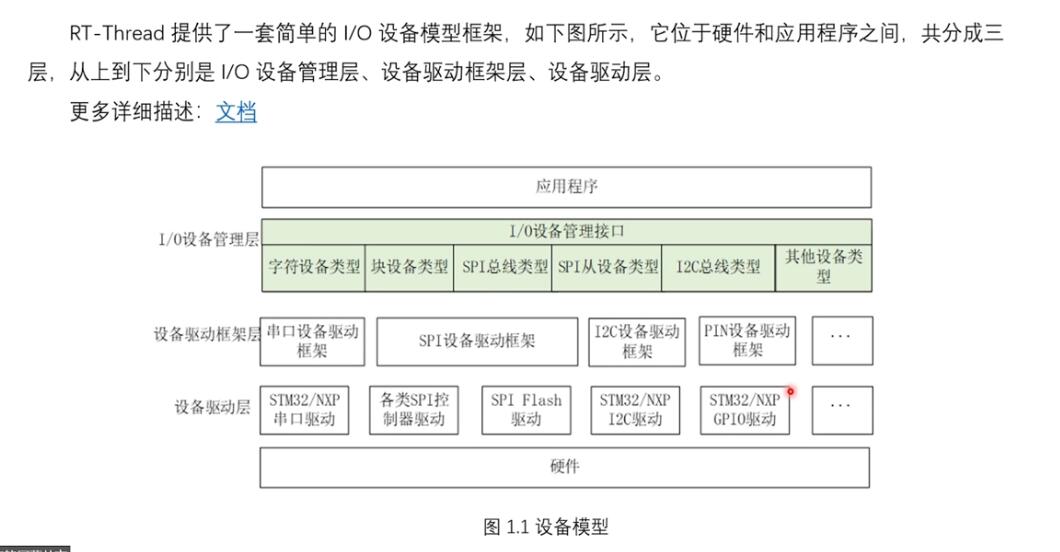

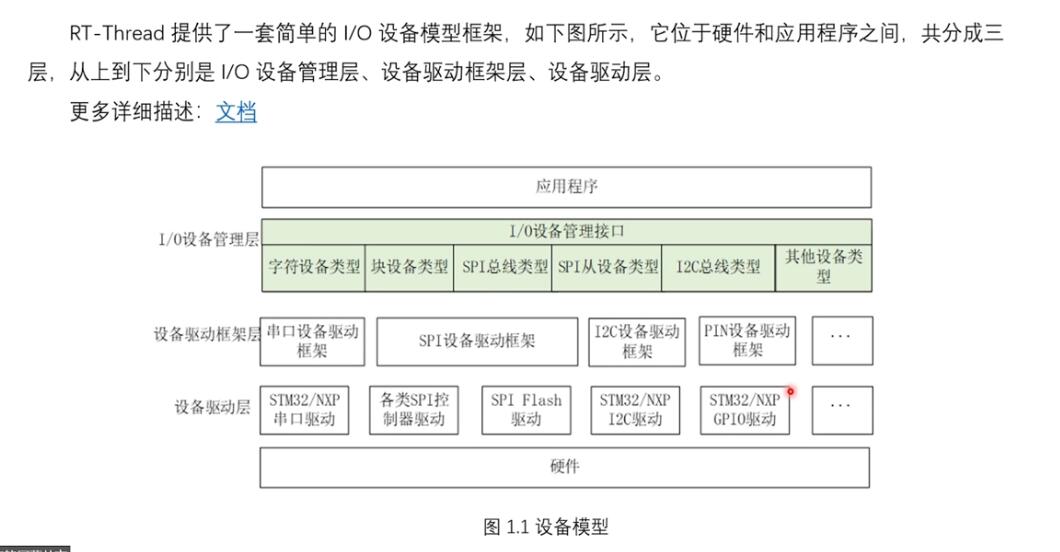

2703 RT-Thread設(shè)備模型框架及創(chuàng)建注冊設(shè)備的實(shí)現(xiàn)方式介紹如下:

2022-05-28 10:38:06 2663

2663

SYCLomatic開放開發(fā),使開發(fā)者自由創(chuàng)建可遷移的異構(gòu)代碼。

2022-05-30 16:49:09 1235

1235 虛擬數(shù)字機(jī)器人仿真測試驗(yàn)證平臺(tái),真正提供機(jī)器人控制器檢測、驗(yàn)證平臺(tái),可檢測各類工業(yè)機(jī)器人控制器的功能、性能指標(biāo),允許基于EtherCAT總線的機(jī)器人控制器連接,仿真硬件可實(shí)時(shí)吞吐仿真數(shù)據(jù),實(shí)現(xiàn)ms級的檢測、驗(yàn)證。

2022-08-31 20:39:09 2244

2244

Pdfium.NetSDK 是領(lǐng)先的.Net庫,用于生成、操作和查看可移植文檔格式的文件。我們提供高級c#/ VB.Net API,用于在WEB服務(wù)器或任何其他服務(wù)器系統(tǒng)上創(chuàng)建動(dòng)態(tài)pdf,并在現(xiàn)有桌面或WEB應(yīng)用程序中實(shí)現(xiàn)“另存為PDF”功能。

2022-09-06 09:21:39 2819

2819 和其他一些應(yīng)用中的驗(yàn)證和跟蹤提供了一種低成本、空間敏感的解決方案。它還可以為外部數(shù)據(jù)加密/解密提供密鑰以確保安全。使用單線存儲(chǔ)設(shè)備,可以在新的或更新的設(shè)計(jì)中輕松實(shí)現(xiàn)驗(yàn)證和跟蹤。

2022-11-18 14:54:46 1013

1013 表單級或控制級驗(yàn)證、完全可自定義和本地化的錯(cuò)誤消息、正則表達(dá)式驗(yàn)證(包括許多)、正則表達(dá)式測試儀、各種驗(yàn)證運(yùn)算符和選項(xiàng),等等。

2022-11-22 09:59:50 761

761 電子發(fā)燒友網(wǎng)站提供《如何為Minized創(chuàng)建可工作的PYNQ系統(tǒng).zip》資料免費(fèi)下載

2022-12-14 10:46:02 1

1 微控制器中的不可變啟動(dòng)存儲(chǔ)器是任何通過安全啟動(dòng)和安全固件升級實(shí)現(xiàn)固件驗(yàn)證的應(yīng)用中非常重要的功能。最新的PIC24F低功耗微控制器(MCU)和高性能dsPIC33數(shù)字信號控制器(DSC)具有ICSP?寫禁止和CodeGuard? Security的閃存OTP,可實(shí)現(xiàn)不可變的安全啟動(dòng)。

2023-05-06 10:28:58 1679

1679

一. 基礎(chǔ)概念 Java中,一般我們創(chuàng)建一個(gè)對象可能會(huì)選擇new一下個(gè)實(shí)例。但是隨著我們技術(shù)的不斷提升,我們也學(xué)習(xí)到了,可以通過反射技術(shù)實(shí)現(xiàn)對象的創(chuàng)建。 可是,你有沒有想一下,什么時(shí)候我們改用new

2023-05-22 14:25:47 2822

2822

uvm environment 類是一個(gè)包含多個(gè)可重用的驗(yàn)證組件的類,它定義了測試用例所需的驗(yàn)證組件的配置。

2023-06-04 16:28:52 926

926

驗(yàn)證環(huán)境用戶需要創(chuàng)建許多測試用例來驗(yàn)證一個(gè)DUT的功能是否正確,驗(yàn)證環(huán)境開發(fā)者應(yīng)該通過以下方式提高測試用例的開發(fā)效率

2023-06-09 11:11:22 1603

1603

本文介紹了從一組可重用的驗(yàn)證組件中構(gòu)建測試平臺(tái)所需的步驟。UVM促進(jìn)了重用,加速了測試平臺(tái)構(gòu)建的過程。

2023-06-13 09:11:11 1090

1090

writer ) 進(jìn)行區(qū)分,前者負(fù)責(zé)測試平臺(tái)的構(gòu)建和配置,后者可能對測試平臺(tái)的底層了解較少,但用它來創(chuàng)建測試用例。 基于驗(yàn)證組件創(chuàng)建測試平臺(tái)的步驟是:? Review可重用的驗(yàn)證組件配置參數(shù)。? 實(shí)例化和配置驗(yàn)證組件。? 為接口驗(yàn)證組件創(chuàng)建可重用的sequences(可選)。? 添加一

2023-06-13 09:14:23 1316

1316

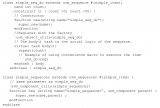

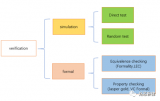

相信很多人已經(jīng)接觸過驗(yàn)證。如我以前有篇文章所寫驗(yàn)證分為IP驗(yàn)證,F(xiàn)PGA驗(yàn)證,SOC驗(yàn)證和CPU驗(yàn)證,這其中大部分是采用動(dòng)態(tài)仿真(dynamic simulation)實(shí)現(xiàn),即通過給定設(shè)計(jì)(design)端口測試激勵(lì),結(jié)合時(shí)間消耗判斷設(shè)計(jì)的輸出結(jié)果是否符合預(yù)期。

2023-07-21 09:53:24 14321

14321

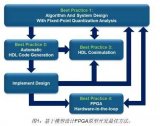

芯片設(shè)計(jì)和驗(yàn)證工程師通常要為在硅片上實(shí)現(xiàn)的每一行RTL代碼寫出多達(dá)10行測試平臺(tái)代碼。驗(yàn)證任務(wù)在設(shè)計(jì)周期內(nèi)可能會(huì)占用50%或更多的時(shí)間。盡管如此辛 苦,仍有接近60%的芯片存在功能瑕疵,需要返工。由于HDL仿真不足以發(fā)現(xiàn)系統(tǒng)級錯(cuò)誤,芯片設(shè)計(jì)人員正利用FPGA來加速算法創(chuàng)建和原型設(shè)計(jì)。

2023-08-06 10:49:09 2904

2904

,步驟如下 注:工作空間名字可任取,將下面語句中的motionplanning_ws改為任取的名字即可 (1)創(chuàng)建工作空間 在終端依次執(zhí)行以下三條語句創(chuàng)建名為

2023-11-26 17:09:04 2122

2122

生態(tài)系統(tǒng)和定制指令集開發(fā)的唯一途徑。 當(dāng)下,芯片企業(yè)正在設(shè)計(jì) RISC-V 人工智能 (AI) 與機(jī)器學(xué)習(xí) (ML) 定制加速器,以實(shí)現(xiàn)特定工作負(fù)載的加速處理,這些企業(yè)創(chuàng)建的架構(gòu)由軟件驅(qū)動(dòng),而不使用遺留數(shù)據(jù)或任何通用數(shù)據(jù)。而是,針對軟件工作負(fù)載應(yīng)用在架構(gòu)層面進(jìn)行量身定制。

2025-05-13 18:21:19 1775

1775 0 1 ? 簡介?? SoC 設(shè)計(jì)團(tuán)隊(duì)的任務(wù)是在創(chuàng)建昂貴的生產(chǎn)掩膜之前完成完整的系統(tǒng)級驗(yàn)證。這意味著徹底審核所有硬件模塊、這些模塊之間的所有交互以及為最終應(yīng)用創(chuàng)建的所有專用軟件,而且所有這些任務(wù)都要

2025-06-12 14:39:36 1265

1265

近日,在聯(lián)合國日內(nèi)瓦萬國宮成功舉辦的“創(chuàng)建可持續(xù)商業(yè)與品牌”高級別對話會(huì)上,由中國標(biāo)準(zhǔn)化協(xié)會(huì)可持續(xù)商業(yè)與品牌工作委員會(huì)(SBBC)等發(fā)起的“創(chuàng)建可持續(xù)品牌”愿景倡議正式發(fā)布。AAC瑞聲科技(下文簡稱:AAC)首批簽署該倡議,向全球展示了中國領(lǐng)先企業(yè)以更高標(biāo)準(zhǔn)、更大雄心踐行可持續(xù)發(fā)展的決心。

2025-09-19 11:42:00 789

789

電子發(fā)燒友App

電子發(fā)燒友App

評論