本視頻介紹了使用IP Integrator(IPI)創(chuàng)建簡(jiǎn)單硬件設(shè)計(jì)的過(guò)程。 使用IPI可以無(wú)縫,快速地實(shí)現(xiàn)DDR4和PCIe等塊 連接在一起,在幾分鐘內(nèi)創(chuàng)建硬件設(shè)計(jì)。

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

賽靈思

+關(guān)注

關(guān)注

33文章

1798瀏覽量

133425 -

IP

+關(guān)注

關(guān)注

5文章

1862瀏覽量

155829 -

PCIe

+關(guān)注

關(guān)注

16文章

1460瀏覽量

88402

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

如何使用蘇培Ethernet/IP總線網(wǎng)關(guān)與匯川AM400系列PLC通訊

Ethernet/IP是一個(gè)面向工業(yè)自動(dòng)化應(yīng)用的工業(yè)應(yīng)用層協(xié)議。它建立在標(biāo)準(zhǔn)UDP/IP與TCP/IP協(xié)議之上,利用固定的以太網(wǎng)硬件和軟件,為配置、訪問(wèn)和控制工業(yè)自動(dòng)化設(shè)備定義了一個(gè)應(yīng)

RDMA設(shè)計(jì)6:IP架構(gòu)2

專(zhuān)注高性能存儲(chǔ)與傳輸,在本博客已給出相關(guān)博文已約80篇,希望對(duì)初學(xué)者有用。注意這里只是拋磚引玉,切莫認(rèn)為參考這就可以完成商用IP設(shè)計(jì)。IP結(jié)構(gòu)圖融合以太網(wǎng)協(xié)議棧是實(shí)現(xiàn) RoCE v2 命令提交和完成

發(fā)表于 11-26 10:24

復(fù)雜的軟件算法硬件IP核的實(shí)現(xiàn)

硬件加速 IP 核 HDL 文件的生成分為兩個(gè)步驟,首先根據(jù)將要接入的 SOPC 系統(tǒng)的總線的特性,將算法做適當(dāng)?shù)陌b、暴露相關(guān)的接口以及調(diào)用方法,即適配總線接口。不同的 SOPC 總線有不同的時(shí)序以及

發(fā)表于 10-30 07:02

蜂鳥(niǎo)E203硬件集成步驟

今天主要介紹一下我們團(tuán)隊(duì)怎么把硬件集成于蜂鳥(niǎo)E203上。

1、sm2 IP設(shè)計(jì)。

2、slave設(shè)計(jì),將sm2 IP連接到總線上,與總線的通信使用自定義ICB協(xié)議,與sm2通信使用sm2自定義協(xié)議

發(fā)表于 10-30 06:52

安防硬件設(shè)備中的防水防塵IP等級(jí)代表什么?IP66是什么水平

我們?cè)谶x擇安防硬件廠家的產(chǎn)品時(shí),在規(guī)格表或產(chǎn)品詳情頁(yè)中常常會(huì)看到一個(gè)防護(hù)等級(jí)的指標(biāo),有的是IP65.有的是IP66等級(jí),這些安防設(shè)備產(chǎn)品的IP等級(jí)高低又分別代表什么呢?下面讓天波小編為

AMD Vivado IP integrator的基本功能特性

我們還將帶您了解在 AMD Zynq UltraScale+ MPSoC 開(kāi)發(fā)板與 AMD Versal 自適應(yīng) SoC 開(kāi)發(fā)板上使用 IP integrator 時(shí),兩種設(shè)計(jì)流程之間存在的差異。

請(qǐng)問(wèn)InConnect 是否可以用實(shí)際 IP 而不是用虛擬 IP 映射實(shí)際IP ?

但是這樣子使用的話,我只能通過(guò)這個(gè)虛擬IP來(lái)連接設(shè)備,那樣子我的PLC編程軟件就不能連接上設(shè)備了因?yàn)?b class='flag-5'>IP和實(shí)際的不一樣,我能通過(guò)什么辦法來(lái)讓映射出來(lái)的虛擬IP和我的實(shí)際設(shè)備IP一致嗎?

發(fā)表于 08-06 07:54

FPGA利用DMA IP核實(shí)現(xiàn)ADC數(shù)據(jù)采集

DMA IP核來(lái)實(shí)現(xiàn)高效數(shù)據(jù)傳輸?shù)牟襟E,包括創(chuàng)建項(xiàng)目、配置ADC接口、添加和連接DMA IP核、設(shè)計(jì)控制邏輯、生成比特流、軟件開(kāi)發(fā)及系統(tǒng)集成。文章還強(qiáng)調(diào)了系統(tǒng)實(shí)現(xiàn)中不可或缺的ip_re

MicroBlaze處理器嵌入式設(shè)計(jì)用戶指南

*本指南內(nèi)容涵蓋了在嵌入式設(shè)計(jì)中使用 MicroBlaze 處理器、含存儲(chǔ)器 IP 核的設(shè)計(jì)、IP integrator 中的復(fù)位和時(shí)鐘拓?fù)浣Y(jié)構(gòu)。獲取完整版《 MicroBlaze 處理器嵌入式設(shè)計(jì)用戶指南》,請(qǐng)至文末掃描二維碼

如何在Unified IDE中創(chuàng)建視覺(jué)庫(kù)HLS組件

Vivado IP 流程(Vitis Unified),在這篇 AMD Vitis HLS 系列 3 中,我們將介紹如何使用 Unified IDE 創(chuàng)建 HLS 組件。這里采用“自下而上”的流程,從 HLS

如何使用AMD Vitis HLS創(chuàng)建HLS IP

本文逐步演示了如何使用 AMD Vitis HLS 來(lái)創(chuàng)建一個(gè) HLS IP,通過(guò) AXI4 接口從存儲(chǔ)器讀取數(shù)據(jù)、執(zhí)行簡(jiǎn)單的數(shù)學(xué)運(yùn)算,然后將數(shù)據(jù)寫(xiě)回存儲(chǔ)器。接著會(huì)在 AMD Vivado Design Suite 設(shè)計(jì)中使用此 HLS

Xilinx Shift RAM IP概述和主要功能

Xilinx Shift RAM IP 是 AMD Xilinx 提供的一個(gè) LogiCORE IP 核,用于在 FPGA 中實(shí)現(xiàn)高效的移位寄存器(Shift Register)。該 IP 核利用

基于8051 IP調(diào)試器設(shè)計(jì)方案

8051 IP調(diào)試器是一種對(duì)基于8051指令系統(tǒng)的IP核進(jìn)行調(diào)試的軟硬件結(jié)合工具,需要與集成開(kāi)發(fā)環(huán)境(IDE)結(jié)合使用。

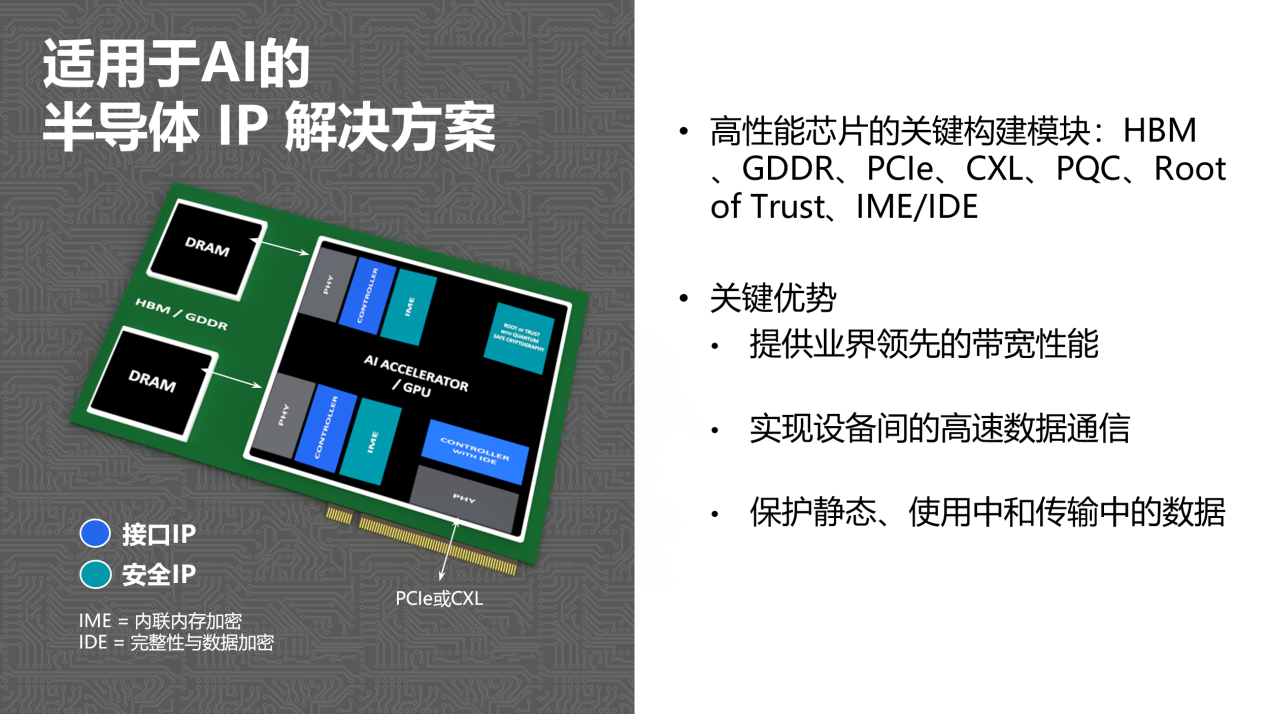

AI應(yīng)用激增,硬件安全防護(hù)更關(guān)鍵,Rambus 發(fā)布CryptoManager安全IP解決方案

知名半導(dǎo)體IP和芯片供應(yīng)商Rambus以創(chuàng)新為基礎(chǔ)打造三大半導(dǎo)體解決方案,包括基礎(chǔ)技術(shù)、半導(dǎo)體IP和芯片。基礎(chǔ)技術(shù)方面,35年以來(lái)公司開(kāi)發(fā)了約2700項(xiàng)專(zhuān)利。半導(dǎo)體IP方面,提供接口IP

RT-Thread Ethernet/IP 協(xié)議技術(shù)實(shí)踐|技術(shù)集結(jié)

工業(yè)設(shè)備之間的實(shí)時(shí)通信。由于Ethernet/IP兼容現(xiàn)有的以太網(wǎng)硬件和網(wǎng)絡(luò),企業(yè)能夠在不需要專(zhuān)用硬件的情況下,實(shí)現(xiàn)工業(yè)設(shè)備間的互聯(lián)互通,提升生產(chǎn)效率和系統(tǒng)可靠性

如何使用IP Integrator創(chuàng)建硬件設(shè)計(jì)

如何使用IP Integrator創(chuàng)建硬件設(shè)計(jì)

評(píng)論