緩沖集成項目是快速,簡單和自動創建差分對。在不到30秒的時間內,觀察板可以創建50對!

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

緩沖

+關注

關注

0文章

53瀏覽量

18231 -

自動

+關注

關注

0文章

121瀏覽量

26702

發布評論請先 登錄

相關推薦

熱點推薦

LT1010:快速功率緩沖器的卓越性能與多樣應用

Technology Corporation推出的LT1010,這是一款快速的單位增益緩沖器,能顯著提升現有IC運算放大器的輸出能力。 文件下載: LT1010.pdf 一、產品概述 (一)功能與優勢 LT1010是一款快速的

小藝開放平臺快速創建鴻蒙智能體

與預覽工具體驗當前智能體的實際效果,來幫助我們進行智能體的問題定位和優化改進。

創建智能體時,開場對話可以讓用戶快速了解你的智能體功能或場景設定故事背景,預置問題可以讓用戶通過點擊快速體驗智能體的能力,角色指令(prompt)直

發表于 01-19 11:00

LTC6417:高性能差分緩沖器的深度剖析與應用探索

LTC6417:高性能差分緩沖器的深度剖析與應用探索 在高速信號處理和數據采集系統中,一款性能卓越的差分緩沖器能夠顯著提升系統的整體性能。今天,我們就來深入探討凌力爾特(現屬亞德諾半導

探索DS15BA101:高速差分緩沖器的卓越之選

探索DS15BA101:高速差分緩沖器的卓越之選 在電子設計領域,高速信號處理與傳輸始終是一項極具挑戰性的任務。高速差分緩沖器作為保障信號在傳輸過程中保持高完整性和穩定性的關鍵組件,其

高速信號處理的利器:DS30BA101差分緩沖器深度解析

高速信號處理的利器:DS30BA101差分緩沖器深度解析 在高速信號處理領域,一款性能卓越的緩沖器對于確保信號的完整性和穩定性至關重要。今天,我們就來深入探討德州儀器(TI)推出的DS30BA101

高速信號處理利器:DS15BA101 1.5 Gbps 差分緩沖器解析

高速信號處理利器:DS15BA101 1.5 Gbps 差分緩沖器解析 在電子工程師的日常設計中,高速數據傳輸和信號處理是繞不開的話題。今天,我們就來深入探討一款功能強大的高速差分緩沖

技術資訊 I 圖文詳解約束管理器-差分對規則約束

本文要點你是否經常在Layout設計中抓瞎,拿著板子無從下手,拿著鼠標深夜狂按;DDR等長沒做好導致系統不穩定,PCIe沒設相位容差造成鏈路訓練失敗……這些都是血淚教訓,關鍵時刻需要靠約束管理器救命

是否可以僅使用 Bootloader Host 來實現可引導加載項目的相同編程結果?

你好

我想使用 Bootloader Host 在我的 CY8CKIT-059 上對 CY8C5888LTI-LP097 芯片進行編程,并將項目類型設置為可引導加載。我的目標是實現與通過使用 SWD

發表于 07-18 07:39

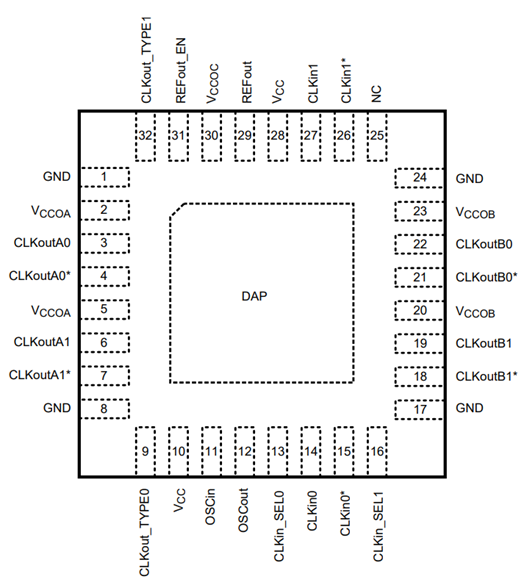

HAC00304QN型低抖動差分時鐘緩沖器發布

輸出,兩個差分輸出組可配置為 LVPECL、LVDS或HCSL驅動器,也可被禁用。LVCMOS 輸出具有用于在啟用或禁用時實現無短脈沖運行的同步使能輸入。如果未選擇晶體輸入,內部振蕩器電路會自動禁用

為CYBT-253059-2創建IAR項目時出錯了,怎么解決?

你好,我們目前正在開發一個基于 CYBT-253059-2 模塊的新應用程序,并且已經可以使用“eclipse”進行一些測試。

我們必須使用 IAR,因此我嘗試使用項目創建器創建一個新項目

發表于 06-30 08:19

降壓式電路的緩沖電路原理和快速設計

摘要

本應用報告首先給出了降壓式開關電路(buck)在上管開通瞬間的的一個等效諧振回路模型。根據該模型推導出使得開關振鈴最小化的阻容緩沖電路(snubber)的參數計算公式,并結合參數公式給出

發表于 06-05 14:27

Allegro Skill布線功能-添加差分過孔禁布區

在高速PCB設計中,差分過孔之間設置禁止布線區域具有重要意義。首先它能有效減少其他信號線對差分信號的串擾,保持差分對的信號完整性。其次禁止布線區域有助于維持

發表于 05-28 15:19

?1061次閱讀

FreeRTOS進階使用之流緩沖區:高效處理字節流的秘密武器

工具,通過合理設置觸發閾值和緩沖區大小,可顯著提升系統性能。實際開發中需注意多核同步、阻塞策略及數據格式設計,必要時結合消息緩沖區實現更復雜的通信需求。掌握這一機制,將助你在嵌入式開發

發表于 03-24 11:37

LTC6416 2GHz、低噪聲、差分16位ADC緩沖器技術手冊

LTC6416 是一款差分單位增益緩沖器,專為以極低的輸出噪聲和卓越的線性 (在超過300MHz 的頻率條件下) 來驅動 16 位 ADC 而設計。差分輸入阻抗為 12kΩ,因而允許在輸入端上使用 1:4 和 1:8 變壓器,旨

緩沖集成項目可實現快速自動創建差分對

緩沖集成項目可實現快速自動創建差分對

評論