概述

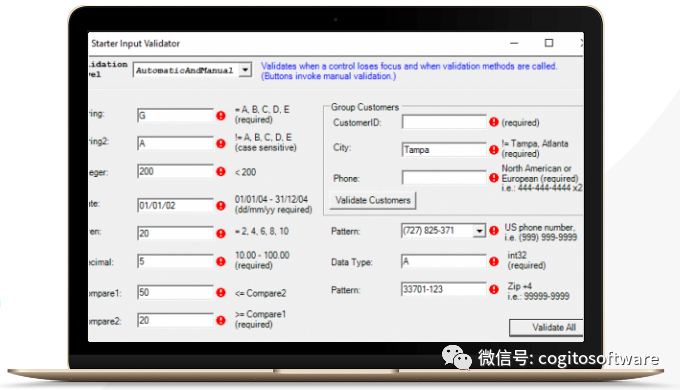

WinForms的簡單、自連接文本驗證。每個驗證標準的可視化配置和可定制的錯誤消息。

無需編寫代碼

表單級或控制級驗證

支持正則表達式,包括許多預(yù)構(gòu)建

XceedGrid for WinForms的一部分,也是XeedUltimate Suite的一部分

即時驗證,無需代碼!只需將其拖放到任何WindowsForm上,它就會將驗證屬性直接添加到所有兼容的控件中。

可視化配置控件驗證或設(shè)置自動添加到每個兼容控件的新屬性。

對于大多數(shù)控件,當發(fā)生驗證錯誤時,它們旁邊會閃爍警告圖標。將鼠標懸停在圖標上以了解規(guī)則的解釋。

表單級或控制級驗證、完全可自定義和本地化的錯誤消息、正則表達式驗證(包括許多)、正則表達式測試儀、各種驗證運算符和選項,等等。

提供獨特的功能,例如將組合框中輸入的值限制為一組預(yù)定義值,并將一個輸入組件中包含的值與另一個輸入組件中包含的值進行比較。

特點

特點

NET技術(shù)

完全用托管C#代碼編寫。Blueprint許可證中包含的源代碼。

包括VB.NET和VisualStudio的C#示例。

面向?qū)ο笤O(shè)計,專為客戶創(chuàng)建.NETFramework。

全面的文檔完全集成到VisualStudio中。

所有錯誤處理都可以通過.NET異常類。

符合CLS(通用語言規(guī)范)。

不使用不安全的區(qū)塊來滿足最低許可要求。

與儀表板和商業(yè)智能軟件很好地集成。

獨特的創(chuàng)新

實現(xiàn)輸入組件驗證的完全可視化方法。

驗證錯誤消息可覆蓋且可本地化。

設(shè)置驗證標準時,可使用多種操作員和選項。

當焦點離開特定輸入組件或調(diào)用通用驗證方法時,標準驗證可用。

與.NETFramework的文本框和組合框控件,以及XceedGrid for WinForms單元格和XceedEditors for WinForms兼容。

可通過從驗證標準或驗證表達式類派生進行擴展。

審核編輯 :李倩

-

代碼

+關(guān)注

關(guān)注

30文章

4968瀏覽量

73961 -

可視化

+關(guān)注

關(guān)注

1文章

1353瀏覽量

22791

原文標題:XceedInput Validator for WinForms

文章出處:【微信號:哲想軟件,微信公眾號:哲想軟件】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

揭秘傳感器淋雨試驗:如何模擬真實降雨環(huán)境驗證可靠性?

RDMA設(shè)計38:寄存器功能驗證與分析

RDMA設(shè)計36:驗證環(huán)境設(shè)計

RDMA設(shè)計35:基于 SV 的驗證平臺

如何驗證硬件冗余設(shè)計的有效性?

利用事務(wù)級加速實現(xiàn)高速、高質(zhì)量的RISC-V驗證

NVMe高速傳輸之擺脫XDMA設(shè)計24: UVM 驗證包設(shè)計

開芯院采用芯華章P2E硬件驗證平臺加速RISC-V驗證

編譯器功能安全驗證的關(guān)鍵要素

Veloce Primo補全完整的SoC驗證環(huán)境

雷擊浪涌發(fā)生器的波形驗證

硬件輔助驗證(HAV) 對軟件驗證的價值

FPGA EDA軟件的位流驗證

技術(shù)分享 | AVM合成數(shù)據(jù)仿真驗證方案

WinForms的XceedInput驗證器

WinForms的XceedInput驗證器

評論