以下文章來源于郝旭帥電子設計團隊,作者郝旭帥

本篇主要討論vivado進行仿真時,GSR信號的理解和影響。

利用vivado進行設計xilinx FPGA時,寫完設計代碼和仿真代碼后,點擊run simulation(啟動modelsim進行仿真)。

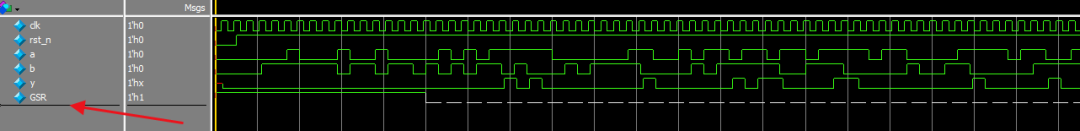

除了能夠看到我們所寫的仿真代碼中的信號外,還會看到一個GSR信號,前面等于1,在100ns左右變為0的虛線。

為什么會有這個信號?

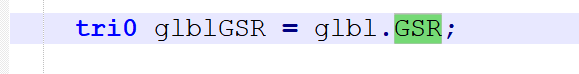

vivado在啟動仿真時,會默認添加一個文件:glbl。GSR信號就在這個當中。

有什么影響嗎?

一般來說:在進行仿真時,都是直接將其刪除,或者直接選擇忽略他,并不影響任何東西。

那么這個信號的意義是什么呢?

感覺好像是無意義的。

有一天在進行時序仿真時,發現了一個bug。

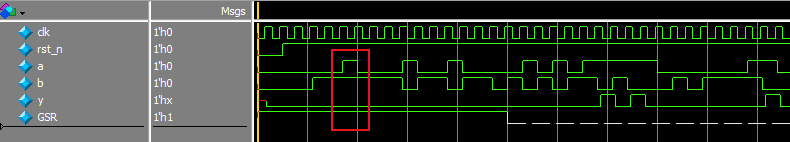

上圖是一個時序邏輯(異步復位的寄存器)輸出的與門邏輯,在GSR為高電平期間,a和b都為高電平了,y應該輸出高電平,但是并沒有。而在GSR為0期間,y輸出都是正常的。

那么感覺就有可能是GSR的問題。

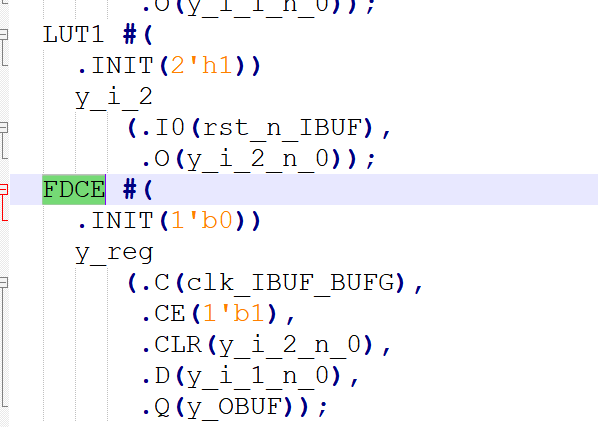

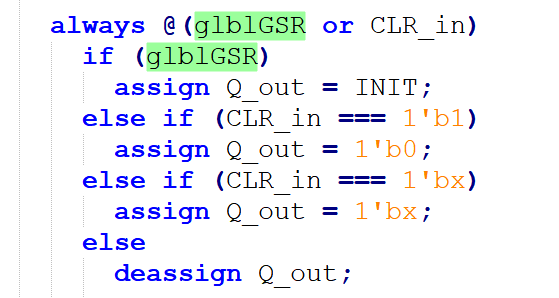

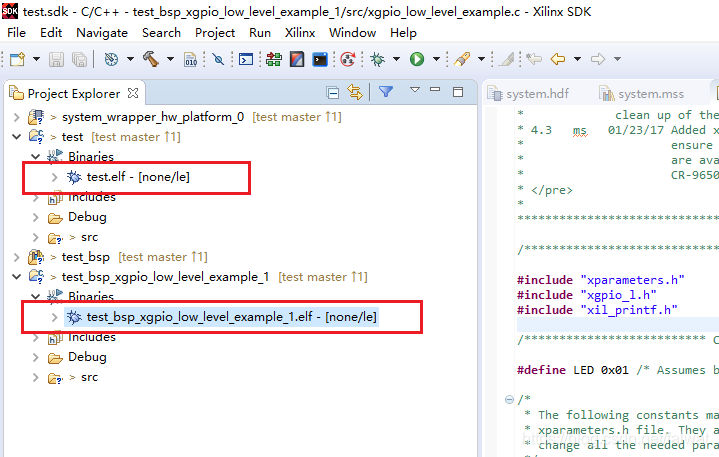

找到時序仿真的文件,內部是使用FPGA器件內部的部件所組成的電路。(找到仿真庫,找到仿真所使用的文件)

注:后仿真使用的不是咱們所寫的verilog文件,而是經過綜合之后的文件。

再次通過尋找庫文件(在unisims庫中),找到FDCE的文件內部。

發現這個這個fdce是和GSR信號有關系的。

也就是說在GSR為高電平期間,輸出值一直是默認值,不會隨著D信號的改變而改變。

那怎么辦呢?

要不然去修改GSR信號拉低的時間,要不然去推后我們仿真時,信號有效的位置。

建議:我們做仿真(特別是時序仿真)時,復位的時間大于100ns(給予有效信號的時間放到100ns之后)。

簡單解析GSR:FPGA內部的一個全局復位信號,用于強制寄存器狀態。

在 Vivado 仿真中,GSR 信號是理解設計初始化(時間零行為)和全局復位的核心。仿真器默認會在 t=0 激活 GSR 一段時間,模擬 FPGA 配置完成后的硬件行為,將所有受控寄存器強制設置到它們的初始狀態。之后 GSR 釋放,用戶設計的邏輯(包括用戶復位信號)才開始正常運行。在波形中觀察 glbl.GSR 的時序以及寄存器在 t=0 附近的變化,是驗證設計啟動和復位行為是否符合預期的關鍵步驟。除非有特殊調試需求,一般不應禁用或修改默認的 GSR 仿真行為。

-

仿真

+關注

關注

55文章

4503瀏覽量

138462 -

信號

+關注

關注

12文章

2916瀏覽量

80264 -

Vivado

+關注

關注

19文章

858瀏覽量

71231

原文標題:vivado進行仿真時,GSR信號的理解和影響

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何用Python實現Vivado和ModelSim仿真自動化?

基于VB的GSR實時信號監護系統

Vivado軟件仿真DDS核的過程中應該注意的問題

Vivado下的仿真詳細過程

如何使用Vivado中的Synopsys VCS仿真器進行仿真

Vivado調用Questa Sim或ModelSim仿真小技巧

vivado仿真時GSR信號的影響

vivado仿真時GSR信號的影響

評論