原創聲明:

本原創教程由芯驛電子科技(上海)有限公司(ALINX)創作,版權歸本公司所有,如需轉載,需授權并注明出處。

適用于板卡型號:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

按鍵是FPGA設計當中最常用也是最簡單的外設,本章通過按鍵檢測實驗,檢測開發板的按鍵功能是否正常,并了解硬件描述語言和FPGA的具體關系,學習Vivado RTL ANALYSIS的使用。

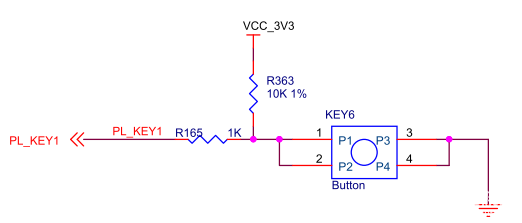

1.按鍵硬件電路

開發板按鍵部分電路

從圖中可以看到,電路的按鍵松開時是高電平,按下時是低電平。

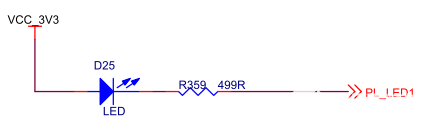

開發板LED部分電路

開發板LED部分電路

而LED部分,高電平滅,低電平亮

2. 程序設計

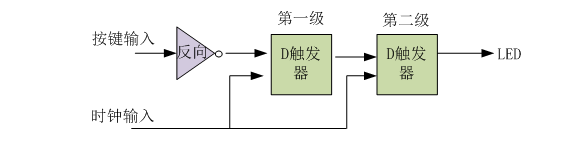

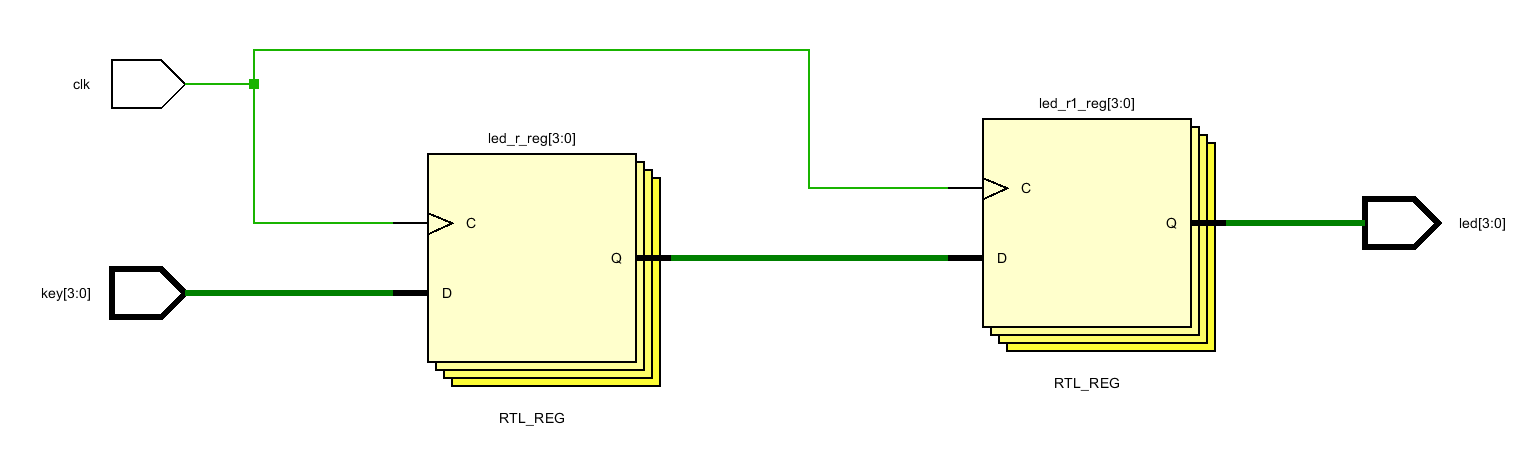

這個程序沒有設計的很復雜,通過簡單的硬件描述語言看透硬件描述語言和FPGA硬件的聯系。首先我們將按鍵輸入經過一個非門后再經過2組D觸發器。經過D觸發器的信號,會在D觸發器時鐘輸入的上升沿鎖存然后再送到輸出。

在進行硬件描述語言編碼之前,我們已經把硬件構建完成,這是一個正常的開發流程。有了硬件設計思路無論是通過畫圖還是通過Verilog HDL、VHDL都能完成設計,根據設計的復雜程序和對某種語言的熟悉程序來選擇工具。

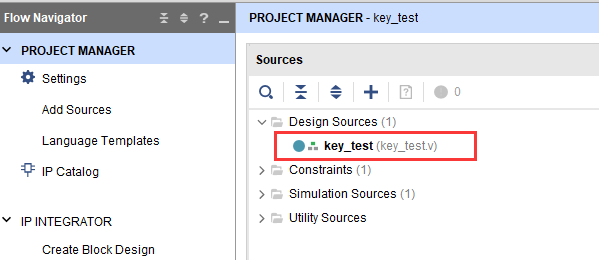

3. 創建Vivado工程

3.1 首先建立按鍵的測試工程,添加verilog測試代碼,完成編譯分配管腳等流程。

`timescale1ns/1psmodulekey_test( inputclk,//systemclock25Mhzonboard input[3:0]key,//inputfourkeysignal,whenthekeydown,thevalueis0 output[3:0]led//LEDdisplay,whenthesiganllow,LEDlighten);reg[3:0]led_r;//definethefirststageregister,generatefourDFlip-flop reg[3:0]led_r1;//definethesecondstageregister,generatefourDFlip-flopalways@(posedgeclk)begin led_r<=??key;//first?stage?latched?dataendalways@(posedge?clk)begin led_r1?<=?led_r;//second?stage?latched?dataendassign?led?=?led_r1;endmodule

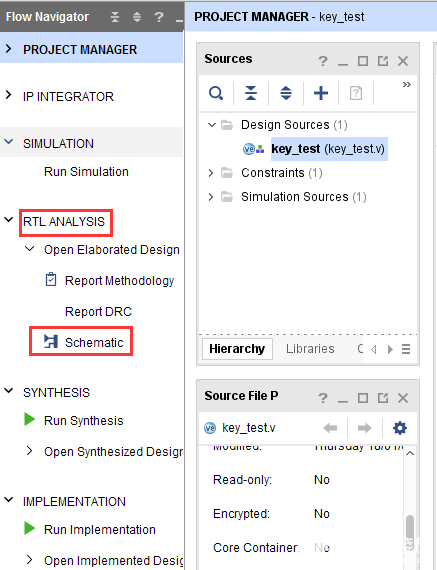

3.2 我們可以使用RTL ANALYSIS工具查看設計

3.3 分析RTL圖,可以看出兩級D觸發器,和預期設計一致。

4. 板上驗證

Bit文件下載到開發板以后,開發板上的"PL LED"處于亮狀態,按鍵“PL KEY1”按下“PL LED1”滅。

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636328 -

按鍵

+關注

關注

4文章

229瀏覽量

58500 -

Zynq

+關注

關注

10文章

630瀏覽量

49449 -

MPSoC

+關注

關注

0文章

203瀏覽量

25173 -

Vivado

+關注

關注

19文章

857瀏覽量

71114

發布評論請先 登錄

【「Altium Designer 25 電路設計精進實踐」閱讀體驗】+讀后感

使用Aurora 6466b協議實現AMD UltraScale+ FPGA與AMD Versal自適應SoC的對接

如何在Zynq UltraScale+ MPSoC平臺上通過JTAG啟動嵌入式Linux鏡像

AMD UltraScale架構:高性能FPGA與SoC的技術剖析

現已上市:AMD Spartan UltraScale+ FPGA SCU35 評估套件——面向所有開發人員的經濟實惠平臺

雙Zynq MPSoC PS側PCIe高速DMA互連解決方案

AMD Spartan UltraScale+ FPGA的優勢和亮點

AMD Vivado IP integrator的基本功能特性

璞致電子 UltraScale+ RFSoC 架構下的軟件無線電旗艦開發平臺

第九章 W55MH32 HTTP Server示例

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 異構架構下的智能邊緣計算標桿

AMD FPGA異步模式與同步模式的對比

AMD Spartan UltraScale+ FPGA 開始量產出貨

Xilinx Ultrascale系列FPGA的時鐘資源與架構解析

【ZYNQ Ultrascale+ MPSOC FPGA教程】第九章Vivado下按鍵實驗

【ZYNQ Ultrascale+ MPSOC FPGA教程】第九章Vivado下按鍵實驗

評論