在一篇以前的文章中,Timothy T.曾談到JESD204B接口標(biāo)準(zhǔn)(該標(biāo)準(zhǔn)越來越受歡迎,因?yàn)樗茉诟咚贁?shù)據(jù)采集系統(tǒng)里簡化設(shè)計(jì))的時鐘要求。在本文中,筆者將談?wù)摱秳雍铣善髋c清除器的不同系統(tǒng)參考信號

2018-05-14 08:48:18 10876

10876

隨著數(shù)模轉(zhuǎn)換器的轉(zhuǎn)換速率越來越高,JESD204B 串行接口已經(jīng)越來越多地廣泛用在數(shù)模轉(zhuǎn)換器上,其對器件時鐘和同步時鐘之間的時序關(guān)系有著嚴(yán)格需求。本文就重點(diǎn)講解了JESD204B 數(shù)模轉(zhuǎn)換器的時鐘

2015-01-23 10:42:18 27137

27137 更低,以及轉(zhuǎn)換器和邏輯器件的封裝更小。多家供應(yīng)商的新型模擬/數(shù)字轉(zhuǎn)換器采用此接口,例如ADI的AD9250。與現(xiàn)有接口格式和協(xié)議相比,JESD204B接口更復(fù)雜、

2024-03-26 08:22:36 2179

2179

開發(fā)串行接口業(yè)界標(biāo)準(zhǔn)JESD204A/JESD204B的目的在于解決以高效省錢的方式互連最新寬帶數(shù)據(jù)轉(zhuǎn)換器與其他系統(tǒng)IC的問題。

2021-11-01 11:24:16 6384

6384

本故障排除指南并未窮盡所有可能,但為使用JESD204B鏈路以及希望了解更多信息的工程師提供了一個很好的基本框架。

2022-01-10 11:06:05 4040

4040

。圖3:第二(當(dāng)前)版——JESD204B在JESD204標(biāo)準(zhǔn)之前的兩個版本中,沒有確保通過接口的確定延遲相關(guān)的條款。JESD204B修訂版通過提供一種機(jī)制,確保兩個上電周期之間以及鏈路重新同步期間

2019-05-29 05:00:03

,CML輸出驅(qū)動器的效率開始占優(yōu)。CML的優(yōu)點(diǎn)是:因?yàn)閿?shù)據(jù)的串行化,所以對于給定的分辨率,它需要的輸出對數(shù)少于LVDS和CMOS驅(qū)動器。JESD204B接口規(guī)范所說明的CML驅(qū)動器還有一個額外的優(yōu)勢

2019-06-17 05:00:08

作者:Ken C在使用我們的最新模數(shù)轉(zhuǎn)換器 (ADC) 和數(shù)模轉(zhuǎn)換器 (DAC) 設(shè)計(jì)系統(tǒng)時,我已知道了很多有關(guān) JESD204B 接口標(biāo)準(zhǔn)的信息,這些器件使用該協(xié)議與 FPGA 通信。此外,我還在

2018-09-13 14:21:49

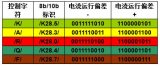

什么是8b/10b編碼,為什么JESD204B接口需使用這種編碼?怎么消除影響JESD204B鏈路傳輸?shù)囊蛩兀?b class="flag-6" style="color: red">JESD204B中的確定延遲到底是什么? 它是否就是轉(zhuǎn)換器的總延遲?JESD204B如何使用結(jié)束位?結(jié)束位存在的意義是什么?如何計(jì)算轉(zhuǎn)換器的通道速率?什么是應(yīng)用層,它能做什么?

2021-04-13 06:39:06

摘要 隨著數(shù)模轉(zhuǎn)換器的轉(zhuǎn)換速率越來越高,JESD204B 串行接口已經(jīng)越來越多地廣泛用在數(shù)模轉(zhuǎn)換器上,其對器件時鐘和同步時鐘之間的時序關(guān)系有著嚴(yán)格需求。本文就重點(diǎn)講解了JESD204B 數(shù)模轉(zhuǎn)換器

2019-06-19 05:00:06

MS-2503: 消除影響

JESD204B鏈路傳輸?shù)囊蛩?/div>

2019-09-20 08:31:46

在使用我們的最新模數(shù)轉(zhuǎn)換器 (ADC) 和數(shù)模轉(zhuǎn)換器 (DAC) 設(shè)計(jì)系統(tǒng)時,我已知道了很多有關(guān) JESD204B 接口標(biāo)準(zhǔn)的信息,這些器件使用該協(xié)議與 FPGA 通信。此外,我還在 E2E 上的該

2022-11-21 07:02:17

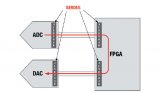

在使用最新模數(shù)轉(zhuǎn)換器 (ADC) 和數(shù)模轉(zhuǎn)換器 (DAC) 設(shè)計(jì)系統(tǒng)時,我已知道了很多有關(guān) JESD204B 接口標(biāo)準(zhǔn)的信息,這些器件使用該協(xié)議與 FPGA 通信。那么在解決 ADC 至 FPGA

2021-04-06 06:53:56

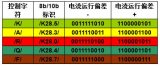

JESD204B的工作原理JESD204B的控制字符

2021-04-06 06:01:20

請問各位大俠:JESD204B專用于ADC/DAC和FPGA或ASIC的接口嗎,該接口同Rapid/PCIe的物理層Serdes接口有何區(qū)別,謝謝!

2025-02-08 09:10:29

JESD204B生存指南

2019-05-28 12:08:12

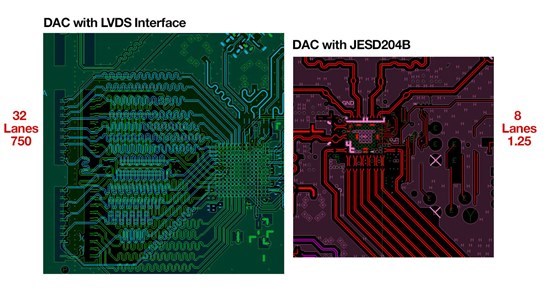

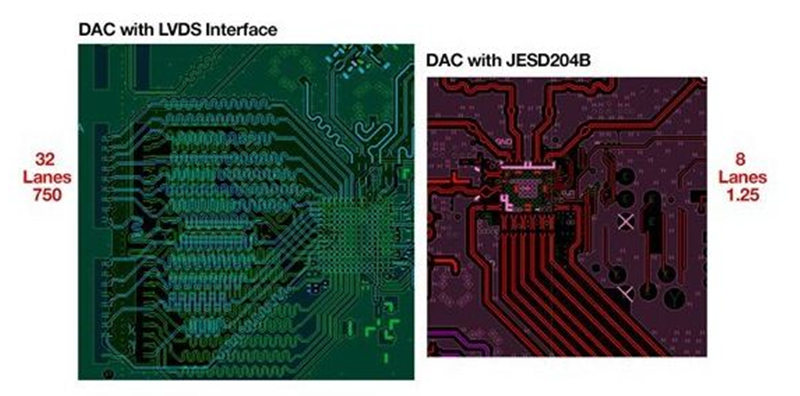

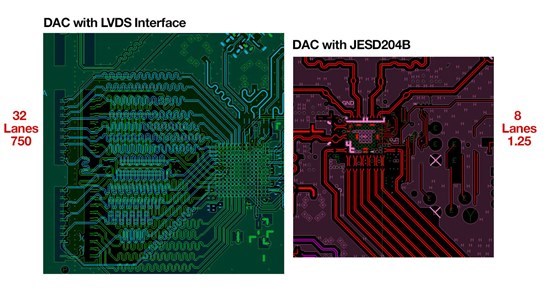

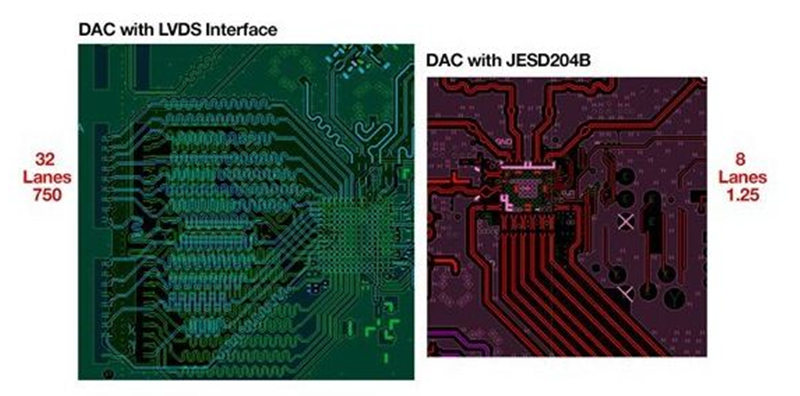

的是 JESD204B 接口將如何簡化設(shè)計(jì)流程。與 LVDS 及 CMOS 接口相比,JESD204B 數(shù)據(jù)轉(zhuǎn)換器串行接口標(biāo)準(zhǔn)可提供一些顯著的優(yōu)勢,包括更簡單的布局以及更少的引腳數(shù)。因此它能獲得工程師

2022-11-23 06:35:43

的任務(wù)。

問:JESD204B中的確定延遲到底是什么?它是否就是轉(zhuǎn)換器的總延遲?

答:ADC的總延遲表示其輸入一個模擬樣本、處理、并從器件輸出數(shù)字信號所需的時間。類似地,DAC的總延遲表示從數(shù)字

2024-01-03 06:35:04

PCB 布局有多大幫助的實(shí)例;高靈活布局:JESD204B 對畸變要求低,可實(shí)現(xiàn)更遠(yuǎn)的傳輸距離。這有助于將邏輯器件部署在距離數(shù)據(jù)轉(zhuǎn)換器更遠(yuǎn)的位置,以避免對靈敏模擬器件產(chǎn)生影響;滿足未來需求:該接口能夠

2018-09-18 11:29:29

所需的時間。該時間通 常以分辨率為幀時鐘周期或以器件時鐘進(jìn)行測量。JESD204B的確定性延遲規(guī)格沒有考慮到ADC模擬前端內(nèi)核 或DAC后端模擬內(nèi)核的情況。它只基于輸入和輸出 JESD204B數(shù)字幀

2018-10-15 10:40:45

我最近嘗試用arria 10 soc實(shí)現(xiàn)與ad9680之間的jesd204B協(xié)議,看了很多資料,卻依然感覺無從下手,不知道哪位大神設(shè)計(jì)過此協(xié)議,希望可以請教一番,在此先謝過。

2017-12-13 12:47:27

因?qū)嶋H需求,本人想使用JESD204b的ip核接收ADC發(fā)送過來的數(shù)據(jù),ADC發(fā)送的數(shù)據(jù)鏈路速率是15gbps, 廠家說屬于204b標(biāo)準(zhǔn)。我看到jesd204b的ip核標(biāo)準(zhǔn)最大是12.5gbps,但是支持的支持高達(dá)16.375 Gb/s的非標(biāo)準(zhǔn)線速率。請問我可以使用這個IP核接收ADC的數(shù)據(jù)嗎?

2020-08-12 09:36:39

AD9164 JESD204B接口的傳輸層是如何對I/Q數(shù)據(jù)進(jìn)行映射的

2023-12-04 07:27:34

AD采集芯片為AD9680-1000,時鐘芯片為AD9528。當(dāng) AD 采樣時鐘為 500MHz 時,jesd204B (串行線速 = 5 Gbps) 穩(wěn)定。但是,當(dāng) AD 采樣時鐘為 800MHz

2025-04-15 06:43:11

。與LVDS及CMOS接口相比,JESD204B數(shù)據(jù)轉(zhuǎn)換器串行接口標(biāo)準(zhǔn)可提供一些顯著的優(yōu)勢,比如更簡單的布局以及更少的引腳數(shù)。也因此它獲得了更多工程師的青睞和關(guān)注,它具備如下系統(tǒng)級優(yōu)勢:1、更小的封裝尺寸

2019-12-03 17:32:13

一,JESD204B應(yīng)用的優(yōu)缺點(diǎn)接觸過FPGA高速數(shù)據(jù)采集設(shè)計(jì)的朋友,應(yīng)該會聽過新術(shù)語“JESD204B”。這是一種新型的基于高速SERDES的ADC/DAC數(shù)據(jù)傳輸接口。隨著ADC/DAC的采樣

2019-12-04 10:11:26

JESD204B到底是什么呢?是什么導(dǎo)致了JESD204B標(biāo)準(zhǔn)的出現(xiàn)?什么是JESD204B標(biāo)準(zhǔn)?為什么關(guān)注JESD204B接口?

2021-05-24 06:36:13

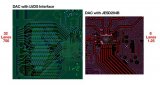

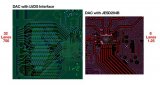

時鐘成為可能。總結(jié)JESD204B工業(yè)串行接口標(biāo)準(zhǔn)降低了高速數(shù)據(jù)轉(zhuǎn)換器和FPGA以及其他器件之間的數(shù)字輸入和輸出通道數(shù)。更少的互連可以簡化布局布線并讓設(shè)計(jì)出更小的尺寸成為可能(見圖4)。這些優(yōu)勢對很多

2019-05-29 05:00:04

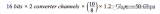

使用JESD204B接口,線速率怎么計(jì)算?在文檔表9-2中線速率等于 fLINERATE=fs*R,如果我選擇雙通道設(shè)備,采樣時鐘fs為500MHz,在表8-17,中選擇模式0,N&

2024-11-18 07:10:40

在使用JESD204B協(xié)議時,當(dāng)L=8時,如果時雙通道數(shù)據(jù),如何對數(shù)據(jù)進(jìn)行組幀?是直接使用前8通道嗎

2024-11-14 07:51:24

關(guān)于JESD204B接口你想知道的都在這

2021-09-29 06:56:22

具有可重復(fù)的確定性延遲。隨著轉(zhuǎn)換器的速度和分辨率不斷提升,JESD204B接口在ADI高速轉(zhuǎn)換器和集成RF收發(fā)器中也變得更為常見。此外,F(xiàn)PGA和ASIC中靈活的串行器/解串器(SERDES)設(shè)計(jì)正逐步

2018-10-16 06:02:44

描述JESD204B 鏈路是數(shù)據(jù)轉(zhuǎn)換器數(shù)字接口的最新趨勢。這些鏈路利用高速串行數(shù)字技術(shù)提供很大的益處(包括增大的信道密度)。此參考設(shè)計(jì)解決了其中一個采用新接口的挑戰(zhàn):理解并設(shè)計(jì)鏈路延遲。一個示例實(shí)現(xiàn)

2018-11-21 16:51:43

JESD204B數(shù)模轉(zhuǎn)換器的時鐘規(guī)范是什么?JESD204B數(shù)模轉(zhuǎn)換器有哪些優(yōu)勢?如何去實(shí)現(xiàn)JESD204B時鐘?

2021-05-18 06:06:10

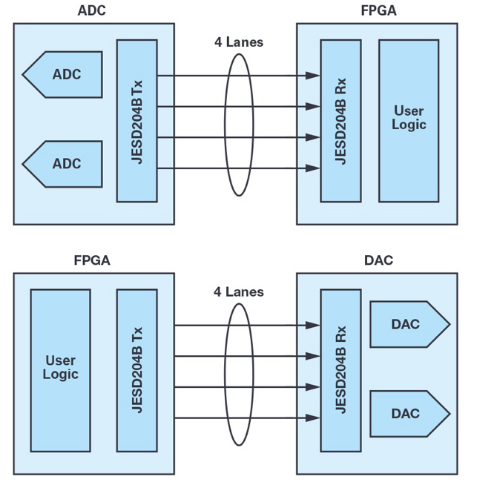

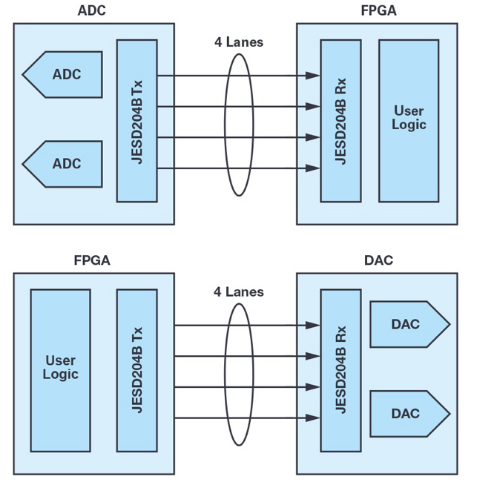

的模數(shù)轉(zhuǎn)換器(ADC)和數(shù)模轉(zhuǎn)換器(DAC)支持最新的JESD204B串行接口標(biāo)準(zhǔn),出現(xiàn)了FPGA與這些模擬產(chǎn)品的最佳接口方式問題。FPGA一直支持千兆串行/解串(SERDES)收發(fā)器。然而在過去,大多數(shù)ADC

2021-04-06 09:46:23

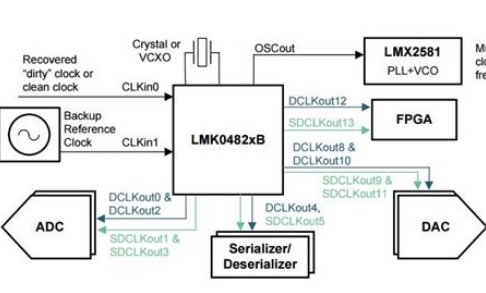

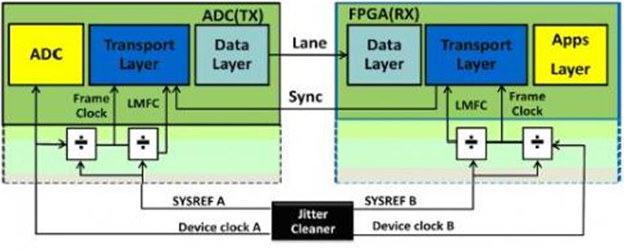

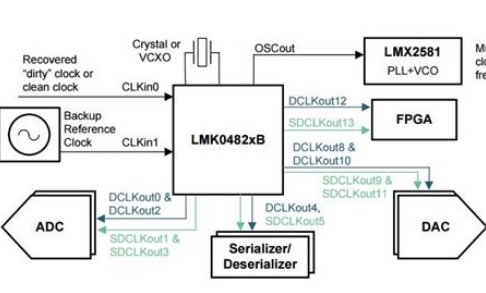

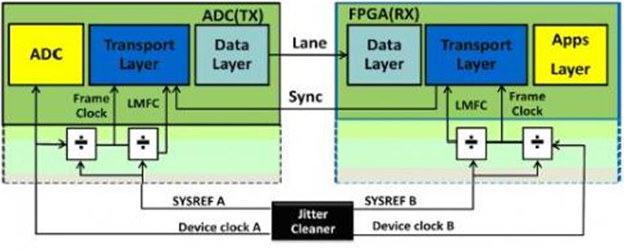

LMK04821系列器件為該話題提供了很好的范例研究素材,因?yàn)樗鼈兪歉咝阅艿碾p環(huán)路抖動清除器,可在具有器件和SYSREF時鐘的子類1時鐘方案里驅(qū)動多達(dá)七個JESD204B轉(zhuǎn)換器或邏輯器件。圖1是典型

2022-11-18 06:36:26

of this significant interfacing breakthrough. JESD204B工業(yè)串行接口標(biāo)準(zhǔn)降低了高速數(shù)據(jù)轉(zhuǎn)換器和FPGA以及其他器件之間的數(shù)字輸入和輸出通道數(shù)。更少的互連可以簡化布局

2021-11-03 07:00:00

建立了所需的電氣連接,如圖 1 所示。請注意圖中箭頭表示信號方向。圖1 —JESD204B TX 至RX 鏈路的信號連接從 TX (tx_dataout) 到 RX 的信號是包含數(shù)據(jù)鏈路的串行解串器信道

2018-09-13 09:55:26

連接,如圖 1 所示。請注意圖中箭頭表示信號方向。圖 1 — JESD204B TX 至 RX 鏈路的信號連接從 TX (tx_dataout) 到 RX 的信號是包含數(shù)據(jù)鏈路的串行解串器信道信號。這些

2022-11-21 07:18:42

我在調(diào)試TI ADS52J90板卡JESD204B接口遇到的問題:

1、目前在應(yīng)用手冊中能看到LVDS的詳細(xì)說明,但是缺少關(guān)于JESD204B的相關(guān)資料,能否提供相關(guān)JESD204B的相關(guān)資料

2024-11-28 06:13:11

全球領(lǐng)先的高性能信號處理解決方案供應(yīng)商ADI今天發(fā)布了一款基于FPGA的參考設(shè)計(jì)及配套軟件和HDL代碼,該參考設(shè)計(jì)可降低集成JESD204B兼容轉(zhuǎn)換器的高速系統(tǒng)的設(shè)計(jì)風(fēng)險。該軟件為JESD204B

2013-10-17 16:35:20 1258

1258 Altera公司今天宣布,開始提供多種JESD204B解決方案,設(shè)計(jì)用于在使用了最新JEDEC JESD204B標(biāo)準(zhǔn)的系統(tǒng)中簡化Altera FPGA和高速數(shù)據(jù)轉(zhuǎn)換器的集成。很多應(yīng)用都使用了這一接口標(biāo)準(zhǔn),包括雷達(dá)、無線射頻前端、醫(yī)療成像設(shè)備、軟件無線電,以及工業(yè)應(yīng)用等。

2014-01-24 10:14:58 2776

2776 隨著數(shù)模轉(zhuǎn)換器的轉(zhuǎn)換速率越來越高, JESD204B 串行接口已經(jīng)越來越多地廣泛用在數(shù)模轉(zhuǎn)換器上,其對器件時鐘和同步時鐘之間的時序關(guān)系有著嚴(yán)格需求。本文就重點(diǎn)講解了JESD204B 數(shù)模轉(zhuǎn)換器的時鐘規(guī)范,以及利用 TI 公司的芯片實(shí)現(xiàn)其時序要求。

2016-12-21 14:39:34 44

44 在使用我們的最新模數(shù)轉(zhuǎn)換器 (ADC) 和數(shù)模轉(zhuǎn)換器 (DAC) 設(shè)計(jì)系統(tǒng)時,我已知道了很多有關(guān) JESD204B 接口標(biāo)準(zhǔn)的信息,這些器件使用該協(xié)議與 FPGA 通信。此外,我還在 E2E 上的該

2017-04-08 04:48:17 2714

2714

。隨著轉(zhuǎn)換器的速度和分辨率不斷提升,JESD204B接口在ADI高速轉(zhuǎn)換器和集成RF收發(fā)器中也變得更為常見。

2017-04-12 10:22:11 16280

16280

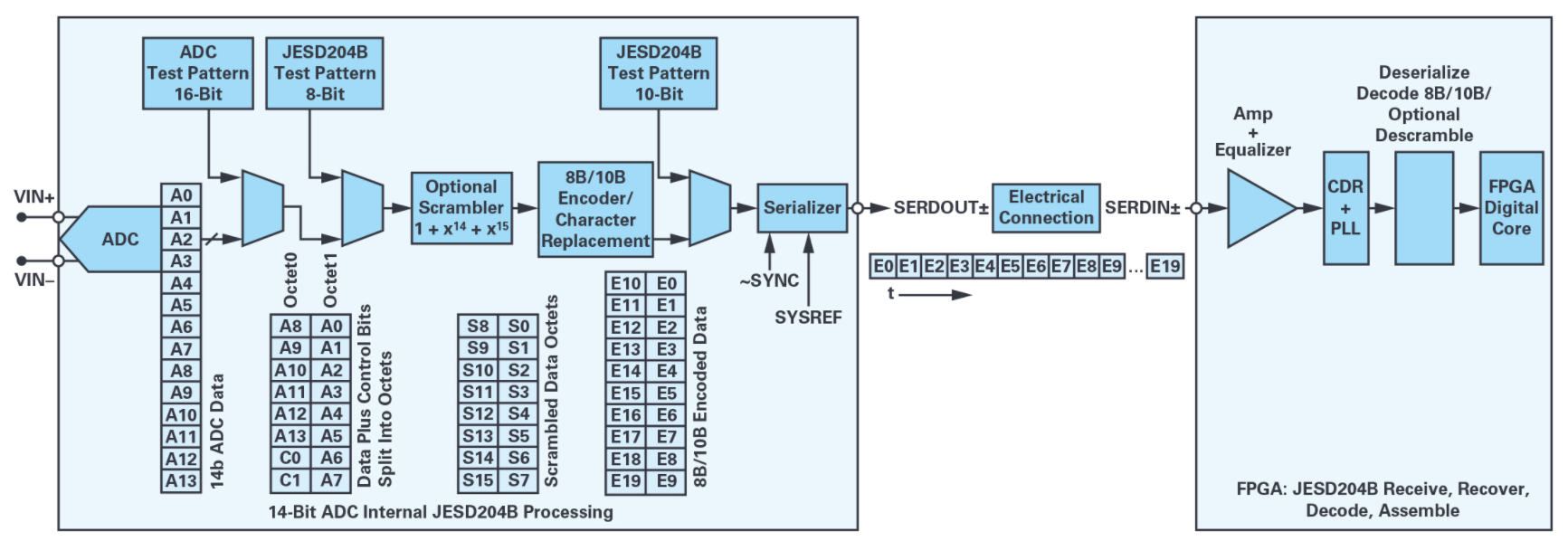

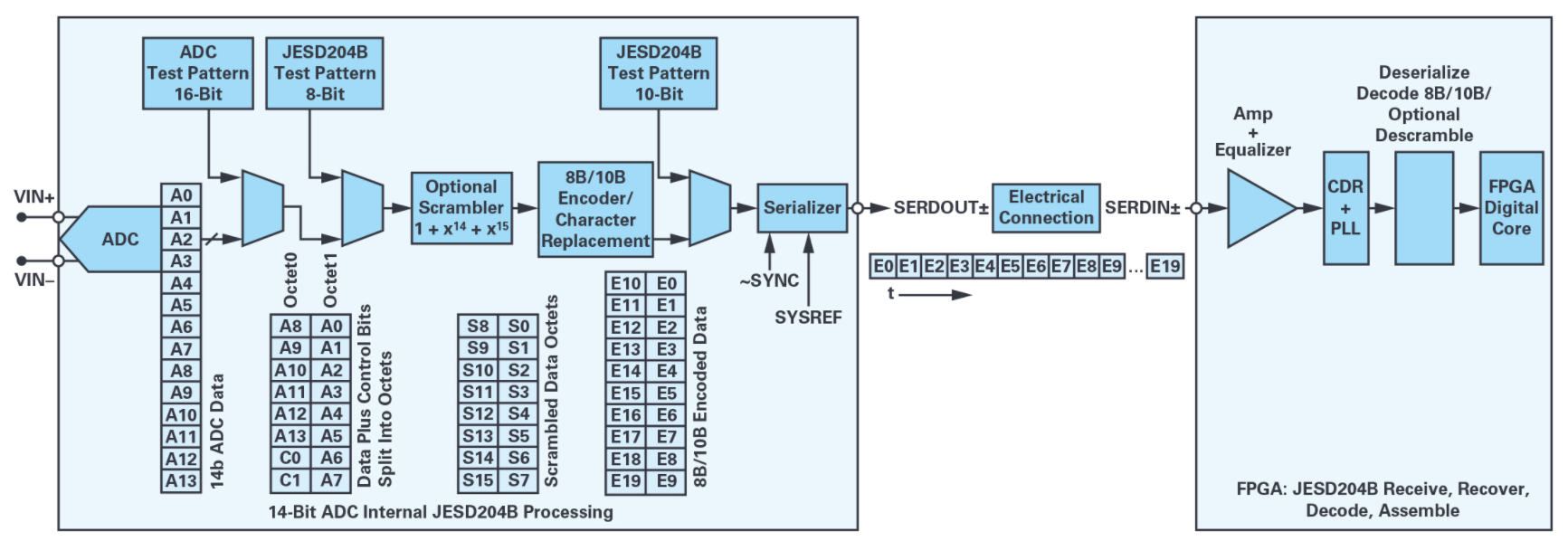

JESD204B是一種高速數(shù)據(jù)傳輸協(xié)議,采用8位/10位編碼和加擾技術(shù),旨在確保足夠的信號完整性。針對JESD204B標(biāo)準(zhǔn),總吞吐量變?yōu)樵诖嗽O(shè)置中,由于AD9250中沒有其他數(shù)字處理任務(wù),所以JESD204B鏈路(JESD204B發(fā)射器)一目了然。

2017-09-08 11:36:03 39

39 隨著高速ADC跨入GSPS范圍,與FPGA(定制ASIC)進(jìn)行數(shù)據(jù)傳輸?shù)氖走x接口協(xié)議是JESD204B。為了捕捉頻率范圍更高的RF頻譜,需要寬帶RF ADC。在其推動下,對于能夠捕捉更寬帶寬并支持

2017-11-16 18:48:16 11659

11659

和RTL代碼的編寫。設(shè)計(jì)以最新的版本JESD204B.01(July 2011)為參考,設(shè)計(jì)根據(jù)數(shù)據(jù)流的傳輸分為傳輸層、數(shù)據(jù)鏈路層、物理成進(jìn)行代碼的編寫,其中JESD204B的模擬特性在本設(shè)計(jì)中因?yàn)闊o法實(shí)現(xiàn),所以并沒有做過多的描述,具體的模擬的細(xì)節(jié)可以參考有JEDEC發(fā)布的標(biāo)準(zhǔn)協(xié)議。

2017-11-17 09:36:56 3518

3518

JESD204B為業(yè)界標(biāo)準(zhǔn)序列通信鏈接,數(shù)據(jù)轉(zhuǎn)換器與現(xiàn)場可編程門陣列(FPGA)、數(shù)字信號處理器(DSP)、特定應(yīng)用集成電路(ASIC)等裝置間的數(shù)字數(shù)據(jù)接口因此能化繁為簡,這項(xiàng)標(biāo)準(zhǔn)減少裝置間路由

2017-11-17 14:45:16 3921

3921

在從事高速數(shù)據(jù)擷取設(shè)計(jì)時使用FPGA的人大概都聽過新JEDEC標(biāo)準(zhǔn)「JESD204B」的名號。近期許多工程師均聯(lián)絡(luò)德州儀器,希望進(jìn)一步了解 JESD204B 接口,包括與FPGA如何互動、JESD204B如何讓他們的設(shè)計(jì)更容易執(zhí)行等。本文介紹 JESD204B標(biāo)準(zhǔn)演進(jìn),以及對系統(tǒng)設(shè)計(jì)工程師有何影響。

2017-11-18 02:57:01 14901

14901 在使用我們的最新模數(shù)轉(zhuǎn)換器(ADC)和數(shù)模轉(zhuǎn)換器(DAC)設(shè)計(jì)系統(tǒng)時,我已知道了很多有關(guān) JESD204B接口標(biāo)準(zhǔn)的信息,這些器件使用該協(xié)議與FPGA 通信。

2017-11-18 04:10:55 3410

3410

目前,將JESD204B作為高速數(shù)據(jù)轉(zhuǎn)換器首選數(shù)字接口的趨勢如火如荼。JESD204接口于2006年首次發(fā)布,2008年改版為JESD204A,2011年8月再改版為目前的JESD204B

2017-11-18 06:07:01 17928

17928

隨著數(shù)模轉(zhuǎn)換器的轉(zhuǎn)換速率越來越高,JESD204B 串行接口已經(jīng)越來越多地廣泛用在數(shù)模轉(zhuǎn)換器上,其對器件時鐘和同步時鐘之間的時序關(guān)系有著嚴(yán)格需求。本文就重點(diǎn)講解了JESD204B 數(shù)模轉(zhuǎn)換器的時鐘

2017-11-18 08:00:01 2492

2492 的是 JESD204B 接口將如何簡化設(shè)計(jì)流程。 與 LVDS 及 CMOS 接口相比,JESD204B 數(shù)據(jù)轉(zhuǎn)換器串行接口標(biāo)準(zhǔn)可提供一些顯著的優(yōu)勢,包括更簡單的布局以及更少的引腳數(shù)。因此它能獲得工程師的青睞和關(guān)注也就不足為奇了,它具備如下系統(tǒng)級優(yōu)勢: 更小的封裝尺寸與更低的封裝成本。

2017-11-18 08:36:01 3853

3853

JESD204B是最新的12.5 Gb/s高速、高分辨率數(shù)據(jù)轉(zhuǎn)換器串行接口標(biāo)準(zhǔn)。轉(zhuǎn)換器制造商的相關(guān)產(chǎn)品已進(jìn)入市場,并且支持JESD204B標(biāo)準(zhǔn)的產(chǎn)品預(yù)計(jì)會在不久的將來大量面世。JESD204B接口

2017-11-18 18:57:16 3629

3629

Arria10接口的JESD204B與ADI9144的互操作性

2018-06-20 00:06:00 5211

5211

在此設(shè)置中,由于AD9250中沒有其他數(shù)字處理任務(wù),所以JESD204B鏈路(JESD204B發(fā)射器)一目了然。對于JESD204B鏈路來說,通道A為轉(zhuǎn)換器“0”( M0 ),而通道B為轉(zhuǎn)換器“1”(M1),這就意味著“M”的值為2。此設(shè)置的總線路速率為

2018-08-24 11:47:52 5375

5375

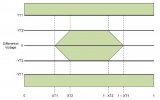

該視頻將為觀眾介紹JESD204B接口中的眼圖測量。

2019-08-01 06:19:00 4828

4828 ADI和Xilinx的專家解釋了JESD204B接口標(biāo)準(zhǔn)的重要性,并說明了該標(biāo)準(zhǔn)如何用于ADC到FPGA設(shè)計(jì)中。

2019-08-01 06:15:00 3813

3813 該視頻將為觀眾介紹JESD204B接口中的眼圖測量。

2019-08-19 06:06:00 5863

5863 真正的串行接口(稱作JESD204)。JESD204 接口被定義為一種單通道、高速串行鏈路,其使用高達(dá)3.125 Gbps 的數(shù)據(jù)速率把單個或者多個數(shù)據(jù)轉(zhuǎn)換器連接至數(shù)字邏輯器件。

2019-05-13 09:16:42 13882

13882

AD9675:采用JESD204B的八進(jìn)制超聲波AFE數(shù)據(jù)表

2021-04-16 10:09:00 8

8 AD9690:14位,1 GSPS/500 MSPS JESD204B,模擬到數(shù)字Converter數(shù)據(jù)Sheet

2021-04-18 14:45:57 10

10 AD9689:14位,2.0 GSPS/2.6 GSPS,JESD204B,雙模擬到數(shù)字轉(zhuǎn)換器數(shù)據(jù)Sheet

2021-04-21 19:01:52 17

17 LTC6952:超低抖動、4.5 GHz PLL,帶11個輸出和JESD204B/JESD204C支持?jǐn)?shù)據(jù)表

2021-04-22 15:52:09 9

9 AD9691:14位,1.25 GSPS JESD204B,雙模擬到數(shù)字Converator數(shù)據(jù)Sheet

2021-04-24 10:47:54 4

4 AD9671:帶數(shù)字解調(diào)器的八進(jìn)制超聲波AFE,JESD204B數(shù)據(jù)表

2021-04-29 16:13:06 8

8 AD9697:14位,1300 MSPS,JESD204B,模擬到數(shù)字轉(zhuǎn)換器數(shù)據(jù)Sheet

2021-05-13 09:18:42 5

5 AD9213:12位,6 GSPS/10.25 GSPS,JESD204B,RF模擬到數(shù)字轉(zhuǎn)換器數(shù)據(jù)Sheet

2021-05-17 19:23:17 6

6 帶JESD204B串行接口的14位250 Msps ADC系列

2021-05-18 15:04:50 7

7 如何同 FPGA 協(xié)作。他們特別感興趣的是 JESD204B 接口將如何簡化設(shè)計(jì)流程。

與 LVDS 及 CMOS 接口相比,JESD204B 數(shù)據(jù)轉(zhuǎn)換器串行接口標(biāo)準(zhǔn)可提供一些顯著的優(yōu)勢,包括更簡單

2021-11-10 09:43:33 1032

1032

與現(xiàn)有接口格式和協(xié)議相比,JESD204B接口更復(fù)雜、更微妙,必須克服一些困難才能實(shí)現(xiàn)其優(yōu)勢。像其他標(biāo)準(zhǔn)一樣,要使該接口比單倍數(shù)據(jù)速率或雙倍數(shù)據(jù)速率CMOS/LVDS等常用接口更受歡迎,它必須能無縫地工作。

2022-04-21 14:28:07 5912

5912 接觸過FPGA高速數(shù)據(jù)采集設(shè)計(jì)的朋友,應(yīng)該會聽過新術(shù)語“JESD204B”。這是一種新型的基于高速SERDES的ADC/DAC數(shù)據(jù)傳輸接口。隨著ADC/DAC的采樣速率變得越來越高,數(shù)據(jù)的吞吐量

2022-07-04 09:21:58 6414

6414

明德?lián)P的JESD204B采集卡項(xiàng)目綜合上板后,可以使用上位機(jī)通過千兆網(wǎng)來配置AD9144和AD9516板卡,實(shí)現(xiàn)高速ad采集。最終可以在示波器和上位機(jī)上采集到設(shè)定頻率的正弦波。本文重點(diǎn)介紹JESD204B時鐘網(wǎng)絡(luò)。

2022-07-07 08:58:11 2424

2424

如何構(gòu)建您的JESD204B 鏈路

2022-11-04 09:52:11 3

3 理解JESD204B協(xié)議

2022-11-04 09:52:12 5

5 JESD204B:適合您嗎?

2022-11-07 08:07:23 0

0 JESD204B接口一般用在高速的AD和DA芯片上,用于傳輸采集到的數(shù)據(jù)。該接口相比LVDS可以減少大量的IO管腳,所以正在逐步取代LVDS接口(引用wp446-jesd204b.pdf)。

2022-12-22 09:45:18 3902

3902 大部分的ADC和DAC都支持子類1,JESD204B標(biāo)準(zhǔn)協(xié)議中子類1包括:傳輸層,鏈路層,物理層。在少部分資料中也會介紹含有應(yīng)用層,應(yīng)用層是對JESD204B進(jìn)行配置的接口,在標(biāo)準(zhǔn)協(xié)議中是不含此層,只是為了便于理解,添加的一個層。

2023-05-10 15:52:55 3056

3056

JESD204B規(guī)范是JEDEC標(biāo)準(zhǔn)發(fā)布的較新版本,適用于數(shù)據(jù)轉(zhuǎn)換器和邏輯器件。如果您正在使用FPGA進(jìn)行高速數(shù)據(jù)采集設(shè)計(jì),您會聽到新的流行詞“JESD204B”。與LVDS和CMOS接口相比,這一較新的版本具有顯著的優(yōu)勢,因?yàn)樗ǜ唵蔚牟季趾透俚囊_數(shù)。

2023-05-26 14:49:31 1468

1468

本文旨在提供發(fā)生 JESD204B 鏈路中斷情況下的調(diào)試技巧簡介

2023-07-10 16:32:03 3105

3105

電子發(fā)燒友網(wǎng)為你提供ADI(ADI)AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊,更有AD9207

2023-10-16 19:02:55

電子發(fā)燒友網(wǎng)站提供《JESD204B規(guī)范的傳輸層介紹.pdf》資料免費(fèi)下載

2023-11-28 10:43:31 0

0 電子發(fā)燒友網(wǎng)站提供《從JESD204B升級到JESD204C時的系統(tǒng)設(shè)計(jì)注意事項(xiàng).pdf》資料免費(fèi)下載

2024-09-21 10:19:00 6

6 能力更強(qiáng),布線數(shù)量更少。 本篇的內(nèi)容基于jesd204b接口的ADC和FPGA的硬件板卡,通過調(diào)用jesd204b ip核來一步步在FPGA內(nèi)部實(shí)現(xiàn)高速ADC數(shù)據(jù)采集,jesd204b協(xié)議

2024-12-18 11:31:59 2553

2553

實(shí)用JESD204B來自全球數(shù)據(jù)轉(zhuǎn)換器市場份額領(lǐng)導(dǎo) 者的技術(shù)信息、提示和建議

2025-05-30 16:31:21 0

0 LMK04828-EP 器件是業(yè)界性能最高的時鐘調(diào)理器,支持 JESD204B。

PLL2的14個時鐘輸出可配置為使用器件和SYSREF時鐘驅(qū)動7個JESD204B轉(zhuǎn)換器或其他邏輯器件

2025-09-12 16:13:11 831

831

LMK0482x 系列是業(yè)界性能最高的時鐘調(diào)節(jié)器,支持 JEDEC JESD204B。

PLL2 的 14 個時鐘輸出可配置為使用器件和 SYSREF 時鐘驅(qū)動 7 個 JESD204B

2025-09-15 10:10:11 848

848

電子發(fā)燒友App

電子發(fā)燒友App

評論