JESD204是基于SerDes($174.9800)的串行接口標準,主要用于數模轉換器和邏輯器件之間的數據傳輸,其最早的版本是JESD204A,現在是JESD204Bsubclass0,subclass1,subclass2.區別主要在于其對同步和鏈路間固定時差的測量。目前市場上比較多地數模轉換器接口是JESD204B subclass1.其最大傳輸速率可達12.5Gbps,支持多鏈路和多器件的同步以及固定時差的測量。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

ADI

+關注

關注

151文章

46118瀏覽量

279657 -

測量

+關注

關注

10文章

5686瀏覽量

116909 -

數模轉換器

+關注

關注

14文章

1317瀏覽量

85901

發布評論請先 登錄

相關推薦

熱點推薦

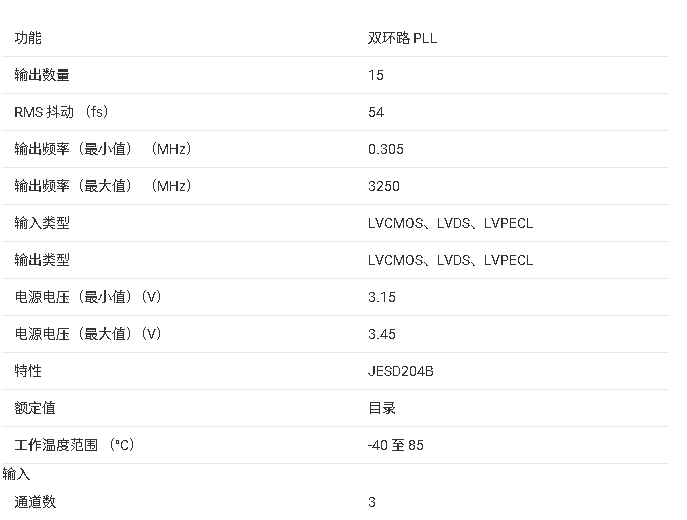

LMK04828 超低噪聲JESD204B兼容時鐘抖動清除器技術手冊

轉換器或其他邏輯器件。SYSREF 可以使用直流和交流耦合提供。不僅限于JESD204B應用,14 個輸出中的每一個都可以單獨配置為傳統時鐘系統的高性能輸出。

?LMK0482x系列超低噪聲JESD204B兼容時鐘抖動清除器技術文檔總結

轉換器或其他邏輯器件。SYSREF 可以使用直流和交流耦合提供。不僅限于JESD204B應用,14 個輸出中的每一個都可以單獨配置為傳統時鐘系統的高性能輸出。

LMK04616 超低噪聲低功耗JESD204B兼容時鐘抖動清除器總結

LMK0461x 器件系列是業界性能最高、功耗最低的抖動清除器,支持 JESD204B。16 個時鐘輸出可配置為使用器件和 SYSREF 時鐘驅動 8 個 JESD204B 轉換器或其他邏輯器件。第 17 個輸出可配置為提供來自 PLL2 的信號或來自外部 VCXO 的副

?LMK04828-EP 超低噪聲JESD204B兼容時鐘抖動清除器總結

。SYSREF 可以使用直流和交流耦合提供。不僅限于JESD204B應用,14 個輸出中的每一個都可以單獨配置為傳統時鐘系統的高性能輸出。

LMK04832 超低噪聲、3.2 GHz、15 輸出、JESD204B 時鐘抖動清除器技術手冊

JESD204B轉換器或其他邏輯器件。SYSREF 可以使用直流和交流耦合提供。不僅限于JESD204B應用,14 個輸出中的每一個都可以單獨配置為傳統時鐘系統的高性能輸出。

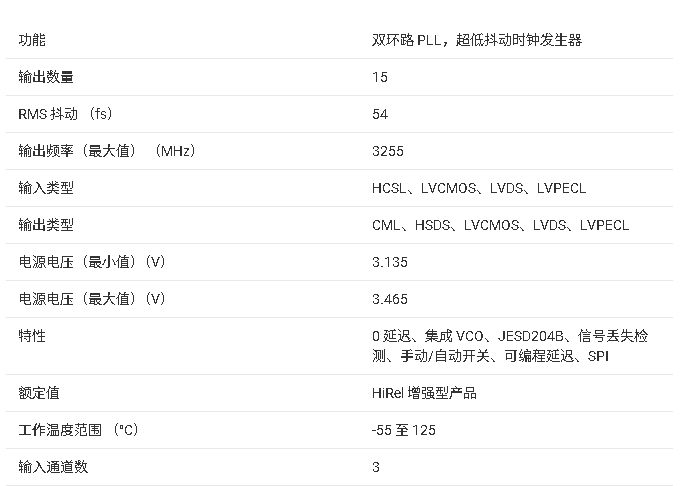

?LMK04368-EP 超低噪聲JESD204B/C雙環路時鐘抖動清除器總結

JESD204B/C 轉換器或其他邏輯器件。SYSREF 可以使用直流和交流耦合提供。不僅限于 JESD204B/C 應用,14 個輸出中的每一個都可以單獨配置為傳統時鐘系統的高性能輸出。

JEDSD204B標準verilog實現-協議演進

年發布)

發布時間

2006年(JEDEC標準JESD204)

2008年(JEDEC標準JESD204A)

2011年(JEDEC標準

發表于 09-05 21:18

替代HMC7044超低噪高性能時鐘抖動消除器支持JESD204B

1. 概述PC7044是一款高性能雙環路的整數時鐘抖動消除器,可以為具有并行或串(JESD204B型)接口的高速數據轉換器執行參考時鐘選擇和超低噪聲頻率的生成。 PC7044具有兩個整數

發表于 05-08 15:57

LTC6953具有11個輸出并支持JESD204B/JESD204C協議的超低抖動、4.5GHz時鐘分配器技術手冊

LTC6953 是一款高性能、超低抖動的 JESD204B/JESD204C 時鐘分配 IC。LTC6953 的 11 個輸出可配置為最多 5 個 JESD204B/JESD204

AD9680 JESD204B接口的不穩定會導致較大的電流波動,怎么解決?

AD采集芯片為AD9680-1000,時鐘芯片為AD9528。當 AD 采樣時鐘為 500MHz 時,jesd204B (串行線速 = 5 Gbps) 穩定。但是,當 AD 采樣時鐘為 800MHz

發表于 04-15 06:43

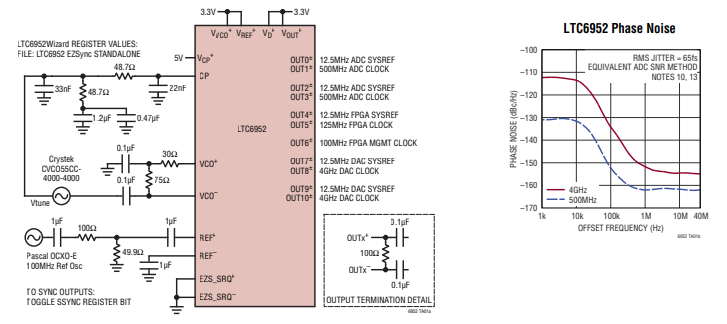

LTC6952具有11個輸出并支持JESD204B/JESD204C協議的超低抖動、4.5GHz PLL技術手冊

LTC6952 是一款高性能、超低抖動 JESD204B/C 時鐘生成和分配 IC。該器件包括一個鎖相環 (PLL) 內核,由基準分頻器、具有鎖相指示器的相位頻率檢波器 (PFD)、超低噪聲充電

JESD204B接口標準中的眼圖測量

JESD204B接口標準中的眼圖測量

評論