綜合(Synthesis)是指將RTL設計轉換為門級描述。Vivado開發套件中的綜合工具是一款時序驅動型、專為內存使用率和性能優化的綜合工具,支持System Verilog 2012

2020-12-29 14:07:42 7815

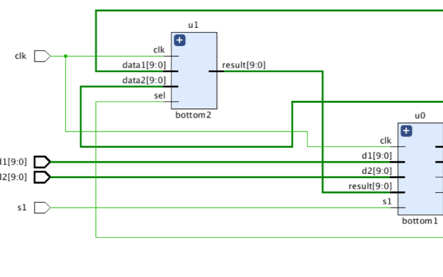

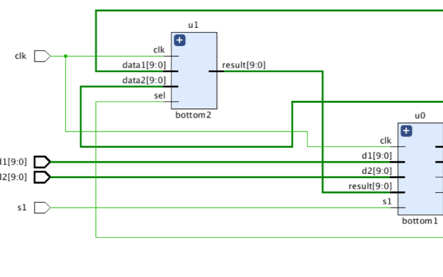

7815 設計技巧:在 Vivado Synthesis 中使用 SystemVerilog 接口連接邏輯

2019-07-02 12:03:07 13109

13109

X如何在XC8中包含“文件”工作?看起來XC8使用當前的工作目錄(正在編譯的文件目錄)作為搜索路徑的一部分,我期待使用標準的(GCC)方法來執行執行包含“文件”的文件的目錄。是否有一種方法來配置包含

2018-12-28 15:47:55

Verilog Synthesis Methodology

2012-08-15 15:31:23

17-345] A有效未找到功能'Synthesis'和/或設備'xc7z010'的許可證。請運行Vivado許可證管理器以獲取有關確定哪些功能和設備已獲得系統許可的幫助。解決方案:在Vivado許可證

2018-12-25 11:03:50

功能'Synthesis'和/或設備'xc7a35t'的有效許可證。請運行Vivado許可證管理器以獲取有關確定系統許可的功能和設備的幫助。解決方案:在Vivado License Manager中檢查

2018-12-26 11:30:48

你能否告訴我,自2014年4月以來Vivado 2016.3中對任何System Verilog功能的支持是否有所改變?你能告訴我這段代碼是否適用于2014.4?interface ibb_if

2020-05-14 08:57:57

你好,在Vivado 2016.4中運行Synthesis功能時,我收到了有效的許可證錯誤[Common 17-345]。請參閱附件和幫助。謝謝,Gursimar合成日志file.txt 2 KB

2019-01-04 11:22:27

嗨,在我的Vivado實現tcl腳本中,以下行導致錯誤:設置SRC_PATH ./input.............#Input the netlistread_edif $ SRC_PATH

2018-10-18 14:26:39

在ISE中可以設置狀態機安全模式 safe impementation模式,但是在Vivado中有沒有類似的設置?我現在一段代碼中可以跑到else,但是 偶爾會跑不到ifs_state_4這個狀態機。。有大佬知道是為什么么?

2020-11-09 15:25:41

: No error這個錯誤出現的原因是工程的路徑名太長,超過了80個字符。解決方法也很簡單,縮短工程路徑即可。Vivado在編寫和genvar有關的代碼時,出現的錯誤:[Synth 8-196

2021-07-31 09:09:20

在Vivado中進行HDL代碼設計,不僅需要描述數字邏輯電路中的常用功能,還要考慮如何發揮Xilinx器件的架構優勢。目前常用的HDL語言有三種。VHDL語言的優勢有:語法規則更加嚴格;在HDL

2020-09-29 10:08:57

…。(不同Vivado版本可能Write Tcl菜單位置會有不同,但是都在File菜單中)彈出的WriteProject to Tcl文件夾,在Output File中設置當前工程路徑,并輸入.tcl為后綴

2020-08-17 08:41:25

。除了手動技術映射之外,我還使用分層RLOC來管理這些模塊的放置,從而獲得快速且確定性的PAR運行,并從我的關鍵路徑中削減數十個百分點。在我的設計中,通常> 50%的基元是手工技術映射和/或手工放置

2018-11-06 11:40:10

使用的更多信息,請參閱(UG901)Vivado設計工具用戶指南:Synthesis(綜合)。 分析日志文件中的信息圖4是通過重定時提升邏輯水平的一個例子,該電路結構中有一個關鍵的路徑分為三個邏輯層

2019-03-14 12:32:05

vivado自己設置的工程目錄本身比較深,而文件路徑太深會導致某些奇怪的錯誤。這是windows系統本身的特性決定的,windows的路徑名不能超過260字節,所以大家設計的時候一定注意路徑名長度

2019-09-11 11:52:42

ADVANCED ASIC CHIP SYNTHESIS文件大小:16MUNIX is a registered trademark of UNIX Systems Laboratories

2009-12-18 11:16:27

searth path 怎么設置呢?還有一個問題是include options和file searth path都有上下兩個可以添加路徑的窗口,這兩個窗口有什么不同呢?謝謝大家的回答~~

2018-06-21 10:27:12

在UE中include都需要時絕對路徑,有沒有辦法可以設置成相對路勁呢

2013-06-14 22:15:35

nWave(ctrl+w)中報signal路徑錯誤,nTrace中顯示信號路徑是xx.xx.xx.signal1;而nWave中信號路徑是xx/xx/xx/signal1.單獨使用Verilog語言或者

2016-01-10 18:37:53

工程才可以。 但如果需要讀取或寫入工程本身的文件夾之外的txt文件中,就涉及到路徑問題,在verilog中使用這個下面的系統任務命令 $readmemb("filename"

2016-06-21 13:52:59

1,創建工程打開Vivado軟件,點擊新建工程。根據向導創建工程,以下以Xilin 7020開發板為例,進行介紹。注意:I,設置工程的名稱,在這個步驟中可以勾選“Create project

2023-04-05 23:21:24

enumdefine.sv為Verilog Header即可。同樣,在Vivado中可以通過下面的方式設置宏定義:Add synthesis option "-verilog

2022-07-08 16:13:01

Header.

在config.v中增加宏定義: `define FPGA_SOURCE

將tb_top.v設置為頂層, 并添加如上圖讀入.verilog文件的路徑,保存文件。

請問胡哥,上述步驟有出現錯誤或疏漏嗎

2023-08-16 08:20:13

vivado中synthesis通過,implement通過,但是在編譯simulation的時候報錯:[USF-XSim-62] 'compile' step failed with error

2017-07-05 10:46:33

為global include ,并將文件類型改為 Verilog Header.

在config.v中增加宏定義: `define FPGA_SOURCE

8.將tb_top.v設置為頂層

2025-11-05 13:56:02

只想看模塊D的波形,那么該fsdb波形,能夠在仿真環境B中查看了嗎?當然,在仿真環境B中,能夠直接打開該fsdb波形,但是不能將模塊D的代碼和波形中模塊D的波形進行對應,因為他們的層次路徑不一樣。所以

2022-04-02 17:30:33

https://www.rvmcu.com/community-topic-id-386.html

以上鏈接為如何生成.verilog,并在VIVADO中生成波形的例子。我們在實踐過程中,發現了兩個

2025-10-27 06:41:49

a0 -8

為例

獲取相應的二進制碼將其轉換為16進制導入vivado,方法就是將代碼文件修改為.verilog文件并存入蜂鳥的tb文件夾,在vivado的tb中修改測試用例路徑即可進行仿真。

得到結果

2025-10-24 06:31:26

,設置為global include

設置成功后:

第二步:將其再設置為verilog header文件

設置成功后:

最終run implementation成功后顯示:

2025-10-27 06:20:05

代碼中的語法錯誤以及代碼行為的正確性,其中不包括延時信息。如果沒有實例化一些與器件相關的特殊底層元件的話,這個階段的仿真也可以做到與器件無關。因此在設計的初期階段不使用特殊底層元件即可以提高代碼的可讀性

2018-01-24 11:06:12

2017.2>Vivado 2017.22)點擊‘Create Project’,或者單擊File>New Project創建工程文件3)將新的工程項目命名為‘lab3’,選擇工程保存路徑,勾選

2017-12-20 10:23:11

嗨朋友們,我正在嘗試使用塊內存生成器訪問存儲在ROM中的.coe文件。我想為此編寫一個verilog代碼。如何以verilog代碼訪問存儲在BRAM中的像素值?提前致謝。以上來自于谷歌翻譯以下為原文

2019-02-26 09:48:33

大家好,我試圖在verilog文件中將命令傳遞給系統。 (在最初的開始循環中)我嘗試使用$ system命令行。它現在處于verilog標準,但它似乎不適用于vivado。誰知道怎么做?這是我想要

2020-05-22 15:23:42

當我構建項目時,我得到了“include file”錯誤。我發現修復這些錯誤的唯一方法是指定包含文件的完整路徑或相對路徑。如何修改包含文件的搜索路徑,從而不必編輯源代碼“include”語句

2019-07-05 09:32:44

是5位模式。我決定編寫一個代碼來生成值,而不是在LCD上看到它我會創建一個文本文件并將結果寫入該文件。任何人都可以告訴我如何在verilog中編寫代碼,這將允許我給出一個特定的頻率,以便我可以繞過信號發生器的使用并在代碼中輸入各種頻率值并獲得不同的結果?謝謝

2019-10-29 09:40:37

a0 -8

為例

獲取相應的二進制碼將其轉換為16進制導入vivado,方法就是將代碼文件修改為.verilog文件并存入蜂鳥的tb文件夾,在vivado的tb中修改測試用例路徑即可進行仿真。

得到

2025-10-24 06:46:36

的便捷性和實用性不用說,接下來我們就來盤點一下使用Notepad++在編寫verilog代碼時要配置哪些!第一 括號、雙引號自動補全點擊設置——首選項,如圖所示在彈出的窗口中選擇自動完成,將下面需要

2017-11-18 09:44:25

嗨,我認為這仍然可以作為xilinx問題(而不是synplify pro問題),因為我在xilinx ISE 14.5中使用synplify pro僅用于合成。所以這里......我在verilog

2019-03-12 09:08:41

您好,我正在為Vivado 2015.3課程做一個項目。該項目是邊界掃描測試。我編寫了所有VHDL代碼并嘗試實現。但是,實施還沒有發生。我一直得到錯誤:[Synth 8-4169]使用條款中的錯誤

2019-04-15 12:38:48

大家早上好,我們嘗試編寫用于將FPGA的IO設置為JTAG模式的verilog代碼。請仔細閱讀下面附帶的verilog,測試臺代碼。我們在模擬中沒有得到正確的輸出。 D_out正在成為高阻抗。任何人都可以幫我解決這個問題嗎?問候Vimalasimulation.wcfg 6 KB

2020-03-23 09:04:29

綜合,結果存儲在.DCP文件中我做了第二個VIVADO綜合后項目......我從第一個VIVADO項目添加了DCP文件,我也添加了NGC文件...但每當我運行實現我得到“頂部找不到文件。請添加一個頂級

2019-03-22 07:46:30

大家好,使用UCF文件中的ISE,我習慣于在輸入焊盤和第一個觸發器之間的信號上設置maxdelay約束,特別是在總線信號上,以確保總線的所有信號具有大致相同的傳播時間。使用Vivado,我無法在

2018-10-25 15:17:18

重新打開ISE項目時,它失敗了。有沒有辦法在ISE中設置Include目錄?謝謝,保羅以上來自于谷歌翻譯以下為原文Hi, I am running ISE 10.1.03 and am trying

2018-10-12 14:13:51

,希望能帶著大家一步一個腳印,腳踏實地的在Vivado和Modelsim兩個主流的工具中完成Verilog的設計和驗證。FPGA或Verilog的視頻教程有很多了,但是能下功夫“陪著”初學者一行一行敲代碼

2020-04-22 09:20:48

誰能給個verilog中的.vt格式文件的建立路徑,比如要建一個.v文件的路徑是:quartus/new/Verilog hdl file;再比如要建一個時序文件,路徑是:quartus/new

2016-05-17 21:59:24

我正在使用Eclipse,我想將MPLAB X IDE編譯器與它結合起來。請幫忙。在Eclipse中需要設置哪些路徑和哪些路徑? 以上來自于百度翻譯 以下為原文 I am using

2019-06-27 08:14:57

我發現vivado可以改變工具中的featuresaboutSynthesis - settings - Synthesis。但我在ISE中找不到類似的東西。如果有人知道設置在哪里。非常感謝你!

2019-08-12 10:13:33

`include "define_file.v" 是不行的,要使用絕對路徑,如 `include "F:/110503_Test/rtl

2014-08-27 00:49:38

Verilog HDL Synthesis (A Practical Primer)

2009-02-12 09:36:24 40

40 ref ddr sdram verilog源代碼

File/Directory Description

2009-06-14 08:48:01 82

82 ref-sdr-sdram-verilog代碼

SDR SDRAM Controller v1.1 readme.txt

This readme file for the SDR SDRAM

2009-06-14 08:50:44 33

33 電子發燒友網核心提示: 本例程是Verilog HDL源代碼:關于基本組合邏輯功能中雙向管腳的功能實現源代碼。 Verilog HDL: Bidirectional Pin This example implements a clocked bidirectional pin in Verilog HDL.

2012-10-15 11:28:26 1808

1808 本文簡單介紹在使用Verilog HDL語言時文件的調用問題之include使用方法介紹及舉例說明,詳見本文...

2013-01-24 14:40:42 7391

7391

verilog_代碼資料,非常實用的代碼示例。

2016-02-18 15:00:10 38

38 《XDC約束技巧》系列中討論了XDC約束的設置方法、約束思路和一些容易混淆的地方。我們提到過約束是為了設計服務,寫入Vivado中的XDC實際上就是用戶設定的目標 ,Vivado對FPGA設計的實現

2017-11-17 18:03:55 39395

39395

Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級到Vivado的信心。本文介紹了Tcl在Vivado中的基礎應用,希望起到拋磚引玉的作用,指引使用者在短時間內快速掌握相關技巧,更好地發揮Vivado在FPGA設計中的優勢。

2017-11-18 03:52:01 5363

5363

本文檔內容介紹了基于Java File中renameTo的介紹和使用說明及源代碼,供參考。

2018-03-12 16:06:22 0

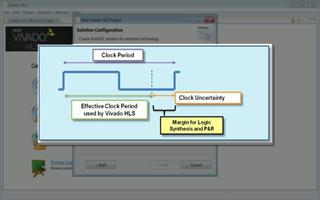

0 Xilinx公司講述:Getting Started with Vivado High-Level Synthesis

2018-06-04 13:47:00 4478

4478

如何為您的NFV應用設置DPDK

2018-11-12 06:37:00 3565

3565 了解如何使用2014.1中引入的新激活許可為Vivado工具生成許可證。

另外,了解Vivado 2014.1中的許可更改如何影響您,以及如何在激活客戶端中使用新的Vivado License Manager

2018-11-22 07:10:00 3623

3623 下圖紅圈的英文是這樣描述的:temporary directory paths exceeds 146 characters。中文意思是說,臨時文件路徑超過146個字符。意思就是編譯過程中

2019-03-30 09:39:44 8166

8166 中國大學MOOC

本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-08-06 06:12:00 4201

4201

在vivado中設置modelsim(即第三方仿真工具)的安裝路徑。在vivado菜單中選擇“Tools”——》“Options.。。”,選擇“General”選項卡,將滾動條拉倒最底部,在

2021-04-15 10:10:49 6544

6544

中網表列表示例 ? 在vivado集成環境中,網表時對設計的描述,如網表由單元(cell)、引腳(pin)、端口(port)和網絡(Net)構成。下圖是一個電路的網表結構: 電路的網表結構 (1)單元

2021-05-14 10:46:53 5414

5414

到另一個文件中。它通常用于包括全局項目定義,而無需在多個文件中重復相同的代碼。另一個用例是將代碼的一部分插入模塊,如以下示例所示: // file test_bench_top.v

2021-05-23 14:51:51 2172

2172 Vivado 的XDC設置輸出延時 Vivado 的XDC設置輸出延時,用于輸出伴隨時鐘和數據的,數據是由系統時鐘125M驅動,伴隨時鐘是由125M經過Pll相位移動-90度。 設置輸出時鐘

2021-06-09 17:28:01 5014

5014

在Vivado中分析時序問題的原因(不在本篇中詳細討論), 并根據時序失敗的原因調整Vivado各個步驟的選項。有時我們也需要調整Vivad

2021-07-28 10:12:47 2858

2858

本篇文章來自賽靈思高級工具產品應用工程師 Hong Han. 本篇博文將繼續介紹在Vitis中把Settings信息傳遞到底層的Vivado. 對于Vivado實現階段策略的指定

2021-08-13 14:35:56 4953

4953 符。 Vivado Synthesis Hangs/StopsVivado在綜合時,如果顯示一直在運轉,但不再輸出任何log信息時,檢查一下工程路徑是否包含了特殊字符“”。因為“”字符在Tcl腳本里是變量置換

2021-09-12 15:15:19 7447

7447 FPGA CPLD中的Verilog設計小技巧(肇慶理士電源技術有限)-FPGA CPLD中的Verilog設計小技巧? ? ? ? ? ? ? ? ?

2021-09-18 16:49:18 37

37 的完整 Verilog 代碼 。 在這個FPGA Verilog項目中,一些簡單的處理操作都是在Verilog中實現的,比如反相、亮度控制和閾值操作。圖像處理操作由“parameter.v”文件選擇

2021-09-23 15:50:21 7240

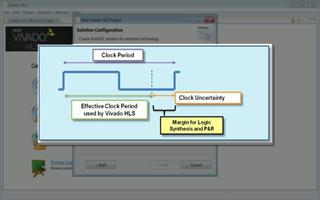

7240 在整個流程中,用戶先創建一個設計 C、C++ 或 SystemC 源代碼,以及一個C的測試平臺。通過 Vivado HLS Synthesis 運行設計,生成 RTL 設計,代碼可以是 Verilog,也可以是 VHDL。

2022-06-02 09:48:17 8680

8680 中的file_path就是獲取的文件所在路徑。 代碼如下: import os file=self.openfile= QFileDialog.getOpenFileNames() file

2022-06-20 21:05:14 4364

4364 Vivado IPI (IP Integrator)提供了直觀的模塊化的設計方法。用戶可以將Vivado IP Catalog中的IP、用戶自己的RTL代碼、或者用戶已有的BD文件添加到IP Integrator中構成Block Design,設計更復雜的系統,如下圖所示。

2022-07-15 11:39:12 2894

2894 全局綜合(Global Synthesis)全局綜合意味著整個設計在一個Synthesis Design Run流程中完成,這樣會帶來幾個好處。

2022-07-15 11:39:42 3171

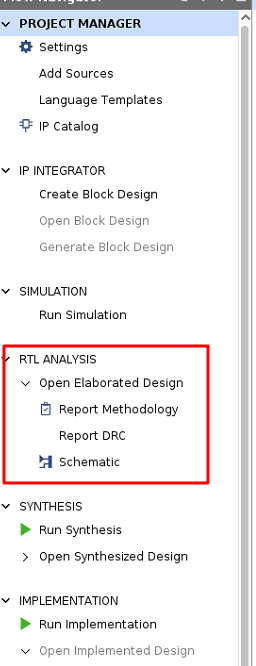

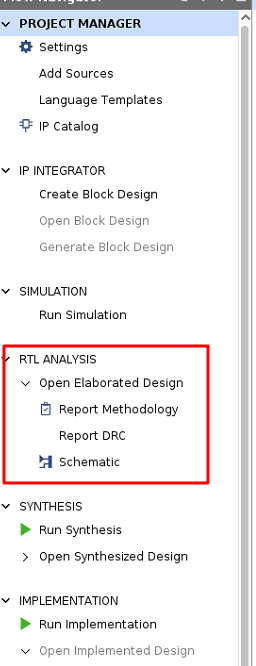

3171 在Vivado的界面中,有個RTL ANALYSIS->Open Elaborated Design的選項,可能很多工程師都沒有使用過。因為大家基本都是從Run Synthesis開始的。

2022-10-24 10:05:03 2251

2251 當使用Codeviser調試系統映像文件時,經常遇到映像編譯使用的源代碼路徑和調試時使用的源代碼路徑不一致的情況,調試這樣的映像時,經常會發生找不到源代碼的情況,這時就需要設置映像對應的源代碼路徑,以便映像引用的是正確的源代碼。

2022-11-15 11:07:36 2049

2049 )和連線(wire)息息相關。Verilog便具有將ASM圖表和電路框圖用計算機語言表達的能力,本文將講述Vivado綜合支持的Verilog硬件描述語言; Verilog提供了行為化和結構化兩方面的語言結構,描述設計對象時可以選擇高層次或低層次的抽象等級。使用V

2022-12-29 10:30:09 7505

7505 在vivado中的Settimg中,Target language可以選擇verilog,也可以選擇vhdl

2023-03-30 10:37:02 1676

1676 在Vivado的界面中,有個RTL ANALYSIS->Open Elaborated Design的選項,可能很多工程師都沒有使用過。因為大家基本都是從Run Synthesis開始的。

2023-05-05 16:00:18 2163

2163

我們在上一篇文章中已經看到了如何使用程序塊(例如 always 塊來編寫按順序執行的 verilog 代碼。

我們還可以在程序塊中使用許多語句來控制在我們的verilog設計中信號賦值的方式

2023-05-11 15:37:36 6517

6517

本文主要介紹Vivado布線參數設置,基本設置方式和vivado綜合參數設置基本一致,將詳細說明如何設置布線參數以優化FPGA設計的性能,以及如何設置Vivado壓縮BIT文件。

2023-05-16 16:40:45 6174

6174

如果你正在使用Vivado開發套件進行設計,你會發現綜合設置中提供了許多綜合選項。這些選項對綜合結果有著潛在的影響,而且能夠提升設計效率。為了更好地利用這些資源,需要仔細研究每一個選項的功能。本文將要介紹一下Vivado的綜合參數設置。

2023-05-16 16:45:50 5589

5589

本文主要介紹ROM和RAM實現的verilog代碼版本,可以借鑒參考下。

2023-05-16 16:57:42 3110

3110 Vivado 軟件提供了HDL編寫中常用的示例,旨在幫助初學者更好地理解和掌握HDL編程,這里分享一下verilog代碼示例。

2023-05-16 16:58:06 1830

1830 電子發燒友網站提供《Verilog中Pmod ALS的SPI接口代碼.zip》資料免費下載

2023-06-15 09:32:52 0

0 關于仿真里的后門訪問,之前的文章《三分鐘教會你SpinalHDL仿真中的后門讀寫》中有做過介紹,其針對的都是針對以SpinalHDL中的代碼進行的后門訪問。今天來看看當封裝了Verilog BlackBox時,在SpinalHDL仿真中如何進行后門訪問Verilog代碼。

2023-07-15 10:22:02 1515

1515

什么是Logic Synthesis?Logic Synthesis用于將輸入的高級語言描述(如HDL、verilog)轉換為門級電路的網絡表示。

2023-10-24 15:56:04 2551

2551

Include File(inc文件)是Vector Logger Suite(VLS)中使用LTL代碼片段的關鍵機制。通過Include File,用戶可以在LTL代碼中靈活定義參數、觸發

2025-12-30 09:44:14 102

102

電子發燒友App

電子發燒友App

評論