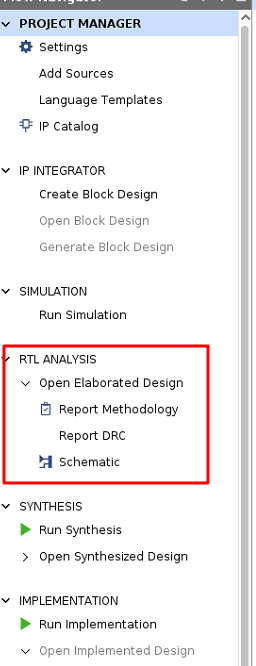

在Vivado的界面中,有個RTL ANALYSIS->Open Elaborated Design的選項,可能很多工程師都沒有使用過。因為大家基本都是從Run Synthesis開始的。

elaborate可以翻譯為“詳盡解析”,就是將RTL源代碼翻譯轉換成對應的電路。

elaborate可以翻譯為“詳盡解析”,就是將RTL源代碼翻譯轉換成對應的電路。

有同學會問,這不是Synthesis做的工作嗎?

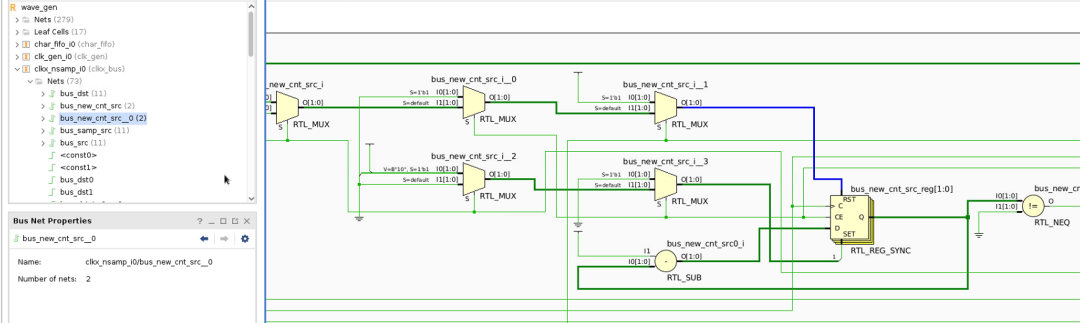

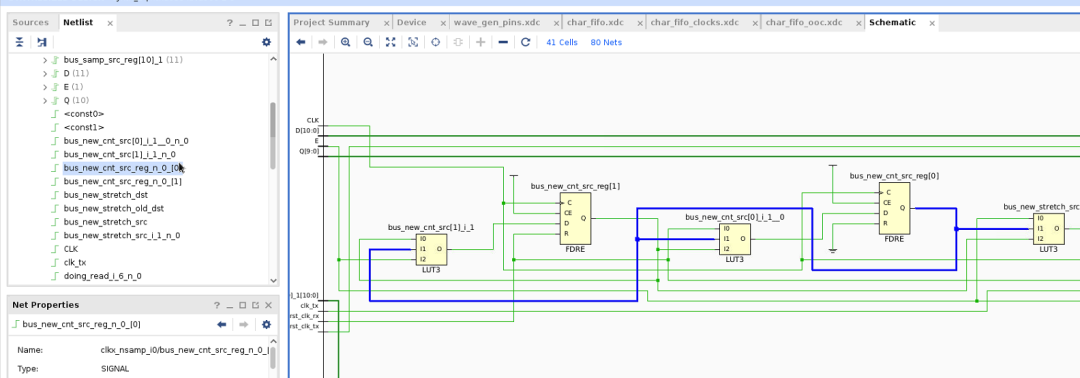

我們可以來比較一下Elaborate和Synthesis后的Schematic就很直觀了:

Elaborated Design:

image-20221023165430449

Synthesisd Design:

image-20221023165346017

可以看出,Elaborated Design里面的電路是單純的對RTL源代碼的解析,到了Synthesisd Design,則可以看到Xilinx的具體的庫單元,比如LUT3、FDRE等,都是在Xilinx FPGA中真實存在的。

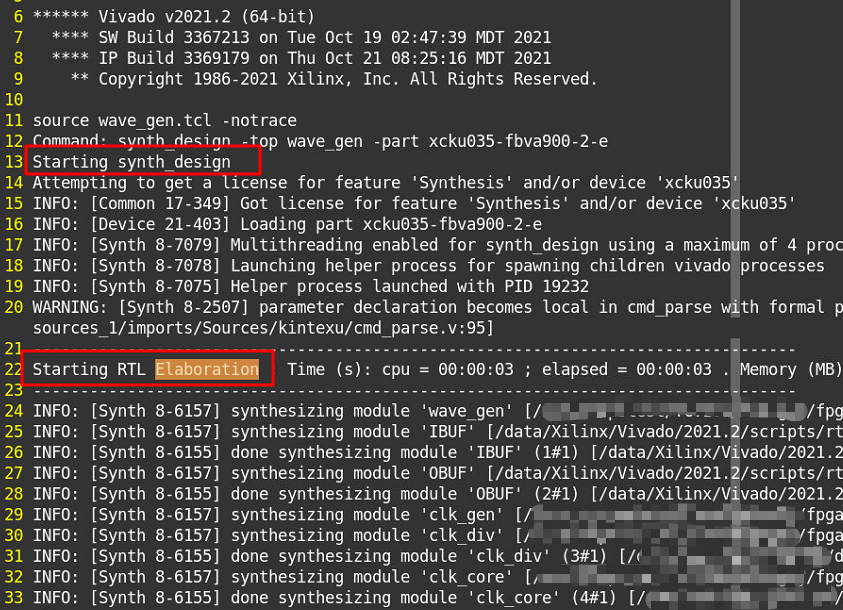

其實在綜合的log文件,看到Elaborate的存在,綜合的第一步就是先進行Elaborate:

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

RTL

+關注

關注

1文章

395瀏覽量

62786 -

design

+關注

關注

0文章

165瀏覽量

47634 -

Vivado

+關注

關注

19文章

859瀏覽量

71278

發布評論請先 登錄

相關推薦

熱點推薦

基于linux系統實現的vivado調用VCS仿真教程

在linux系統上實現vivado調用VCS仿真教程 作用:vivado調用VCS仿真可以加快工程的仿真和調試,提高效率。 前期準備:確認安裝vivado軟件和VCS軟件 VCS軟件最

Vivado 2017.1和Vivado 2016.4性能對比分析

。總體而言,Vivado 2017.1比Vivado2016.4給出了更好的效果。雖然在測試1中的結果有些相似,但是Vivado2017.1從測試2和3

Tcl在Vivado中的基礎應用

Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級到Vivado的信心。本文介紹了Tcl在Vivado中的基礎應用,希望起到拋磚引玉的

發表于 11-18 03:52

?5427次閱讀

Vivado使用誤區與進階——在Vivado中實現ECO功能

關于Tcl在Vivado中的應用文章從Tcl的基本語法和在Vivado中的應用展開,介紹了如何擴展甚至是定制FPGA設計實現流程后,引出了一個更細節的應用場景:如何利用Tcl在已完成布

發表于 11-18 18:26

?5922次閱讀

如何在Vivado中應用物理優化獲得更好的設計性能

物理優化是Vivado實現流程中更快時序收斂的重要組成部分。

了解如何在Vivado中應用此功能以交換運行時以獲得更好的設計性能。

Vivado 2014.1中的許可和激活概述

了解如何使用2014.1中引入的新激活許可為Vivado工具生成許可證。

另外,了解Vivado 2014.1中的許可更改如何影響您,以及如何在激活客戶端中使用新的

在Vitis中把Settings信息傳遞到底層的Vivado

本篇文章來自賽靈思高級工具產品應用工程師 Hong Han. 本篇博文將繼續介紹在Vitis中把Settings信息傳遞到底層的Vivado. 對于Vivado實現階段策略的指定

Vivado中的Elaborate是做什么的?

在Vivado的界面中,有個RTL ANALYSIS->Open Elaborated Design的選項,可能很多工程師都沒有使用過。因為大家基本都是從Run Synthesis開始的。

Tcl在Vivado中的應用

Xilinx的新一代設計套件Vivado相比上一代產品 ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言 XDC 以及腳本語言 Tcl 的引入則成為

如何在Vivado中添加時序約束呢?

今天介紹一下,如何在Vivado中添加時序約束,Vivado添加約束的方法有3種:xdc文件、時序約束向導(Constraints Wizard)、時序約束編輯器(Edit Timing Constraints )

Vivado時序約束中invert參數的作用和應用場景

在Vivado的時序約束中,-invert是用于控制信號極性的特殊參數,應用于時鐘約束(Clock Constraints)和延遲約束(Delay Constraints)中,用于指定信號的有效邊沿或邏輯極性。

簡述Vivado中的Elaborate的作用

簡述Vivado中的Elaborate的作用

評論