用于早期軟件開發和調試的虛擬平臺可能包含由SystemC TLM模型組成的子系統。得益于它們的快速執行,為創建硬件設計而開發的模型也可用來加速軟件設計。

2020-09-05 12:23:17 6182

6182

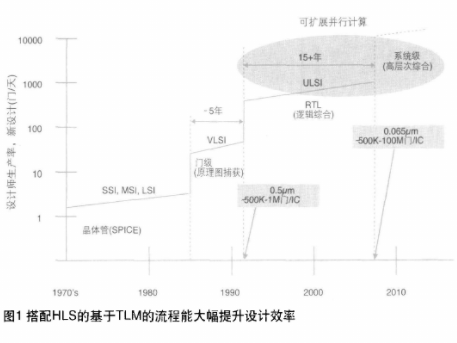

建立芯片模型是在早期進行芯片架構決策的有效方法,通過建模不僅可以對芯片的性能做出分析,還可以在硬件沒有完成之前開發軟件,不僅提高了產品成功率,而且縮短了研發周期。設計人員早期采用C/C++語言進行

2018-12-05 07:43:00 5969

5969

Reconfigurable Cell Array)結構測試FPGA邏輯單元PLB(Programmable Logic Block)的方法,該方法對邏輯單元PLB 進行了分類、分階段的測試,同時進行電路模擬實驗。

2018-11-28 09:02:00 5013

5013

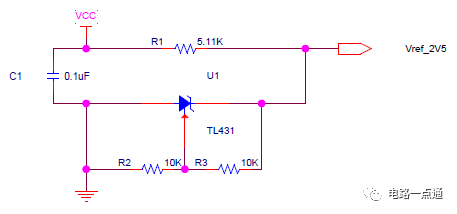

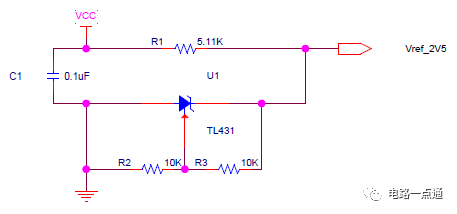

本文將引導您采用極簡/簡單的方法進行開關電源設計,并介紹幾種利用 FPGA 資源和最小模擬電路發電的方法。

2023-02-20 09:14:50 1421

1421

FPGA設計流程是利用EDA開發軟件和編程工具對FPGA芯片進行開發的過程。FPGA的設計流程如上圖所示:包括設計定義、代碼實現、功能仿真、邏輯綜合、前仿真、布局布線、后仿真和板級調試等步驟!

2023-04-04 10:29:51 3088

3088 開發和驗證 FPGA IP 不僅僅是編寫 HDL,而是需要更多的思考。讓我們來看看如何做吧!

2023-10-17 09:57:19 1911

1911

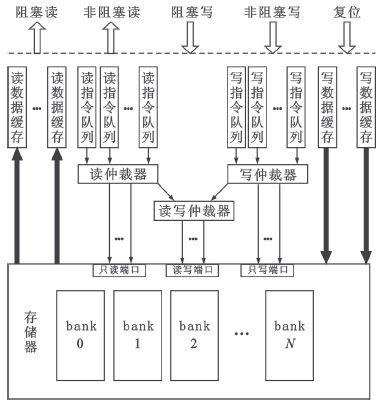

本文介紹如何利用FPGA和DMA技術處理來自AD9280和AD9708 ADC的數據。首先,探討了這兩種ADC的特點及其與FPGA的接口兼容性。接著,詳細說明了使用Xilinx VIVADO環境下

2025-07-29 14:12:22 4847

4847 FPGA開發過程中,利用免費的IP內核可以顯著提高開發效率,減少設計成本。以下是一些關于如何利用免費IP內核進行FPGA開發的建議:

選擇適合的IP內核:首先,需要明確項目的需求和目標,然后選擇與之

2024-04-28 09:41:04

,可以嘗試對IP軟核進行優化。例如,可以調整參數配置、優化布局布線、修改代碼等。

在調試過程中,可以利用FPGA開發工具提供的調試功能,如邏輯分析儀、波形查看器等,幫助定位問題和解決問題。

知識產權保護

2024-05-27 16:13:24

開發流程FPGA的設計流程就是利用EDA開發軟件和編程工具對FPGA芯片進行開發的過程。FPGA的開發流程一般如圖2所示,包括電路設計、設計輸入、功能仿真、綜合優化、綜合后仿真、實現、布線后仿真、板級

2017-01-10 15:50:15

單元、大容量處理器、吉比特收發器、混合邏輯、IP以及原有的設計部分組成。相應的FPGA規模大都在百萬門以上,適合于許多領域,如電信、計算機等行業。 系統設計方法是SOC常用的方法學,其優勢在于,可進行

2015-11-30 15:28:41

USB OTG的工作原理是什么?IP設計原理是什么?如何進行IP模塊設計?USB OTG IP核有什么特性?如何對USB OTG IP核進行FPGA驗證?

2021-04-27 06:44:33

使用默認應用程序模擬后,您可以:

·通過修改參考平臺測試臺和相應的構建系統對其進行更改,以包括、實例化和連接新的或更新的模型。

·復制和移植作為參考平臺一部分的SystemC周期模型,并將其構建到您自己的定制平臺中。

·修改ARM參考平臺,方法是將您自己的SystemC模型類添加到參考平臺

2023-08-23 07:21:54

SystemC是什么?SystmeC的作用是什么?SystemC的用途是什么?

2021-06-21 07:37:41

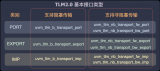

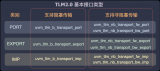

TLM 2.0的AMBA-PV擴展(AMBA-PV)將AMBA?總線映射到TLM 2.0之上。

其主要特點是:

?本課程專注于程序員視圖(PV),專注于高級、功能準確的事務建模。低電平信號,例如信道

2023-08-10 06:56:50

ARM系統C周期模型直接從RTL代碼編譯而來。

SystemC模型包裝器以源代碼形式提供,以支持對任何符合SystemC 2.3.1標準的模擬器進行編譯。

您可以將這些模型直接集成到任何符合IEEE

2023-08-12 07:02:07

SystemVerilog 的VMM 驗證方法學教程教材包含大量經典的VMM源代碼,可以實際操作練習的例子,更是ic從業人員的絕佳學習資料。SystemVerilog 的VMM 驗證方法學教程教材[hide][/hide]

2012-01-11 11:21:38

( ? :)嗎?或者說:systemc中三目運算符( ? :)是不可綜合的?[groupid=554]FPGA[/groupid]

2014-08-29 16:11:21

`本視頻是Combat FPGA開發板的配套視頻課程,本章節課程主要介紹如何利用Gowin FPGA實現MAC協議開發。內容包括MAC協議概述,MAC幀結構,以及Gowin以太網Mac IP使用簡介

2021-05-06 15:08:59

本視頻是Combat FPGA開發板的配套視頻課程,本章節課程主要介紹MiPi-DPHY的基礎知識、MiPi-DPHY的IP core的調用以及MiPi-DPHY的仿真。課程資料包含豐富

2021-05-06 15:23:20

core、常用的高云IP core有哪些、如何配置和調用IP core以及高云關于IP core介紹的官方文檔,幫助用戶快速掌握高云IP core的使用。本視頻教程利用Runber開發板進行講解,視頻課程注重基礎知識和設計思路的講解,幫助初學者理解和掌握FPGA設計。

2021-04-12 16:45:11

本合集為系列視頻教程利用Runber FPGA開發板進行講解,包含是視頻及代碼資料下載。視頻課程注重基礎知識和設計思路的講解,幫助初學者理解和掌握FPGA設計。【Runber FPGA開發板】配套

2021-04-13 14:01:49

摘要針對FFT算法基于FPGA實現可配置的IP核。采用基于流水線結構和快速并行算法實現了蝶形運算和4k點FFT的輸入點數、數據位寬、分解基自由配置。使用Verilog語言編寫,利用ModelSim

2019-07-03 07:56:53

隨著系統級芯片技術的出現,設計規模正變得越來越大,因而變得非常復雜,同時上市時間也變得更加苛刻。通常RTL已經不足以擔當這一新的角色。那么我們就需要弄明白,什么是IP開發及FPGA建模?

2019-08-01 07:41:01

核的分類和特點是什么?基于IP核的FPGA設計方法是什么?

2021-05-08 07:07:01

什么是FPGA (現場可編程門陣列)?如何保護系統的關鍵功能和知識產權(IP)?

2019-08-26 08:25:51

隨著系統級芯片技術的出現,設計規模正變得越來越大,因而變得非常復雜,同時上市時間也變得更加苛刻。通常RTL已經不足以擔當這一新的角色。上述這些因素正驅使設計師開發新的方法學,用于復雜IP(硬件和軟件)以及復雜系統的驗證。

2019-08-12 07:01:58

如何利用庫函數的方法進行開發使用STM32外設的基本流程呢?如何驅動平臺上的用戶指示燈呢?

2022-02-25 07:38:22

ASIC驗證能夠采用的主要技術是什么?如何利用現成FPGA開發板進行ASIC原型開發?

2021-05-08 07:51:04

。很多人問我如何將SystemC綜合和編譯為可以下載的CPLD/FPGA的比特文件或者綜合為ASIC網表,我的回答是用SystemC做RTL設計還為時過早。可以想象將來可能將SystemC的行為級的描述

2012-03-01 11:30:19

請教各位大佬,UVM是基于sv的驗證方法學,如果采用systemc語言編程,如何實現?

2019-11-07 15:30:16

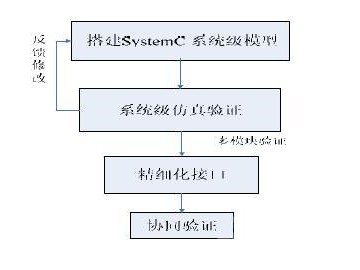

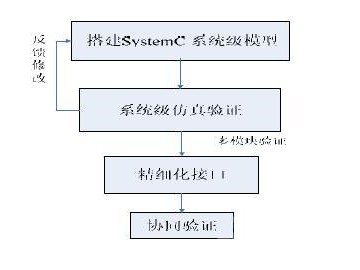

基于SystemC/TLM方法學的IP開發及FPGA建模

2021-04-29 06:54:48

隨著系統級芯片技術的出現,設計規模正變得越來越大,因而變得非常復雜,同時上市時間也變得更加苛刻。通常RTL已經不足以擔當這一新的角色。上述這些因素正驅使設計師開發新的方法學,用于復雜IP(硬件和軟件)以及復雜系統的驗證。

2019-08-15 06:34:17

本文根據FPGA的結構特點,圍繞在FPGA上設計實現八位微處理器軟核設計方法進行探討,研究了片上系統的設計方法和設計復用技術,并給出了指令集和其調試方法,提出了一種基于FPGA的微處理器的IP的設計方法。

2021-04-29 06:38:37

億海微6系 EQ6HL45型可編程邏輯芯片開發平臺采用核心板加擴展板的模式,方便用戶對核心板的二次開發利用,為前期驗證和后期應用提供了可能。相信這樣的一款產品非常適合從事FPGA開發的工程師、科研人員等群體。

2022-02-16 17:06:51

。EasyGo FPGA Solver 的優點在于,能夠將Simulink的圖形化模型利用解算器軟件轉化成FPGA執行的代碼,而不需要進行FPGA的編譯

2022-05-19 09:21:43

IC 技術已發展到SoC 階段,系統級設計、仿真和驗證已成為IC 設計面臨的巨大挑戰。SystemC 是新興的系統級設計語言,為復雜系統的設計與驗證提供了解決方案。本文介紹SystemC 的特點

2009-05-18 13:44:58 28

28 Systemc From The Ground Up:The first question any reader should ask is “Why this book?” We

2009-07-10 17:27:57 0

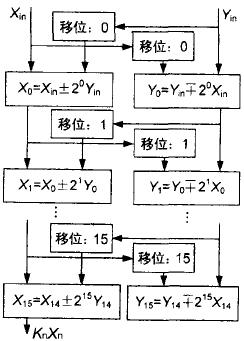

0 事務級(Transaction-Level,TL)建模是SystemC 中提出的一種新型高層次建模方法,以CoCentric System Studio(CCSS)作為SystemC 仿真工具,以一個IP 路由系統為建模實例,分析了事務級建模

2009-07-30 15:27:27 24

24 基于FPGA 視頻α 混合IP 的設計(合肥工業大學微電子設計研究所 485 信箱 郵編:230009)摘要:本文闡述了視頻α 混合IP 的設計和實現方法。為了改善電路的性能, 在設計中不僅

2009-12-14 11:16:23 13

13 利用面向對象技術進行可配置的FFT IP 設計與實現摘要:為了縮短產品上市時間并降低設計成本,IP 復用已經成為IC設計的重要手段。以往利用RTL 代碼編寫的IP,往往是針對特定應

2010-07-04 11:42:13 8

8 數字專用集成電路設計中的SystemC建模驗證方法

2010-07-17 16:36:23 31

31 利用FFT IP Core實現FFT算法

摘要:結合工程實踐,介紹了一種利用FFT IP Core實現FFT的方法,設計能同時對兩路實數序列進行256點FFT運算,并對轉換結果進行求

2008-01-16 10:04:58 8042

8042

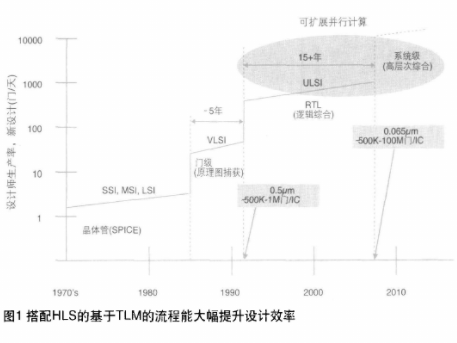

Cadence推出首個TLM驅動式設計與驗證解決方案

Cadence設計系統公司今天推出首個TLM驅動式協同設計與驗證解決方案和方法學,使SoC設計師們可以盡享事務級建模(TLM)的好處。

2009-08-07 07:32:00 931

931 Cadence推出首個TLM驅動式設計與驗證解決方案提升基于RTL流程的開發效率

Cadence設計系統公司推出首個TLM驅動式協同設計與驗證解決方案和方法學,使SoC設計師們可以盡

2009-08-11 09:12:18 756

756 就 SystemC 和 SystemVerilog 這兩種語言而言, SystemC 是C++在硬件支持方面的擴展,而 SystemVerilog 則繼承了 Verilog,并對 Verilog 在面向對象和驗證能力方面進行了擴展。這兩種語言均支持

2010-08-16 10:52:48 5673

5673 文章主要介紹《VMM for SystemVerilog》一書描述的如何利用SystemVerilog語言,采用驗證方法學以及驗證庫開發出先進驗證環境。文章分為四部分,第一部分概述了用SystemVerilog語言驗證復雜S

2011-05-09 15:22:02 53

53 引言 Cadence設計系統公司目前提供一種全面的SystemC TLM 驅動式IP設計與驗證解決方案,包括方法學指南、高階綜合、有TLM感知的驗證以及客戶服務,推動用戶向TLM驅動設計與驗證流程轉變

2011-08-25 09:56:24 1724

1724

本內容提供了集成電路設計方法學概論,歡迎大家下載學習

2011-10-28 10:08:44 36

36 利用FPGA的IP核設計和實現FFT算法

2016-05-24 14:14:47 37

37 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:37:00 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:37:00 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:37:00 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:37:00 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:37:00 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:37:00 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:37:00 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:19:07 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:37:00 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:19:07 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:19:07 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:19:07 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:37:00 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:19:07 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:19:07 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:19:07 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:19:07 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:37:00 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:37:00 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:22:05 0

0 斯坦福大學公開課: 編程方法學-分課時課件與作業。

2016-12-14 20:19:07 0

0 CADENCE射頻SiP方法學套件加速無線應用設計

2017-01-14 12:50:17 25

25 ASIC設計在尺寸和復雜性上不斷增加,現代FPGA的容量和性能的新進展意味著這些設計中的2/3能夠使用單個FPGA進行建模。

2017-02-11 16:26:11 1342

1342

設計了一種基于FPGA的驗證平臺及有效的SoC驗證方法,介紹了此FPGA驗證軟硬件平臺及軟硬件協同驗證架構,討論和分析了利用FPGA軟硬件協同系統驗證SoC系統的過程和方法。利用此軟硬件協同驗證

2017-11-17 03:06:01 5210

5210

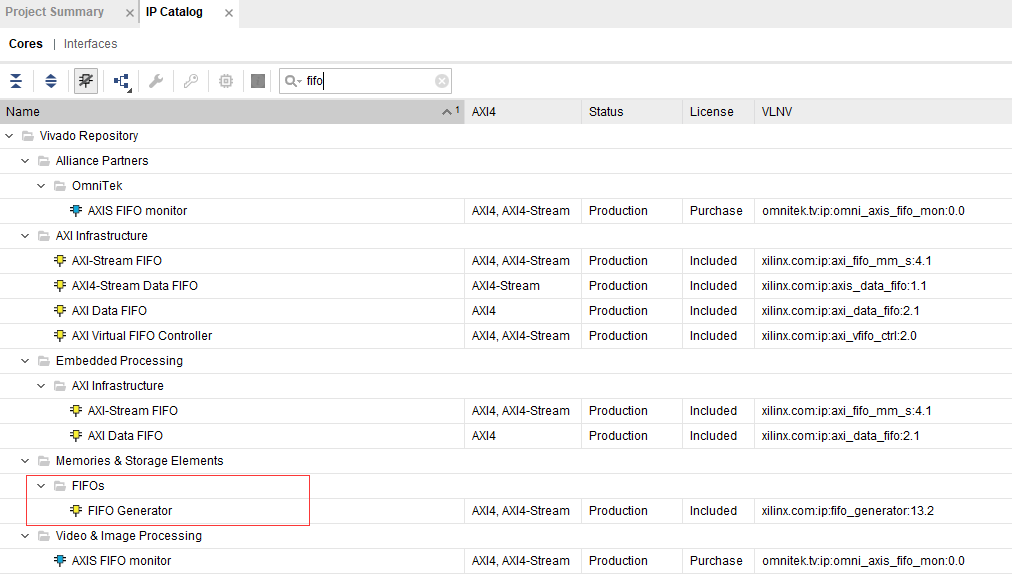

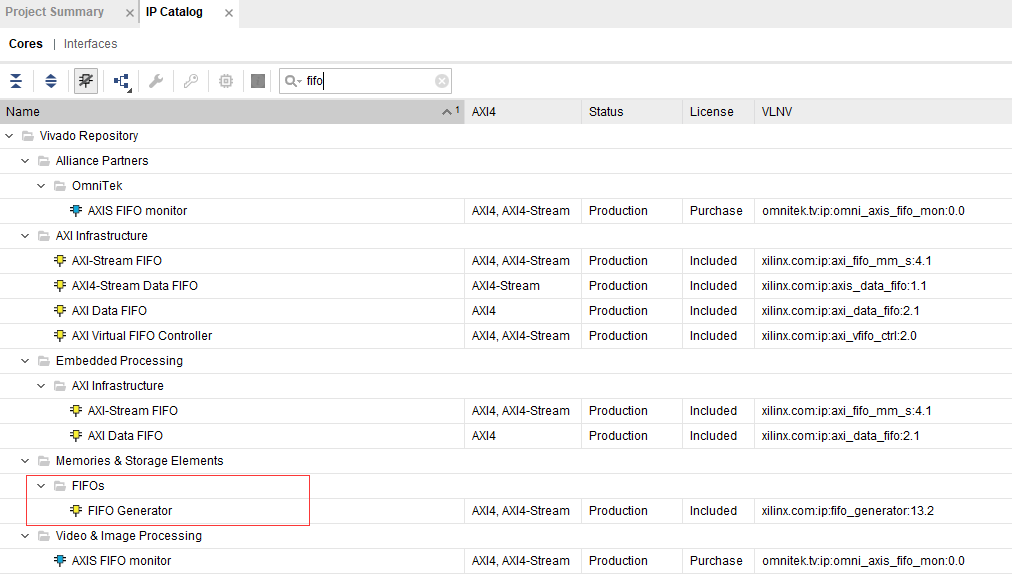

在Vivado下,有兩種方式管理IP。一種是創建FPGA工程之后,在當前工程中選中IP Catalog,生成所需IP,這時相應的IP會被自動添加到當前工程中;另一種是利用Manage IP,創建獨立

2017-11-18 04:22:58 6145

6145 ASIC設計在尺寸和復雜性上不斷增加,現代FPGA的容量和性能的新進展意味著這些設計中的2/3能夠使用單個FPGA進行建模。然而,這些設計中仍然保留有1/3(那就是說,所有ASIC設計中的1/9

2017-11-25 09:05:02 1312

1312 pmsm電機的pid參數設置的方法學習

2018-04-11 10:37:30 13

13 SystemC 是由C++衍生而來,本質是在C++的基礎上添加了硬件擴展庫和仿真核,這使SystemC 可以在不同抽象級對復雜電子系統建模。

2018-07-19 11:55:00 5628

5628

資源。為簡化設計,降低硬件資源開銷,可以在FPGA中利用IP核實現的嵌入式微處理器來對串口數據進行處理。

2019-08-02 08:08:00 5424

5424 介紹了在大型工業模擬仿真系統中,利用FPGA和軟IP核實現數據采集及收發控制的方案,并對其進行設計實現。重點闡述了在發送指令和采集接收兩種數據流模式下.該IP核的控制處理邏輯及工作狀態機的設計及實現

2018-11-07 11:14:19 20

20 在開發PL時一般都會用到分頻或倍頻,對晶振產生的時鐘進行分頻或倍頻處理,產生系統時鐘和復位信號,這是同步時序電路的關鍵,這時就需要使用到時鐘向導IP,下面就介紹一下在vivado中進行PL開發時調用IP的方法。

2018-12-22 15:14:38 10894

10894 FPGA的設計流程就是利用EDA開發軟件和編程工具對FPGA芯片進行開發的過程。FPGA的開發流程一般如下圖所示,包括功能定義/器件選型、設計輸入、功能仿真、邏輯綜合、布局布線與實現、編程調試等主要步驟。

2019-10-15 11:25:07 3819

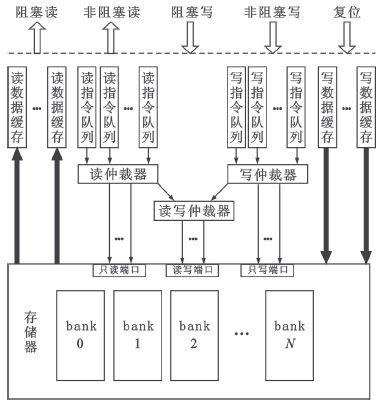

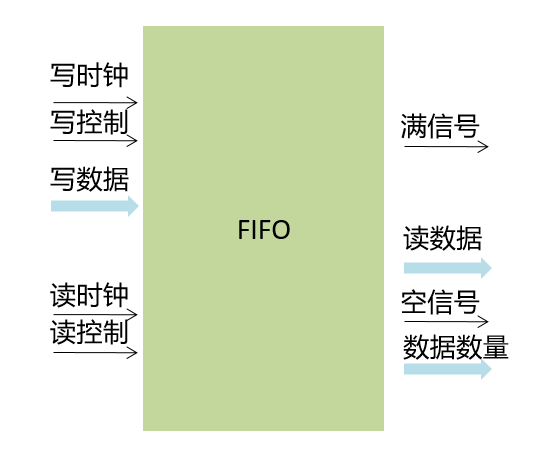

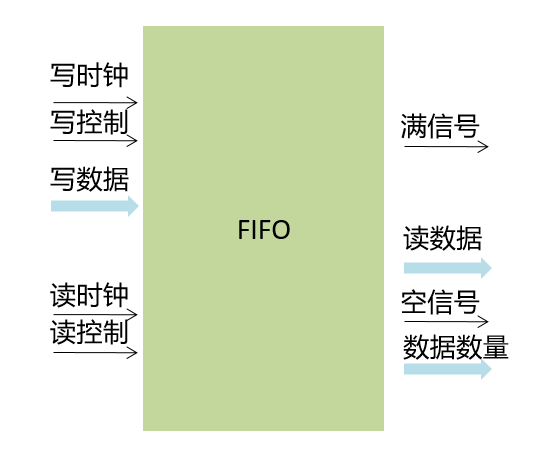

3819 FIFO是FPGA應用當中非常重要的模塊,廣泛用于數據的緩存,跨時鐘域數據處理等。學好FIFO是FPGA的關鍵,靈活運用好FIFO是一個FPGA工程師必備的技能。本章主要介紹利用XILINX提供的FIFO IP進行讀寫測試。

2022-02-08 17:08:32 4442

4442

FPGA_ASIC-DSP和FPGA共用FLASH進行配置的方法(哪些專業適合嵌入式開發)-該文檔為FPGA_ASIC-DSP和FPGA共用FLASH進行配置的方法講解文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 11:16:55 22

22 ASIC設計在尺寸和復雜性上不斷增加,現代FPGA的容量和性能的新進展意味著這些設計中的2/3能夠使用單個FPGA進行建模。然而,這些設計中仍然保留有1/3(那就是說,所有ASIC設計中的1/9

2023-06-04 16:50:01 2194

2194 TLM2.0在2009年成為OSCI標準,主要用于構造總線系統的SystemC模型。

2023-06-25 09:58:38 4086

4086

FPGA開發過程中,利用各種IP核,可以快速完成功能開發,不需要花費大量時間重復造輪子。

2023-08-07 15:43:19 1992

1992

SystemC TLM中的接口 在SystemC TLM中,接口是一個C++的抽象類。抽象類中的所有方法都是用“=0”標識表示的純虛函數。C++不允許創建抽象類的對象,因為抽象類對象是沒有意義

2023-11-02 15:54:21 1748

1748 利用海外爬蟲IP進行數據抓取需要綜合考慮多個方面。

2024-10-12 07:54:38 1057

1057 /prologue-the-2022-wilson-research-group-functional-verification-study/),70% 的 FPGA 項目落后于計劃,12% 的項目落后計劃 50% 以上。 為此,很多FPGA廠商都在自己EDA工具里嵌入IP減少FPGA項目的開發周期,使用 IP 是一種有助于實現按時、高質量且經濟高效的項目交付的方法。

2025-01-15 10:47:37 1246

1246

電子發燒友App

電子發燒友App

評論