1 引言

建立芯片模型是在早期進(jìn)行芯片架構(gòu)決策的有效方法,通過建模不僅可以對芯片的性能做出分析,還可以在硬件沒有完成之前開發(fā)軟件,不僅提高了產(chǎn)品成功率,而且縮短了研發(fā)周期。設(shè)計人員早期采用C/C++語言進(jìn)行硬件建模。但是隨著軟硬件復(fù)雜度的提高,C/C++語言難以再滿足要求。OSCI適時推出了SystemC語言來適應(yīng)新的需求。如今SystemC已經(jīng)被廣泛應(yīng)用于SoC軟硬件建模中。

目前大部分SystemC建模方面是設(shè)計芯片整體模型的描述,這種針對特定芯片設(shè)計的文獻(xiàn)雖然都有參考價值,但是其模型本身借鑒性有限。另一方面,構(gòu)成SoC硬件的基本組件因為可重用的緣故,其模型設(shè)計具有更好的可借鑒性。這方面的研究成果相對較少,而且集中在總線建模方面,也可以看到多核設(shè)計方面的建模方法。

除了上述總線、CPU 架構(gòu)外,片內(nèi)或片外存儲器同樣是系統(tǒng)關(guān)鍵模塊,對系統(tǒng)性能有著至關(guān)重要的影響。文獻(xiàn)[6]對SystemClick框架做了擴展,從而通過存儲器模型能夠分析共享存儲器對性能的影響。文獻(xiàn)[7]針對多通道DRAM 做了建模,并且分析了不同的配置和使用情況對性能的影響。這兩篇文獻(xiàn)都對所設(shè)計的模型做了詳盡的分析,具有很好的參考價值,但是兩者的通用性欠佳。本文提出了一個可配置的通用存儲器SystemC模型。

2 SystemC

SystemC可被視作C++硬件建模和仿真的擴展庫,特別適合集成電路的建模,但它事實上可以用來描述更多的系統(tǒng)。SystemC通過確定仿真核心(simulation kernel)算法定義了處理并行事件和仿真時間的機制。SystemC還定義了模塊、端口、接口、通道等概念來組成一個復(fù)雜SoC的連接關(guān)系和層次結(jié)構(gòu)。因此,它解決了標(biāo)準(zhǔn)C++語言用于復(fù)雜硬件建模時的難題。

3 存儲器的建模

3.1 存儲器模型概述

為了能幫助設(shè)計人員分析系統(tǒng)性能并選擇最合適的存儲器構(gòu)造,存儲器模型需要反映出對性能造成影響的關(guān)鍵參數(shù),即帶寬、延時和仲裁機制。而這些參數(shù)又是由存儲器的結(jié)構(gòu)以及其它參數(shù)決定的。另一方面,本文希望提出一個通用的存儲器模型,因此會有更多的參數(shù)用于配置存儲器以模擬某種特定類型的存儲器特征,比如多端口SRAM。

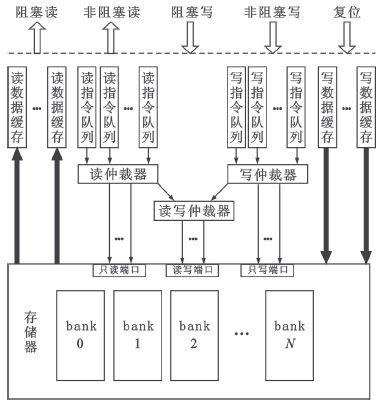

圖1給出了所設(shè)計的存儲器模型的結(jié)構(gòu)。它包括三個部分:一是模型接口;二是端口及bank可配置的存儲器;三是由讀寫通路及仲裁機制構(gòu)成的存儲器控制器。接口部分采用了事務(wù)級建模,而內(nèi)部模塊采用了時鐘精準(zhǔn)的建模,這樣在保證時間精度的同時,方便了接口連接以及提高了仿真速度。

圖1 可配置存儲器模型結(jié)構(gòu)

3.2 存儲器接口

基于SystemC的存儲器模型接口,由SystemC定義的接口基類派生而來。整個存儲器模型是一個SystemC模塊,由于實現(xiàn)了所定義的存儲器模型接口,它成為SystemC概念中的hierarchal channel。因此,該存儲器模型將如同其它SystemC定義的通道,比如FIFO,一樣作為基本組件來連接其它的模塊從而構(gòu)造出SoC硬件系統(tǒng)。所設(shè)計存儲器具有如下所述事務(wù)級SystemC接口。

阻塞讀接口:該接口用來讀取給定地址的給定大小的數(shù)據(jù),當(dāng)數(shù)據(jù)沒有讀出時,調(diào)用這個接口的模塊線程將被堵塞,直到數(shù)據(jù)讀出為止。除了地址和數(shù)據(jù),該接口還包含調(diào)用者的標(biāo)志信息。

非阻塞讀接口:與阻塞讀接口不同的是,如果在調(diào)用時讀指令不能被接受,則返回失敗。否則,不等待數(shù)據(jù)返回便成功退出。這樣調(diào)用接口的模塊線程可以在等待時間做其它事情。調(diào)用者通過監(jiān)聽存儲器模型廣播的當(dāng)前讀出數(shù)據(jù)多對應(yīng)調(diào)用者標(biāo)記來在之后讀出數(shù)據(jù)。

阻塞寫接口:該接口用來向存儲器給定地址寫入給定大小的數(shù)據(jù)。當(dāng)指令或?qū)憯?shù)據(jù)不能被存儲器模型接收時,調(diào)用的線程被堵塞直到接受為止。除了地址和數(shù)據(jù),該接口還包含調(diào)用者的標(biāo)志信息。

非阻塞寫接口:與阻塞寫接口不同的是,當(dāng)指令或數(shù)據(jù)不能被接受時,返回失敗而不等待。否則返回成功。

復(fù)位接口:用于復(fù)位存儲器模型。

為了不強制要求外部提供存儲器模型需要的時鐘,存儲器模型接口中不包含時鐘輸入。模型內(nèi)部有一個專門的時鐘產(chǎn)生線程。

3.3 存儲器實體

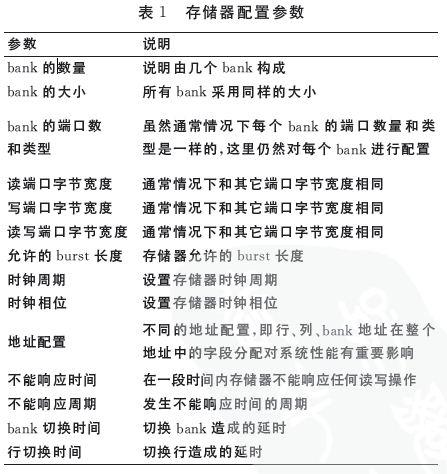

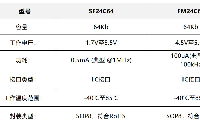

存儲器模型中的存儲器實體可以由多個bank組成,并構(gòu)成一個子模塊。根據(jù)bank的數(shù)量和種類,該存儲器子模塊具有不同數(shù)量的只讀端口、只寫端口和讀寫端口。為了能盡可能模擬不同的存儲器類型,存儲器子模塊可配置參數(shù)如表1所示。

表1 存儲器配置參數(shù)

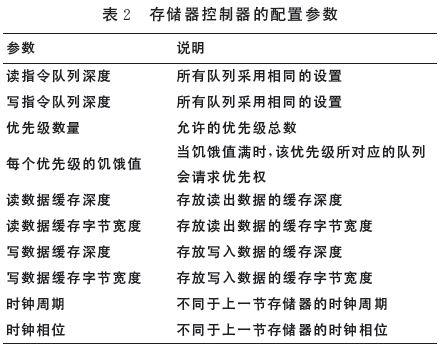

3.4 存儲器控制器

存儲器控制器由指令隊列、數(shù)據(jù)緩存、以及仲裁器構(gòu)成。這一部分對系統(tǒng)的性能有重要影響。讀指令隊列和寫指令隊列用來分別緩存讀寫指令。當(dāng)它們寫滿時,新的讀寫操作將失敗或堵塞。指令隊列的數(shù)量取決于訪問存儲器模型的模塊有幾個優(yōu)先級。相同優(yōu)先級的指令會被放到同一個隊列。讀仲裁器和寫仲裁器分別根據(jù)隊列中的讀地址和寫地址,讀寫數(shù)據(jù)緩存器的狀態(tài),以及指令優(yōu)先級來決定發(fā)送哪個指令到哪個端口。而如果讀指令和寫指令指向了相同的讀寫端口,讀寫仲裁器將再一次做出仲裁。這里的每個仲裁器除了上述功能外,具體的仲裁機制以虛函數(shù)的形式由具體的實現(xiàn)來決定。在該存儲器模型中實現(xiàn)了默認(rèn)的基于優(yōu)先級的輪詢算法。存儲器控制器的配置參數(shù)如表2所示。

表2 存儲器控制器的配置參數(shù)

3.5 參數(shù)配置

存儲器模型的眾多參數(shù)需要在構(gòu)造函數(shù)中配置完成。在運行階段,不能再更改配置。運行階段的配置更改將是我們下一步的研究內(nèi)容,可以用于類似于文獻(xiàn)[8]的自演化系統(tǒng)。

4 應(yīng)用實例

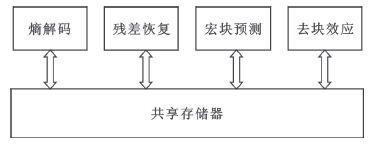

圖2所示為一個H.264解碼器模塊框圖。該解碼器共包括四個模塊以流水線方式工作在宏塊級別。其中熵解碼產(chǎn)生運動矢量,變換系數(shù)等信息。殘差恢復(fù)模塊通過反量化、反變換操作得到殘差。宏塊預(yù)測模塊進(jìn)行幀內(nèi)或幀間預(yù)測并和殘差一起重建出宏塊數(shù)據(jù)。去快效應(yīng)模塊實現(xiàn)H.264去塊效應(yīng)濾波。這四個模塊通過一個共享的SRAM 來交換數(shù)據(jù)。RTL設(shè)計人員根據(jù)設(shè)計指標(biāo)率先完成了各模塊微架構(gòu)的設(shè)計,平均解碼每個模塊所需時間在指標(biāo)范圍內(nèi)。

圖2 H.264解碼器使用共享存儲器在解碼模塊間交換數(shù)據(jù)

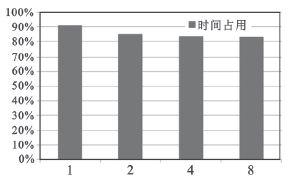

為了確定共享SRAM 引入的性能損失和確定SRAM 的設(shè)計,采用本文存儲器模型進(jìn)行分析。存儲器的大部分參數(shù)已經(jīng)被確定,需要決定采用幾個bank(每個bank是一個單端口SRAM)。另一方面,各模塊讀寫存儲器的時間也基本確定從而有了可靠地負(fù)載模型。通過改變存儲器模型的bank數(shù),得到結(jié)果如圖3所示。

圖3 不同bank數(shù)所對應(yīng)的單個宏塊平均解碼時間占允許時間的比例

由于bank的增加可以減少訪問存儲器的沖突,模型仿真得到的處理時間隨bank數(shù)量的增加而減少。但是可以看到bank數(shù)量對所消耗的時間影響不大,這說明各解碼模塊訪問存儲器的時間分布已經(jīng)比較均勻。由于一個bank的情況已經(jīng)可以滿足要求,所以最后確定bank數(shù)為1。RTL全部完成后的仿真結(jié)果所消耗的時間比模型所給出的略少一些,原因是RTL設(shè)計對訪問共享SRAM 的時間安排做了進(jìn)一步細(xì)化的工作。

5 結(jié)束語

本文提出了一個通用的存儲器SystemC模型,該模型采用統(tǒng)一的事務(wù)級接口,和可配置的時鐘精準(zhǔn)的內(nèi)部控制邏輯以及存儲器構(gòu)成。通過一系列的參數(shù)配置,該模型能夠幫助設(shè)計人員快速實現(xiàn)系統(tǒng)建模并在存儲器設(shè)計和選擇上做出合理判斷。借助其通用性,它還可以幫助保持一致性和減少重復(fù)勞動。該模型被應(yīng)用于視頻解碼案例中,成功預(yù)測了共享SRAM 的bank數(shù)對性能的影響,證明了其有效性。

-

芯片

+關(guān)注

關(guān)注

463文章

54007瀏覽量

465928 -

soc

+關(guān)注

關(guān)注

40文章

4576瀏覽量

229109 -

C++

+關(guān)注

關(guān)注

22文章

2123瀏覽量

77110

發(fā)布評論請先 登錄

【案例5.1】存儲器選型的考慮要點

VTI低功耗SRAM存儲器VTI508HB08

性能測試調(diào)優(yōu)實戰(zhàn)與探索(存儲模型優(yōu)化+調(diào)用鏈路分析)

瑞薩RA系列FSP庫開發(fā)實戰(zhàn)指南之常用存儲器介紹

基于SystemC的存儲器模型設(shè)計與性能分析

基于SystemC的存儲器模型設(shè)計與性能分析

評論