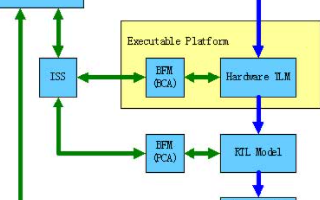

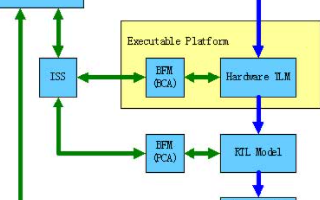

用于早期軟件開發和調試的虛擬平臺可能包含由SystemC TLM模型組成的子系統。得益于它們的快速執行,為創建硬件設計而開發的模型也可用來加速軟件設計。

2020-09-05 12:23:17 6183

6183

雖然 SystemC/C++ 編程風格已使用多年,但最近出現了一些特定使用模式,它們推動工程團隊采用共同的設計流程。這包括抽象算法設計代碼用作高層次綜合 (HLS) 工具的輸入,虛擬平臺模型用于早期軟件測試,可配置的知識產權 (IP) 模塊,等等。

2025-06-24 11:07:24 1115

1115

隨著SystemVerilog成為IEEE的P1800規范,越來越多的項目開始采用基于SystemVerilog的驗證方法學來獲得更多的重用擴展性、更全面的功能覆蓋率,以及更合理的層次化驗證結構

2014-03-24 14:07:47 3820

3820 和 Visualizer Debug Environment 可促進逐步求精方法流程的采用。

· ARM 已表現出支持在完整 IP至SoC 設計流程中使用逐步求精方法進行驗證和實施。

2015-09-14 09:56:34 1567

1567 建立芯片模型是在早期進行芯片架構決策的有效方法,通過建模不僅可以對芯片的性能做出分析,還可以在硬件沒有完成之前開發軟件,不僅提高了產品成功率,而且縮短了研發周期。設計人員早期采用C/C++語言進行

2018-12-05 07:43:00 5969

5969

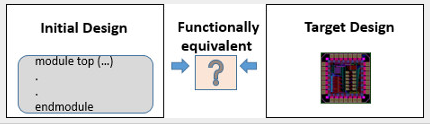

定理證明是形式驗證技術中最高大上的,它需要設計行為的形式化描述,通過嚴格的數學證明,比較HDL描述的設計和系統的形式化描述在所有可能輸入下是否一致。

2022-07-11 16:34:15 7856

7856

1 簡介

隨著設計的復雜程度不斷增加,要求把更多的資源放到驗證上,不但要求驗證能夠覆蓋所有的功能,還希望能夠給出大量的異常情況來檢查DUT對應異常的處理狀態,這在傳統測試方法下往往是難以實現

2023-08-25 16:45:55 1549

1549 SystemC是基于C++的系統級設計語言,兼具描述硬件電路模型和面向對象的抽象能力。

2023-08-07 09:43:45 2059

2059

使用默認應用程序模擬后,您可以:

·通過修改參考平臺測試臺和相應的構建系統對其進行更改,以包括、實例化和連接新的或更新的模型。

·復制和移植作為參考平臺一部分的SystemC周期模型,并將其構建到您自己的定制平臺中。

·修改ARM參考平臺,方法是將您自己的SystemC模型類添加到參考平臺

2023-08-23 07:21:54

查看本節中使用ARM SystemC周期模型的前提條件。

有關以下必備條件的詳細信息,請參閱周期模型系統C運行時安裝指南(101146):

·您的環境中必須安裝受支持的周期模型SystemC

2023-08-12 06:21:42

SystemC是什么?SystmeC的作用是什么?SystemC的用途是什么?

2021-06-21 07:37:41

SystemC是什么?SystmeC的作用是什么?

2021-06-21 08:05:06

驗證方法簡介 設計驗證是用于證明設計正確性的過程,要求和規格。 在數字設計流程中,驗證可確保芯片按照設計意圖正確運行,然后再將設計送去制造。 具體來說,驗證方法是驗證集成電路設計的標準化方法。 驗證

2022-02-13 17:03:49

本節介紹ARM Cortex?-A53系統C周期模型。

ARM系統C周期模型直接從RTL代碼編譯而來。

SystemC模型包裝器以源代碼形式提供,使您能夠為任何符合SystemC IEEE 1666

2023-08-16 07:30:34

本節介紹ARM Cortex?-R52系統C周期模型。

ARM系統C周期模型直接從RTL代碼編譯而來。

SystemC模型包裝器以源代碼形式提供,使您能夠為任何符合SystemC IEEE 1666

2023-08-18 07:25:43

本節介紹ARM Cortex?-R8系統C周期模型。

ARM系統C周期模型直接從RTL代碼編譯而來。

SystemC模型包裝器以源代碼形式提供,使您能夠為任何符合SystemC IEEE 1666

2023-08-16 06:47:09

的反應是否與特性列表和設計規格說明書中的一致,如中斷是否置起。DUT是否足夠穩健,能夠從異常狀態中恢復到正常的工作模式。關于《IC驗證》就介紹到這里!!!更多ic設計內容請關注后續更新............

2020-12-01 14:39:13

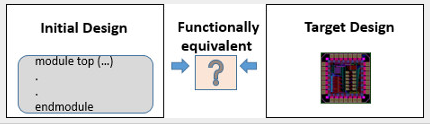

上)對綜合后的網表進行驗證。常用的就是等價性檢查方法,以功能驗證后的HDL設計為參考,對比綜合后的網表功能,他們是否在功能上存在等價性。這樣做是為了保證在邏輯綜合過程中沒有改變原先HDL描述的電路功能

2018-08-13 17:05:29

進行仿真驗證、綜合和時序分析,最后轉換成基于工藝庫的門級網表。后端的流程圖如下,這也就是從netlist到GDSⅡ的設計流程: 后端的主要任務是:(1)將netlist實現成版圖(自動布局布線APR

2018-08-16 09:14:32

關于IC設計的流程是怎樣的?有關IC設計的方法有哪些?

2021-06-21 07:51:54

方法中的漏洞。用于可笑的測試并支持設計人員運行他們自己的驗證。加快標準驗證流程并支持芯片啟動測試開發。等等等等。 這份長達 500 多頁的介紹性材料將向讀者介紹處理硬件驗證需求的主要 Python

2022-11-03 13:07:24

為什么verilog可以描述硬件?在SOC設計中使用verilog,和FPGA為對象使用verilog,有什么區別?SOC流程和FPGA流程的不同之處在哪里?

2021-06-21 07:02:59

1.Verilog 中generate if語句如何用systemc實現?例如:generateif (SIZE < 8)assign y = a & b & c;else

2014-08-29 16:11:21

Verilog 中generate if語句如何用systemc實現?例如:generateif (SIZE < 8)assign y = a & b & c;else

2014-08-28 12:06:43

芯片內嵌SOC子系統的規格制定;嚴格遵循開發流程、模板、標準和規范,完成芯片內嵌子系統的設計,驗證,測試,優化等工作,確保電路設計滿足規格要求,以芯片最后交付為目標。2、及時編寫各種SOC文檔和標準化

2020-02-29 11:06:28

學習方法和思想傳遞給大家。 如果大家所認為的FPGA開發流程就是編碼、下載、調試,那么你就該好好的看下這個視頻教程了,因為我也正是被這種錯誤的學習方式耽誤了好久好久,直到參加了培訓學習才知道,仿真驗證

2015-09-19 16:23:18

關于ADPCM壓縮算法流程介紹

2021-06-03 06:44:13

半定制/全定制混合設計的特點,提出并實現了一套半定制/全定制混合設計流程中功能和時序驗證的方法。論文從模擬驗證、等價性驗證和全定制設計的功能驗證三個方面對FF-DX的分支控制部件進行功能驗證。對于模擬

2011-12-07 17:40:14

使得設計調試和檢驗變成設計周期中最困難的流程。本文重點介紹在調試FPGA系統時遇到的問題及有助于提高調試效率的技術,通過邏輯分析儀配合FPGA View軟件快速有效的觀測FPGA內部節點信號。最后提供了FPGA具體的調試過程和方法。

2019-06-25 07:51:47

在verilog中實現上拉和下拉很容易,使用pullup 和 pulldown 就行,但在systemC設計中如何實現上拉和下拉?

2015-07-22 22:37:20

(back-annotated)時序再次驗證。 此基本流程讓Fusion使用者可以利用經證實的方法,在設計過程中的任何階段驗證混合信號PSC的系統層級行為,就宛如全數字芯片般簡單。此流程依據客戶設計中整合其余數字系統的某個模擬輸入組合執行仿真系統層級行為必要的工作。

2011-10-16 22:55:10

1 簡介隨著設計的復雜程度不斷增加,要求把更多的資源放到驗證上,不但要求驗證能夠覆蓋所有的功能,還希望能夠給出大量的異常情況來檢查DUT對應異常的處理狀態,這在傳統測試方法下往往是難以實現的。此外

2019-07-03 07:40:26

1 簡介 隨著設計的復雜程度不斷增加,要求把更多的資源放到驗證上,不但要求驗證能夠覆蓋所有的功能,還希望能夠給出大量的異常情況來檢查DUT對應異常的處理狀態,這在傳統測試方法下往往是難以實現的。此外

2019-07-01 08:15:47

如何在ModelSim下編譯和仿真SystemC的設計?如何在ModelSim下用SystemC的做驗證?SystemC作為一種系統級設計與驗證語言,非常適合做復雜IC的驗證,而不是用于RTL描述

2012-03-01 11:30:19

請教各位大佬,UVM是基于sv的驗證方法學,如果采用systemc語言編程,如何實現?

2019-11-07 15:30:16

實例狀態機的設計方法介紹;數據選擇器狀態機實現方法與仿真驗證獨立按鍵消抖的狀態機實現方法、仿真驗證與板級驗證紅外遙控解碼的狀態機實現方法、仿真驗證與班級驗證 線性序列機設計方法介紹;數字波形序列發生器的線性

2015-06-15 22:01:45

關于時序邏輯等效性的RTL設計和驗證流程介紹。

2021-04-28 06:13:14

固網短信電話專用SoC芯片介紹一種數模混合SoC設計協同仿真的驗證方法

2021-04-23 06:06:39

混合信號FPGA的智能型驗證流程是怎樣的?

2021-04-30 06:26:35

硬件驗證方法簡明介紹本書“硬件驗證方法簡明介紹”是“半導體 IP 核——不僅僅是設計”系列叢書中“驗證 IP 和 IP 核驗證”的一部分。本書調查、處理和介紹了 IC 驗證中涉及的一些關鍵方法、工具

2022-11-26 20:43:20

,隨著該介紹,第一個硬件驗證語言誕生了。 ***2 年,還創建了一個新標準 SystemVerilog。 現在有不同的驗證語言可用,其中 e、SystemVerilog、SystemC

2022-02-16 13:36:53

怎么在Modelsim下編譯SystemC ,例如使用命令sccom -link

2019-02-28 21:46:01

群主好,我想請教數字電路的系統級設計驗證工具及流程?即系統工程師常用的硬件描述語言,系統驗證工具以及設計驗證的基本流程,多謝!

2012-09-05 15:11:23

和Questasim(兩者間命令上沒有太大的差別,但是后者主要是針對各大驗證方法學來的,對SystemVerilog支持更好) 綜合:S的DC,Cadence的Buildgates。 時序:S的PT

2012-12-28 17:00:22

decided

to write this book after learning SystemC and after using minimal documents

to help us through the quest of bec

2009-02-12 09:30:34 0

0 在介紹嵌入式 SoC IC 概念的基礎上,介紹基于重用(re-use)的 SoC IC 設計方法和流程, 涉及滿足時序要求、版圖設計流程和測試設計的問題, 并給出設計計劃考慮項目。

2009-05-13 16:09:42 28

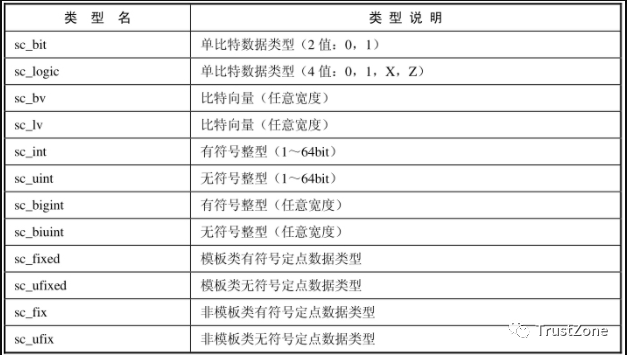

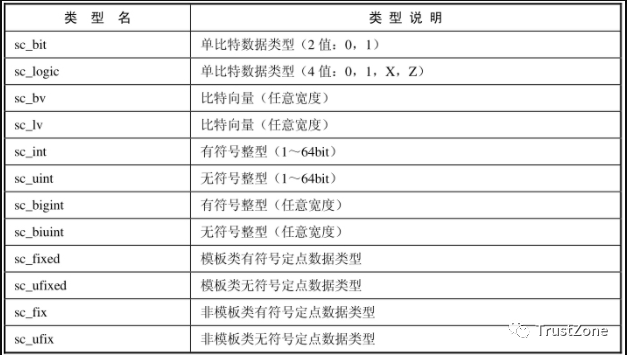

28 IC 技術已發展到SoC 階段,系統級設計、仿真和驗證已成為IC 設計面臨的巨大挑戰。SystemC 是新興的系統級設計語言,為復雜系統的設計與驗證提供了解決方案。本文介紹SystemC 的特點

2009-05-18 13:44:58 28

28 Systemc From The Ground Up:The first question any reader should ask is “Why this book?” We

2009-07-10 17:27:57 0

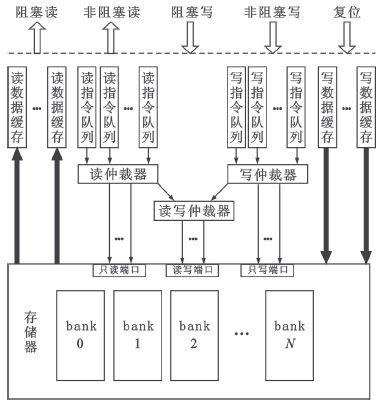

0 事務級(Transaction-Level,TL)建模是SystemC 中提出的一種新型高層次建模方法,以CoCentric System Studio(CCSS)作為SystemC 仿真工具,以一個IP 路由系統為建模實例,分析了事務級建模

2009-07-30 15:27:27 24

24 本文針對目前芯片驗證中出現的瓶頸問題,闡述了當前流行的驗證技術和部分硬件驗證語言。文中介紹了SystemC 和E 語言,以及多種功能驗證技術。最后通過對Rana接口芯片的功

2009-08-13 08:44:19 27

27 本文首先介紹RVM驗證方法學和覆蓋率驅動技術,然后詳細分析如何使用結合覆蓋率驅動技術的RVM驗證方法學對SOC(System On Chip)進行完備的功能驗證, 最

2009-09-05 08:53:00 15

15 本文介紹了基于事務的SoC驗證方法,詳細說明了事務、事務處理器的概念和事務級驗證平臺的功能結構。Synopsys公司的RVM驗證方法學是當前比較流行的基于事務的SoC驗證方法,文中詳細

2010-02-24 11:44:04 8

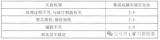

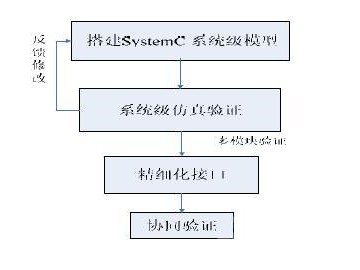

8 視頻編解碼芯片中運動估計與補償單元(MECU)的算法復雜,使用傳統硬件描述語言建立模型和模型驗證的過程繁瑣耗時,為了縮短芯片驗證時間,本文針對MECU模塊提出了基于SystemC語言

2010-02-24 12:07:21 16

16 數字專用集成電路設計中的SystemC建模驗證方法

2010-07-17 16:36:23 31

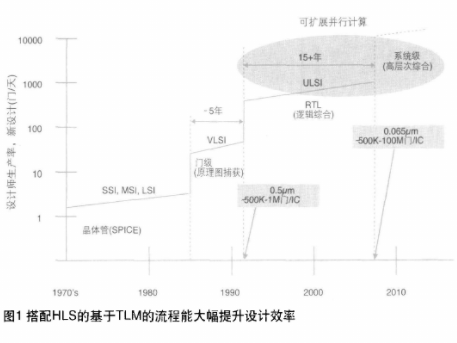

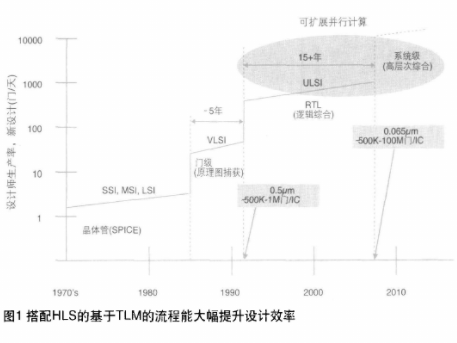

31 利用基于SystemC/TLM的方法學進行IP開發和FPGA建模

隨著系統級芯片技術的出現,設計規模正變得越來越大,因而變得非常復雜,同時上市時間也變得更加苛刻。通常RTL已

2010-01-04 13:11:50 5764

5764

全球電子設計創新領先企業Cadence設計系統公司,今天宣布了業界最全面的用于系統級芯片(SoC)驗證的通用驗證方法學(UVM)開源參考流程。為了配合Cadence EDA360中SoC實現能力的策略,

2010-06-28 08:29:14 2864

2864 就 SystemC 和 SystemVerilog 這兩種語言而言, SystemC 是C++在硬件支持方面的擴展,而 SystemVerilog 則繼承了 Verilog,并對 Verilog 在面向對象和驗證能力方面進行了擴展。這兩種語言均支持

2010-08-16 10:52:48 5675

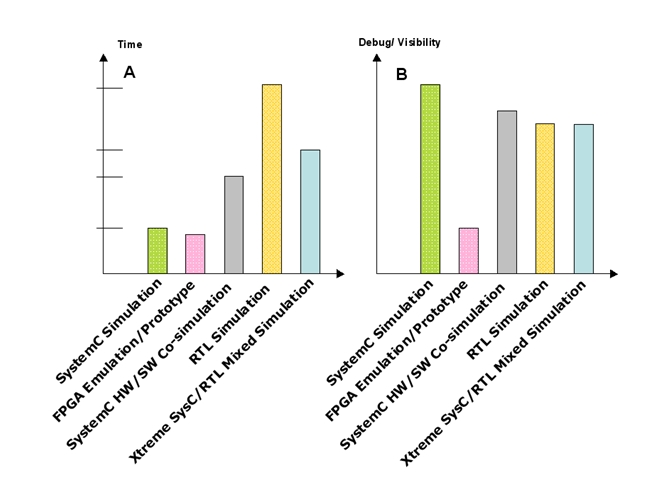

5675 隨著項目復雜程度的提高,最新的系統語言的聚合可以促進生產能力的激增,并為處在電子設計自動化(EDA)行業中的設計企業帶來益處。SystemVerilog和SystemC這兩種語言在設計流

2010-08-25 09:44:47 1557

1557 集成電路設計流程 集成電路設計方法 數字集成電路設計流程 模擬集成電路設計流程 混合信號集成電路設計流程 SoC芯片設計流程

2011-03-31 17:09:12 382

382 文章主要介紹《VMM for SystemVerilog》一書描述的如何利用SystemVerilog語言,采用驗證方法學以及驗證庫開發出先進驗證環境。文章分為四部分,第一部分概述了用SystemVerilog語言驗證復雜S

2011-05-09 15:22:02 53

53 介紹了基于深亞微米 CMOS 工藝A S IC 電路設計流程中的靜態驗證方法。將這種驗證方法與以往的動態驗證方法進行了比較, 結果表明, 前者比后者更加高效和準確。由此可以說明, 靜態驗證

2011-06-21 15:05:00 0

0 隨著半導體技術的發展,驗證已經逐漸成為大規模集成電路設計的主要瓶頸。首先介紹傳統的功能驗證方法并剖析其優缺點,然后引入傳統方法的一種改進基于覆蓋率的驗證方法,最后

2011-06-29 10:46:06 22

22 以失效分析的數據作為基本數據結構,提出了測試項目有效性和測試項目耗費時間的折中作為啟發信息的優化算法,提出了 芯片驗證 分析及測試流程優化技術

2011-06-29 17:58:23 97

97 引言 Cadence設計系統公司目前提供一種全面的SystemC TLM 驅動式IP設計與驗證解決方案,包括方法學指南、高階綜合、有TLM感知的驗證以及客戶服務,推動用戶向TLM驅動設計與驗證流程轉變

2011-08-25 09:56:24 1725

1725

本內容主要介紹了嵌入式軟件開發流程及ARM的中斷調試方法,在整個流程中,用戶首先需要建立工程并對工程做初步的配置,包括配置處理器和配置調試設備

2011-11-09 17:03:20 6031

6031 為了實現軟硬件協同設計和提高仿真速度的需求,采用SystemC語言的建模方法,通過對片上網絡體系結構的研究,提出了一種片上網絡的建模方案,并對一個mesh結構完成了SystemC的建模設

2013-07-30 11:46:44 42

42 systemc語言簡單介紹,有助于初學者更好的運用和了解

2015-12-07 10:33:57 0

0 基于SystemC構建多核DSP軟件仿真平臺_韋祎

2017-01-03 17:41:32 3

3 /HLV 的優勢,并希望探索在公司內部署該流程。要讓 HLS/HLV 能成功予以采用, HLS 編碼風格、代碼檢查、約束驅動型綜合、設計構造以及 C++ 和 SystemC 代碼的結構和功能驗證都需要

2017-09-11 11:37:38 9

9 設計了一種基于FPGA的驗證平臺及有效的SoC驗證方法,介紹了此FPGA驗證軟硬件平臺及軟硬件協同驗證架構,討論和分析了利用FPGA軟硬件協同系統驗證SoC系統的過程和方法。利用此軟硬件協同驗證

2017-11-17 03:06:01 21495

21495

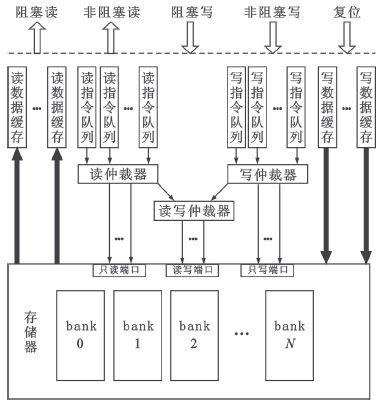

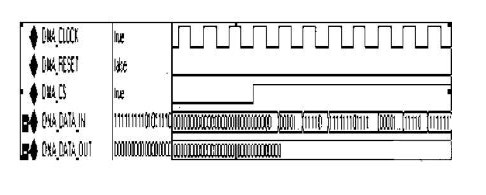

基于前面對DMA控制器工作流程的詳細分析。運用SystemC 語言,建立DMA控制器的Cye le-Accurat級參考模型。控制器由以下幾個模塊組成:寄存器賦值、狀態轉換。輸出模塊和頂層模塊。具體工作過程可以參考如圖3所示的有限狀態機

2017-12-07 16:21:12 3549

3549

AWR公司,高頻EDA軟件的創新領導者,與電氣和電子工程軟件解決方案的領先供應商Zuken今天一起發布AWR Connected for Zuken。該射頻印刷電路板(PCB)驗證流程簡化

2017-12-07 16:40:17 829

829 有關FPGA設計驗證的相關方法

2018-04-03 15:01:41 10

10 本文首先介紹了ic設計的方法,其次介紹了IC設計前段設計的主要流程及工具,最后介紹了IC設計后端設計的主要流程及工具。

2018-04-19 18:04:45 12585

12585 Fmul64的SC設計總體框圖如圖2所示,sc_main()是SystemC設計的top文件,連接測試環境Testbench和待測設計DUT。DUT即Fmul64,用SystemC語言

2018-08-17 10:05:54 8600

8600

支持SystemC的電子系統級(ESL)設計和驗證環境旨在設計,分析,優化和驗證片上系統(SoC)平臺模型。這樣的環境構成了已建立的RTL實現流程的前端。

2019-10-03 17:05:00 6026

6026 為便于后面敘述的方便,這里先簡要介紹一下系統建模的幾種抽象方式和應用類型。

2020-10-04 14:36:00 5319

5319

5G單站驗證流程課件下載

2021-03-19 09:17:48 0

0 近日,Sondrel 開發一種稱為性能驗證環境(PVE 的參數)的方法,據此創建 Synopsys?SystemC 仿真模型,通過調整模型的各種參數,重新了解變化規范的影響。

2022-03-25 10:13:11 1749

1749 芯片驗證就是采用相應的驗證語言,驗證工具,驗證方法,在芯片生產之前驗證芯片設計是否符合芯片定義的需求規格,是否已經完全釋放了風險,發現并更正了所有的缺陷,站在全流程的角度,它是一種防范于未然的措施。

2022-07-25 11:48:49 7723

7723 靜態時序分析是一種重要的邏輯驗證方法,設計者根據靜態時序分

析的結果來修改和優化邏輯,直到設計滿足要求。

2022-11-11 09:42:54 960

960 必須優化正式驗證流程中的初始網表,因此測試設計需要額外的邏輯。在這里,我們提供16 nm節點的形式驗證流程和調試技術。

2022-11-24 12:09:17 2044

2044

和靜態時序分析工具一起來完成對電路完備的驗證。本文就以Synopsys公司的formality工具為例,來介紹形式驗證的流程和基本概念,后續會詳細介紹使用formality做RTL2Gate流程中每一步驟的操作。

2022-12-27 15:18:11 3635

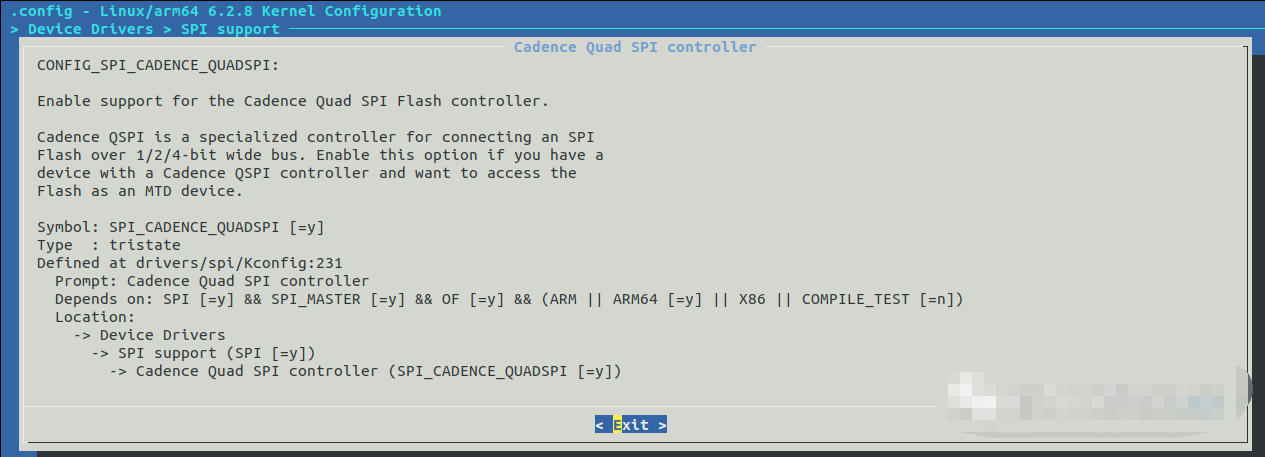

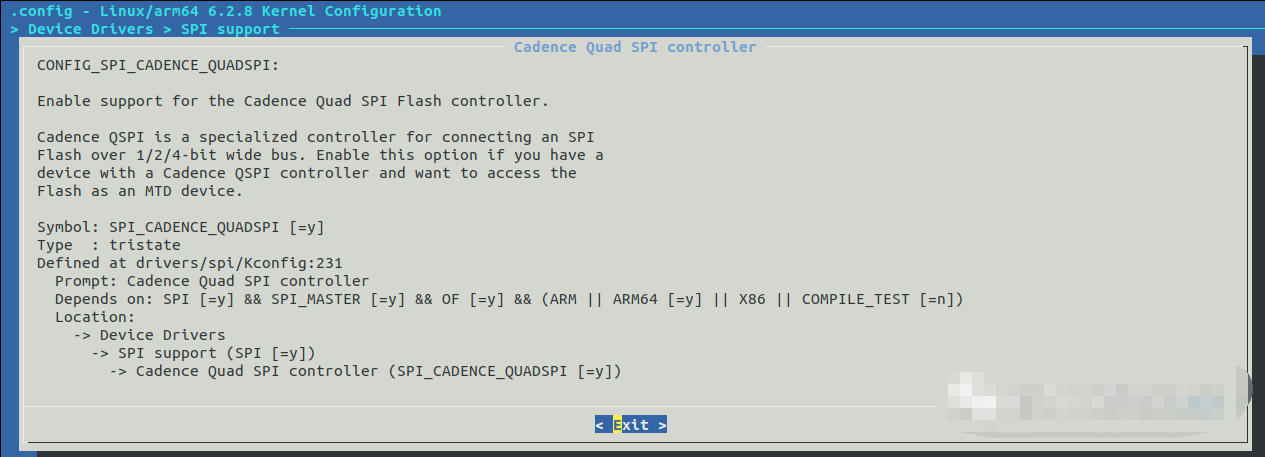

3635 本文主要講述了Linux的QSPI驅動移植方法及驗證方法。

2023-04-14 10:20:41 5021

5021

驗證其實是一個“證偽”的過程,從流程到工具,驗證工程師的終極目的都只有一個。

2023-05-31 10:34:49 2783

2783 隨著RISC-V處理器的快速發展,如何保證其正確性成為了一個重要的問題。傳統的測試方法只能覆蓋一部分錯誤情況,而且無法完全保證處理器的正確性。因此,基于形式驗證的方法成為了一個非常有前途的方法,可以更加全面地驗證處理器的正確性。本文將介紹一種基于形式驗證的高效RISC-V處理器驗證方法。

2023-06-02 10:35:17 2130

2130 SystemC中的模塊 模塊(SC_MODULE)是SystemC系統建模的一個基本單位。一個系統由許多個模塊構成,各個模塊實現系統中不同的功能。在設計中,設計者需要根據功能把復雜的系統劃分成若干個

2023-11-02 15:31:26 2124

2124 SystemC中的事件 在SystemC中,事件提供了一個底層的處理程序間同步及重新啟動的方式,它能用來實現通道的功能,定義事件的語法如下: sc_event event_name; 另外,要觸發或

2023-11-02 15:44:43 1872

1872

SystemC TLM中的接口 在SystemC TLM中,接口是一個C++的抽象類。抽象類中的所有方法都是用“=0”標識表示的純虛函數。C++不允許創建抽象類的對象,因為抽象類對象是沒有意義

2023-11-02 15:54:21 1759

1759 設計的要求運行。 本文將詳細介紹數字電路設計的仿真驗證流程,以及每個步驟的重要性和方法。 仿真驗證的目標: 在設計階段,仿真驗證的目標是驗證電路的功能正確性、時序正確性和性能指標是否滿足設計要求。通過仿真驗證,

2024-01-02 17:00:43 3471

3471 FPGA原型驗證流程是確保FPGA(現場可編程門陣列)設計正確性和功能性的關鍵步驟。它涵蓋了從設計實現到功能驗證的整個過程,是FPGA開發流程中不可或缺的一環。

2024-03-15 15:05:33 3060

3060 本文首先介紹了器件失效的定義、分類和失效機理的統計,然后詳細介紹了封裝失效分析的流程、方法及設備。

2025-03-13 14:45:41 1822

1822

)和行業規范,形成完整的流程閉環。以下是具體流程拆解: 一、驗證前準備階段:明確依據與基礎條件 此階段為后續驗證提供 “標準參照” 和 “數據基礎”,避免驗證無的放矢。 確定驗證范圍與依據 明確驗證對象:單臺監測裝置、某一監測點的多臺裝置,或整個區域

2025-09-03 17:50:34 610

610

電子發燒友App

電子發燒友App

評論