Xilinx FPGA主要分為兩大類,一種側重低成本應用,容量中等,性能可以滿足一般的邏輯設計要求,如Spartan系列;還有一種側重于高性能應用,容量大,性能能滿足各類高端應用,如Virtex系列,用戶可以根據自己實際應用要求進行選擇。 在性能可以滿足的情況下,優先選擇低成本器件。

在此Xilinx研究實驗室演示中,解釋了單源SYCL C ++示例以及生成在Xilinx FPGA上運行的硬件實現的方法。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636312 -

賽靈思

+關注

關注

33文章

1798瀏覽量

133435 -

C++

+關注

關注

22文章

2124瀏覽量

77115

發布評論請先 登錄

相關推薦

熱點推薦

keil實現c與c++混合編程

參考touchgfx生成的代碼,發現了一個不需要添加--cpp11 參數的解決方法,具體操作如下。

一、創建一個空白的C文件和頭文件在頭文件中定義c++文件中需要調用的函數,如圖所示

發表于 01-26 08:58

C語言與C++的區別及聯系

并沒有錯。

C++一開始被本賈尼·斯特勞斯特盧普(Bjarne Stroustrup)發明時,起初被稱為“C with Classes”,即「帶類的C」。

很明顯,它是在

發表于 12-24 07:23

C語言和C++之間的區別是什么

區別

1、面向對象編程 (OOP):

C語言是一種面向過程的語言,它強調的是通過函數將任務分解為一系列步驟進行執行。

C++在C語言的基礎上

發表于 12-11 06:23

C/C++條件編譯

條件編譯是一種在編譯時根據條件選擇性地包含或排除部分代碼的處理方法。在 C/C++ 中,條件編譯使用預處理指令 #ifdef、#endif、#else 和 #elif 來

發表于 12-05 06:21

C++程序異常的處理機制

1、什么是異常處理?

有經驗的朋友應該知道,在正常的C和C++編程過程中難免會碰到程序不按照原本設計運行的情況。

最常見的有除法分母為零,數組越界,內存分配失效、打開相應文件失敗等等

發表于 12-02 07:12

Xilinx FPGA串行通信協議介紹

Xilinx FPGA因其高性能和低延遲,常用于串行通信接口設計。本文深入分析了Aurora、PCI Express和Serial RapidIO這三種在Xilinx系統設計中關鍵的串

以太網通訊在FPGA上的實現

一、介紹在本項目由于我們需要使用PC實時的向FPGA發送將要識別的圖片,所以我們最終選擇使用以太網來從PC向FPGA發送圖片并暫存在DDR中,下面是對以太網協議和硬件實現的一些介紹。

發表于 10-30 07:45

在vivado上基于二進制碼對指令運行狀態進行判斷

vivado仿真運行判斷狀態是否正確。

獲取二進制代碼

在Nucleistudio中打開相關項目的Properties,按路徑打開C/C++ Build ->settin

發表于 10-24 06:31

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

本篇將詳細介紹如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試。SRAM是一種非易失性存儲器,具有高速讀取和寫入的特點。在

NucleiStudio下載程序到FPGA中的E203上

使用NucleiStudio開發應用程序,并將應用程序的代碼下載到FPGA上。這里,以helloworld為例,介紹該過程遇到的問題以及解決方法。

1、新建Nuclei RISC-V C

發表于 10-20 09:24

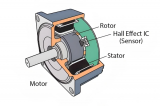

使用Verilog在FPGA上實現FOC電機控制系統

在自動駕駛、電動滑板車、無人機甚至工業自動化領域,高性能電機控制是不可或缺的核心技術。而如果你對硬件有足夠的熱情,你會發現:傳統用 MCU 實現 FOC(Field-Oriented Control,磁場定向控制)也能“搬”到 FPGA

在Xilinx FPGA上單源SYCL C++實現運行的方法

在Xilinx FPGA上單源SYCL C++實現運行的方法

評論