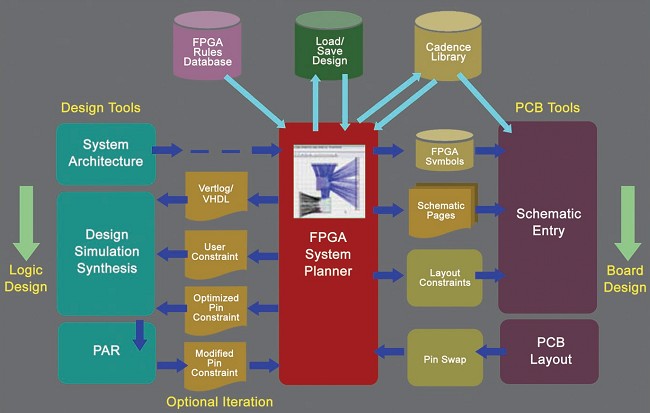

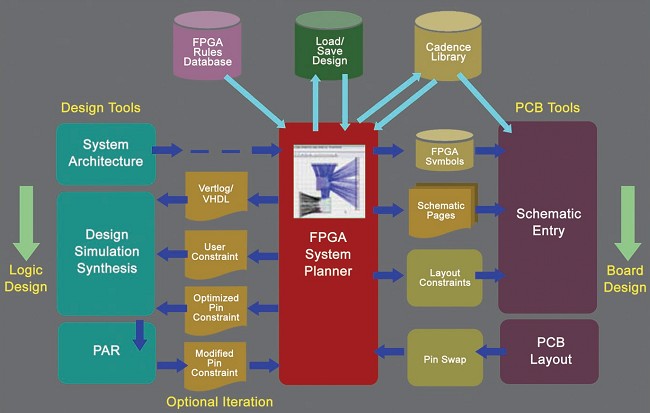

Cadence FPGA System Planner(FSP)是一款完整性高的FPGA-PCB系統(tǒng)化協(xié)同設(shè)計工具。此次主要為大家介紹FPGA System Planner的基本情況,詳見原文。

2013-04-08 11:08:03 6040

6040

簡介

ORCAD Capture (以下以Capture代稱)是一款基于Windows 操作環(huán)境下的電路設(shè)計工具。利用Capture軟件,能夠?qū)崿F(xiàn)繪制電路原理圖以及為制作PCB和可編程的邏輯設(shè)計提供連

2010-08-30 17:43:32 5005

5005 Cadence公司的OrCAD ® ®電路板設(shè)計器包含一個完全整合的設(shè)計流程,包括約束經(jīng)理,設(shè)計捕捉技術(shù),組件的工具,在PCB編輯器,自動/交互式路由器,而制造業(yè)和機械CAD接口

2010-09-09 17:47:32 5549

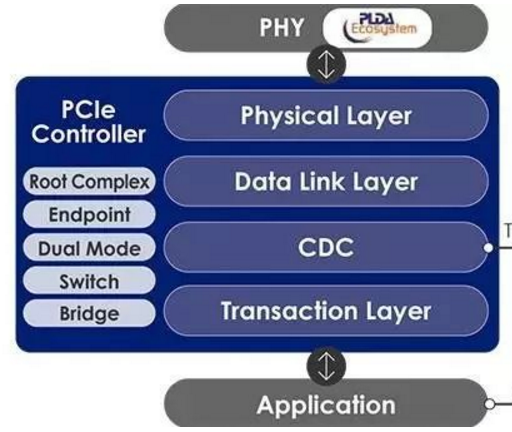

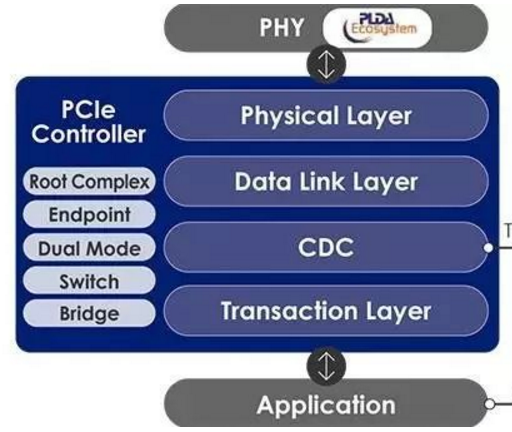

5549 PLDA的XpressRICH4?和XpressRICH4-AXI?為Xilinx? Virtex? Ultrascale+? FPGA提供PCIe 4.0 v0.9支持,為FPGA技術(shù)提供最先進(jìn)、最高性能的互連技術(shù)

2017-09-24 06:17:00 8570

8570

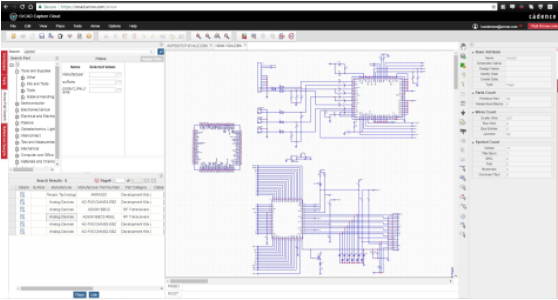

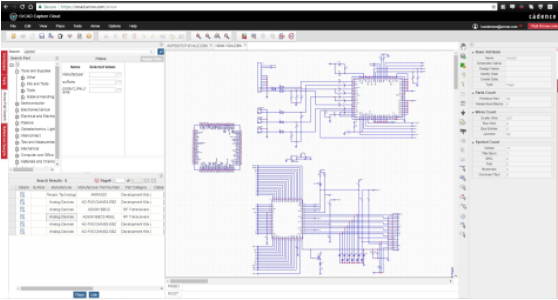

艾睿電子和Cadence Design Systems公司擴大了其正在進(jìn)行的合作,在Arrow.com設(shè)計中心推出針對OrCAD Capture Cloud的Cadence? OrCAD?Entrepreneur包。

2018-02-08 13:24:39 10323

10323

美高森美公司(Microsemi Corporation)宣布成為首家針對RISC-V設(shè)計提供全面軟件工具鏈和知識產(chǎn)權(quán)(IP)內(nèi)核的可編程邏輯器件(FPGA)供應(yīng)商。其RV32IM RISC-V

2018-07-31 09:01:00 3500

3500 在 FPGA(Zynq? UltraScale+? MPSoC) 上的 Ubuntu 22.04 桌面映像上安裝了各種 EE 設(shè)計應(yīng)用程序(包括 KiCad),并用它設(shè)計 PCB。

2024-02-26 09:04:27 2926

2926

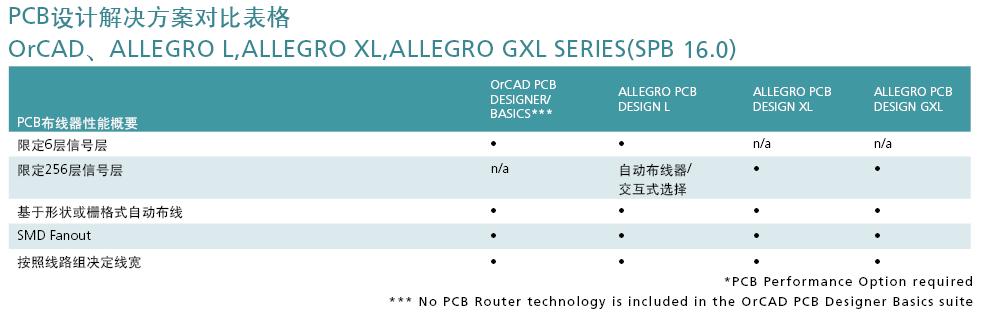

cadence公司于2012年9月25日發(fā)布了具有一系列新功能的Cadence? OrCAD? 16.6 PCB設(shè)計解決方案,用戶定制功能增強,模擬性能提高20%, 使用戶得以更快、更有預(yù)見性

2013-01-11 11:23:33

,OPE,EDM)如何助推我們的設(shè)計效率、全新Allegro PCB系統(tǒng)如何讓復(fù)雜設(shè)計變得更簡潔明確、領(lǐng)先的Sigrity 2015在SI/PI又有著怎樣的提升?我們誠邀您參加”2015 Cadence

2015-05-19 16:54:13

的數(shù)據(jù)庫架構(gòu),使用模型和庫為Cadence OrCAD和Allegro產(chǎn)品線提供完全可升級的PCB解決方案,加速你的設(shè)計速度并擴大設(shè)計規(guī)模,從而提高了設(shè)計效率,縮短了設(shè)計周期,以及更快地實現(xiàn)

2018-08-30 10:49:16

Cadence OrCAD and Allegro 17.2 安裝破解步驟PCB設(shè)計專業(yè)群:4676294

2017-07-26 13:25:08

系列產(chǎn)品應(yīng)用效率與可用性的一系列大幅改良。例如OrCAD Capture CIS如今提供了自動布線功能以迅速增加連線,還有全新的三維封裝顯示功能。OrCAD PCB Editor提供了三維查看與“翻板

2018-09-10 16:37:20

Cadence設(shè)計系統(tǒng)公司發(fā)布了Cadence Allegro系統(tǒng)互連設(shè)計平臺針對印刷電路板(PCB)設(shè)計進(jìn)行的全新產(chǎn)品和技術(shù)增強。改進(jìn)后的平臺為約束驅(qū)動設(shè)計提供了重要的新功能,向IC、封裝和板

2018-11-23 17:02:55

cadence公司于2012年9月25日發(fā)布了具有一系列新功能的Cadence® OrCAD® 16.6 PCB設(shè)計解決方案,用戶定制功能增強,模擬性能提高20

2012-12-18 10:18:07

Cadence設(shè)計系統(tǒng)公司發(fā)布Cadence?Allegro?系統(tǒng)互連設(shè)計平臺針對印刷電路板(PCB)設(shè)計進(jìn)行的全新產(chǎn)品和技術(shù)增強.改進(jìn)后的平臺為約束驅(qū)動設(shè)計提供了重要的新功能,向IC、封裝和板

2018-08-28 15:28:45

Cadence設(shè)計系統(tǒng)公司發(fā)布Cadence?Allegro?系統(tǒng)互連設(shè)計平臺針對印刷電路板(PCB)設(shè)計進(jìn)行的全新產(chǎn)品和技術(shù)增強.改進(jìn)后的平臺為約束驅(qū)動設(shè)計提供了重要的新功能,向IC、封裝和板

2008-06-19 09:36:24

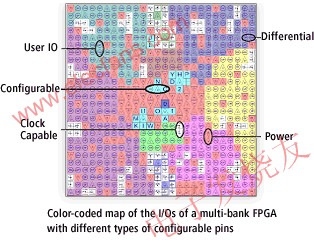

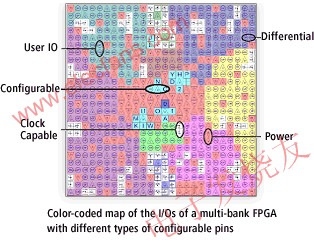

如今,FPGA 功能強大且管腳數(shù)目極大,可為工程師提供大量機會來提升特性和功能,同時還能降低產(chǎn)品成本。隨著復(fù)雜度增加,將這些器件集成到印刷電路板也成為了一項嚴(yán)峻的挑戰(zhàn)。數(shù)百個邏輯信號需映射到器件

2018-09-20 11:11:16

本帖主要介紹Cadence軟件FPGA System Planner(FSP)使用,以連載的方式提供。希望能給到大家一點幫助。FSP工具是cadence公司為了FPGA/PCB協(xié)同設(shè)計而推出的一個

2011-10-18 11:44:31

FPGA設(shè)計提高教程Advanced FPGA Design.FPGA設(shè)計提高教程Advanced FPGA Design.

2012-08-11 16:19:12

Cadence設(shè)計系統(tǒng)公司,日前公布了OrCAD Capture Marketplace,這是一種獨特的、基于網(wǎng)絡(luò)的設(shè)計環(huán)境,為工程師帶來了一個完整的PCB設(shè)計生態(tài)體系,其中包含了業(yè)界首個網(wǎng)絡(luò)

2020-07-06 17:49:34

。OrCAD Express for Windows是一個32位的用來設(shè)計印刷電路板PCBs和可編程器件的Windows應(yīng)用軟件。對于PCB設(shè)計來說,Express提供了整個系統(tǒng)的設(shè)計和OrCAD關(guān)于

2018-11-23 16:51:40

設(shè)計的 Orcad LayoutR 以及供高密度電路板自動繞線的SPECCTRAR 4U。新加入的SPECCTRA,用以支援設(shè)計日益復(fù)雜的各種高速、高密度印刷電路板設(shè)計。SPECCTRA 提供設(shè)計師

2011-06-21 10:27:15

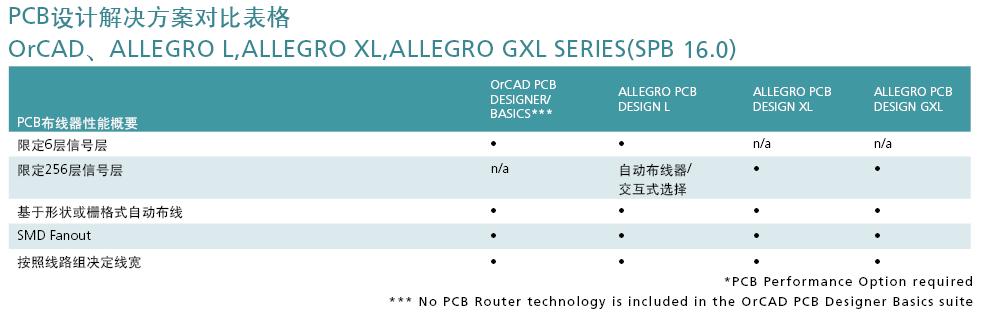

布的OrCAD產(chǎn)品線為PCB設(shè)計師提供了低價格、高性能的設(shè)計工具,繼續(xù)提高整個Cadence Allegro PCB產(chǎn)品的生產(chǎn)力并提供簡單擴展功能。 帶有PSpice的OrCAD PCB Designer

2020-07-07 09:06:50

我有個TI方案的原來是cadence的,是用cadence16.6做的,怎么轉(zhuǎn)成AltiumDesigner13支持的格式,按網(wǎng)上的提示通過AltiumDesigner13工具的導(dǎo)入向?qū)聿僮鳎x擇

2016-01-05 15:30:31

,圖二為封裝bottom層,圖三是所用焊盤名稱,圖4為所用焊盤,圖五是與圖四一樣的表貼焊盤。cadence中有著同等大小表貼焊盤,為什么在繪制封裝的時候用的是通孔焊盤而不是表貼焊盤?是不是自帶的封裝畫錯了?因為我看到其他人繪制的板子FPGA的焊盤都是表貼的。有沒有人遇到過這個問題,求大神指教

2020-08-05 16:08:22

cadence_OrCAD經(jīng)典教程

2017-08-11 12:06:29

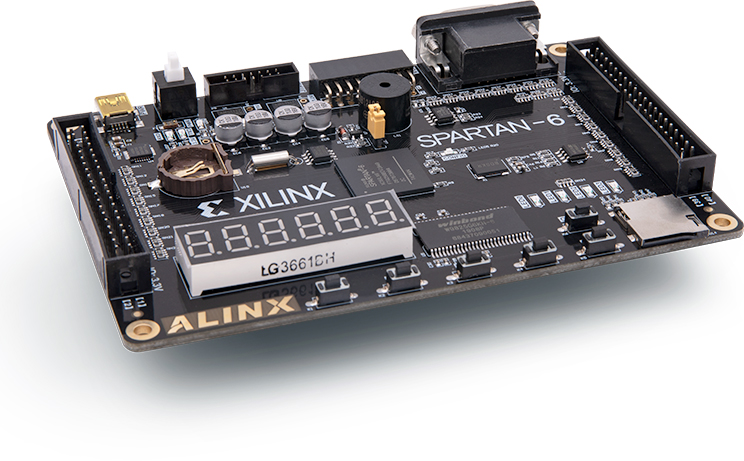

【摘要】:<正>Altium繼續(xù)為電子產(chǎn)品設(shè)計人員擴大器件選項。目前,最新版Altium Designer可提供Xilinx Spartan-6器件系列的全面支持

2010-04-24 10:07:11

FPGA,特別是Zynq系列或Altera等效SOC + FPGA,設(shè)計PCB板,批量生產(chǎn)產(chǎn)品并通過嚴(yán)格的EMI資格認(rèn)證。在什么階段,公司可能需要將Xilinx稱為Altera技術(shù)支持?可能需要

2019-04-15 10:08:36

,提供系列在線培訓(xùn)課程(均為免費)。歡迎大家踴躍參與!內(nèi)容包括:課程分為四期,內(nèi)容包括Capture CIS、PSpice、FPGA System Planner以及Allegro PCB SI培訓(xùn)

2012-05-28 22:57:48

OrCAD Capture作為行業(yè)標(biāo)準(zhǔn)的PCB原理圖輸入方式,是當(dāng)今世界最流行的原理圖輸入工具之一,具有簡單直觀的用戶設(shè)計界面。不管是用于設(shè)計模擬電路、復(fù)雜的PCB、FPGA和CPLD、PCB改版

2020-07-06 16:15:50

根據(jù)自己的經(jīng)驗,總結(jié)了一下,大致分為以下個方面 1.協(xié)同設(shè)計支持pcb協(xié)同,原理圖協(xié)同,是業(yè)界最先進(jìn),并且唯一。是應(yīng)對復(fù)雜設(shè)計、緊急項目最好的解決辦法。(cadence無實時協(xié)同

2014-10-28 14:06:53

本文概述了開發(fā)這種系統(tǒng)所必須面對的各種設(shè)計挑戰(zhàn),并講解了Altium公司的最新電子設(shè)計環(huán)境Nexar如何為FPGA設(shè)計提供一種全新的方法。這種方法不僅可將處理器有效地集成入FPGA之中,而且成為一種挖掘現(xiàn)有以及未來大容量、低成本FPGA部件應(yīng)用潛力的系統(tǒng)級

2021-05-08 06:02:24

BOARD EVAL FOR ORCA OR4E6 FPGA

2023-03-30 11:49:36

TINYFPGA AX2

2024-03-14 22:18:36

TINYFPGA BX

2024-03-14 22:18:36

:1.運用Allegro FPGA System Planner來完善FPGA的pin腳分配從而優(yōu)化整個系統(tǒng)的協(xié)調(diào)性。2.運用Allegro FPGA System Planner產(chǎn)生其他信號在PCB

2012-03-28 10:04:23

`例說FPGA連載32:PLL例化配置與LED之使用Pin Planner進(jìn)行引腳分配特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc

2016-09-14 16:59:04

幾天前從學(xué)長那里裝了candence軟件16.5版本的軟件,但是其中一個部分FPGA system planner 里的元器件不全,沒有v7的FPGA,而且里面的操作界面也不一樣,關(guān)鍵是我已經(jīng)破解

2014-04-30 14:50:06

哪位大佬能提供FSP(FPGA System Planer)的使用教程?跪求

2020-06-19 11:31:29

我似乎無法使用System Ace在ML605板上配置V6 Fpga。我有一個包含邏輯設(shè)計的文件,其中包含一個EDK系統(tǒng),還有一個bootoader啟動我的應(yīng)用程序,該程序在FLASH中編程。當(dāng)我

2019-09-25 12:34:58

` 本帖最后由 kuyuan 于 2010-12-22 16:01 編輯

cadence OrCAD及PSpice入門者可以參考視頻教程了視頻為高清版,有點大,后續(xù)的視頻就到PSpice技術(shù)支持中心下載吧.下載地址是www.pspice.com.cn`

2010-12-22 15:58:37

Planner來完善FPGA的pin腳分配從而優(yōu)化整個系統(tǒng)的協(xié)調(diào)性。2.運用Allegro FPGA System Planner產(chǎn)生其他信號在PCB板子走線邏輯關(guān)系以及FPGA logic

2012-03-28 11:48:59

我買了你的kc705并下載了你的電路板文件。我想使用Cadence的Orcad捕獲來重繪原理圖。我怎樣才能做到這一點?你有Orcad捕獲版的電路板文件嗎?如果您這樣做,請發(fā)送或建議我。非常感謝你。

2020-07-30 14:24:02

產(chǎn)品發(fā)布的一部分,這種新技術(shù)有助于為PCB設(shè)計提供更短、更具可預(yù)測性的設(shè)計周期。對于使用高密度互連(HDI)的設(shè)計師來說,該技術(shù)實現(xiàn)了重大改進(jìn),它對于高端消費電子市場的客戶價值尤其明顯,同時也適合

2018-08-30 10:37:59

后,到培訓(xùn)當(dāng)天回收到郵件,通過郵件提供的鏈接就可以加入培訓(xùn)。 內(nèi)容包括:Capture CIS、PSpice、FPGA System Planner以及Sigrity培訓(xùn)。以下是初步定下的培訓(xùn)時間

2013-05-28 21:31:14

cadence中文教程:Cadence 是一個大型的EDA 軟件它幾乎可以完成電子設(shè)計的方方面面包括ASIC 設(shè)計FPGA 設(shè)計和PCB 板設(shè)計與眾所周知的EDA 軟件Synopsys相比Cadence 的綜合工具略為遜色然

2008-07-12 09:33:38 0

0 億海微6系 EQ6HL45型可編程邏輯芯片開發(fā)平臺采用核心板加擴展板的模式,方便用戶對核心板的二次開發(fā)利用,為前期驗證和后期應(yīng)用提供了可能。相信這樣的一款產(chǎn)品非常適合從事FPGA開發(fā)的工程師、科研人員等群體。

2022-02-16 17:06:51

概述EasyGo FPGA Coder Block是嵌入Matlab/Simulink里面的FPGA 仿真工具包軟件。提供了一些基礎(chǔ)的函數(shù)庫以及常用的控制函數(shù)模塊,配合

2022-05-19 09:16:05

概述EasyGo FPGA Solver是EasyGo開發(fā)的專門部署在FPGA 硬件上的解算器軟件。根據(jù)不同的應(yīng)用需求,會有不同的FPGA Solver 選擇

2022-05-19 09:21:43

PCBNavigator在OrCAD與PowerPCB間的應(yīng)用說明:該軟件是一個從原理圖到PCB板的雙向綜合環(huán)境系統(tǒng)能完成pin/gate swapreference designrenamerules 等原理圖與pcb間雙向修改支持的軟件及版本有Zuken Cadstar

2009-09-26 18:29:58 0

0 斑梨電子FPGA CycloneII EP2C5T144 學(xué)習(xí)板 開發(fā)板產(chǎn)品參數(shù)1. 采用ALTERA公司的CyclonellEP2C5T144芯片作為核心最小系統(tǒng),將FPGA

2023-02-03 15:14:29

Altium發(fā)布NanoBoard 3000 FPGA開發(fā)板的部署外殼產(chǎn)品

日前,Altium 宣布為其最新 NanoBoard 3000 FPGA 開發(fā)板添加即時部署選項。設(shè)計人員將無需創(chuàng)建定制的 PCB,便可使 FPGA 設(shè)計直

2009-12-01 08:36:37 1610

1610 CADENCE PCB設(shè)計技術(shù)方案

CADENCE PCB設(shè)計解決方案能為解決與實現(xiàn)高難度的與制造密切相關(guān)的設(shè)計提供完整的設(shè)計環(huán)境,該設(shè)計解決方案集成了從設(shè)計構(gòu)

2010-04-29 08:53:19 4158

4158

OrCAD FPGA系統(tǒng)規(guī)劃

創(chuàng)新的FPGA - PCB協(xié)同設(shè)計

該Cadence ®的OrCAD ® FPGA系統(tǒng)提供了一個完整的策劃,為FPGA - PCB協(xié)同設(shè)計,使用戶能夠創(chuàng)建可擴展解決方案的

2010-08-30 17:49:26 2058

2058

Cadence是一個大型的EDA軟件,它幾乎可以完成電子設(shè)計的方方面面,包括ASIC設(shè)計、FPGA設(shè)計和PCB板設(shè)計。與眾所周知的EDA軟件Synopsys相比,Cadence的綜合工具略為遜色。然而Cadence在仿真電路

2011-05-11 18:26:43 0

0 Cadence OrCAD Capture 具有快捷、通用的設(shè)計輸入能力,使Cadence OrCAD Capture 線路圖輸入系統(tǒng)成為全球最廣受歡迎的設(shè)計輸入工具。它針對設(shè)計一個新的模擬電路、修改現(xiàn)有的一個 PCB 的線路圖

2011-05-22 11:50:23 0

0 完整性高的FPGA-PCB系統(tǒng)化協(xié)同設(shè)計工具 Cadence OrCAD and Allegro FPGA System Planner便可滿足較復(fù)雜的設(shè)計及在設(shè)計初級產(chǎn)生最佳的I/O引腳規(guī)劃,并可透過FSP做系統(tǒng)化的設(shè)計規(guī)劃,同時整合logic、

2013-04-08 11:07:53 0

0 2013年12月3號,北京——Altera公司(Nasdaq: ALTR)今天發(fā)布了Arria 10版Quartus II軟件,這是業(yè)界第一款支持20 nm FPGA和SoC的開發(fā)工具。基于TSMC

2013-12-03 10:48:47 2106

2106 現(xiàn)在的很多 PCB 工具和 FPGA 開發(fā)軟件都有附帶的接口,可以相互轉(zhuǎn)換。將 PCB 設(shè)計軟件中的管腳轉(zhuǎn)換 成 FPGA 的約束文件,或者再 FPGA 調(diào)整之后再次導(dǎo)入 PCB。本開發(fā)板使用 OrCAD 系列軟件進(jìn)行設(shè)計,因此以 OrCAD 為例進(jìn)行講解,希望對大家的學(xué)習(xí)有幫助!

2015-12-16 15:31:44 2

2 Cadence_PCB_設(shè)計與制板,有需要的下來看看。

2016-02-19 16:37:09 0

0 FPGA設(shè)計提高班培訓(xùn)課堂PPT_V1.0

2016-05-10 11:24:33 25

25 PCB Navigator在OrCAD與PowerPCB間的應(yīng)用說明

2016-06-15 15:53:57 0

0 華清遠(yuǎn)見FPGA代碼-在Xilinx的FPGA開發(fā)板上運行第一個FPGA程序

2016-10-27 18:07:54 23

23 華清遠(yuǎn)見FPGA代碼-在Altera的FPGA開發(fā)板上運行第一個FPGA程序

2016-10-27 18:07:54 16

16 FPGA參考設(shè)計提供電源管理方案。X-Fest 2014展會期間,系統(tǒng)設(shè)計人員可通過Xilinx Kintex UltraScale FPGA KCU105評估板對Maxim方案進(jìn)行評估。

2017-02-10 16:42:19 1392

1392 前一陣一直在忙,所以沒有來得及寫博文。弄完雜七雜八的事情,又繼續(xù)FPGA的研究。使用Verilog HDL語言和原理圖輸入來完成FPGA設(shè)計的方法都試驗過了,更高級的還有基于System Generator和基于EDK/Microblaze的方法。

2017-02-11 03:10:11 8716

8716

現(xiàn)在的FPGA算法的實現(xiàn)有下面幾種方法: 1. Verilog/VHDL 語言的開發(fā) ; 2. system Generator; 3. ImpulsC 編譯器實現(xiàn)從 C代碼到 HDL 語言; 4.

2017-11-17 14:29:06 8946

8946 隨著現(xiàn)場可編程門陣列(FPGA)已發(fā)展成為真正的可編程系統(tǒng)級芯片,利用這些芯片設(shè)計印制電路板(PCB)的任務(wù)變得愈加復(fù)雜。要完全實現(xiàn)FPGA的功能,需要對PCB板進(jìn)行精心設(shè)計。采用高速FPGA進(jìn)行設(shè)計時,在板開發(fā)之前和開發(fā)期間對若干設(shè)計問題進(jìn)行考慮是十分重要的。

2017-11-23 14:18:22 5427

5427 PLD/FPGA 常用開發(fā)軟件System Generator 9.10。 業(yè)內(nèi)領(lǐng)先的高級系統(tǒng)級FPGA開發(fā)高度并行系統(tǒng)。

2017-11-26 11:34:56 14

14 Cadence 是一個大型的EDA 軟件,它幾乎可以完成電子設(shè)計的方方面面。包括ASIC 設(shè)計,FPGA 設(shè)計和PCB 板設(shè)計。與眾所周知的EDA 軟件Synopsys相比,Cadence 的綜合工具略為遜色。

2017-12-04 10:00:39 77079

77079

Cadence 是一個大型的EDA 軟件,它幾乎可以完成電子設(shè)計的方方面面,包括ASIC 設(shè)計、FPGA 設(shè)計和PCB 板設(shè)計。Cadence 在仿真、電路圖設(shè)計、自動布局布線、版圖設(shè)計及驗證等方面有著絕對的優(yōu)勢。Cadence 包含的工具較多幾乎包括了EDA 設(shè)計的方方面面。

2018-02-07 13:44:36 21351

21351 Cadence 是一個大型的EDA 軟件,它幾乎可以完成電子設(shè)計的方方面面,包括ASIC 設(shè)計、FPGA 設(shè)計和PCB 板設(shè)計。Cadence 在仿真、電路圖設(shè)計、自動布局布線、版圖設(shè)計及驗證等方面

2018-02-07 17:11:21 28461

28461

關(guān)鍵詞: System Builder , SmartFusion FPGA 帶有System Builder設(shè)計工具的Libero SoC軟件可以加快SmartFusion2的開發(fā)和縮短客戶的上市

2018-09-25 09:07:01 1042

1042 如今,FPGA 功能強大且管腳數(shù)目極大,可為工程師提供大量機會來提升特性和功能,同時還能降低產(chǎn)品成本。隨著復(fù)雜度增加,將這些器件集成到印刷電路板也成為了一項嚴(yán)峻的挑戰(zhàn)。數(shù)百個邏輯信號需映射到器件

2018-10-26 11:54:01 544

544 本文檔的主要內(nèi)容詳細(xì)介紹的是Cadence Allegro 16.5 PCB軟件使用教程培訓(xùn)資料免費下載。

為了適應(yīng)不同用戶的需要,Cadence軟件包中提供了Allegro PCB

2018-12-20 08:00:00 0

0 近期在研究FPGA System Planner的過程中,發(fā)現(xiàn)在調(diào)用原理圖符號時需要指定一個原理圖器件庫,而本人設(shè)計中使用的FPGA符號與之前創(chuàng)建的不太一樣,為了精準(zhǔn)無誤地進(jìn)行設(shè)計,需要將FPGA從原理圖中導(dǎo)出并保存至器件庫。本文將這個方法分享給讀者。

2019-06-30 09:17:22 35751

35751

pcb設(shè)計人員可以在[FPGA]器件庫中提供的限制條件下優(yōu)化基于pcb的引腳排列,并將這些引腳自動傳回FPGA設(shè)計系統(tǒng)。

2019-08-14 12:31:00 3129

3129 ORCAD PCB設(shè)計解決方案為您提供從概念到生產(chǎn)的PCB設(shè)計所需的一切。在每一個eda行業(yè)中,orcad pcb designer standard和orcad pcb designer

2019-09-16 15:52:00 66

66 為了適應(yīng)不同用戶的需要,Cadence軟件包中提供了Allegro PCB Designer、OrCAD PCB Designer Standard和OrCAD PCB Designer Professional 3種PCB設(shè)計軟件版本。

2020-05-13 08:00:00 0

0 SDRAM。如Kintex Ultrascale FPGA中的型號Kintex7可支持32位DDR4SDRAM,主要應(yīng)用于在通信,雷達(dá),信號處理,IC驗證等高端領(lǐng)域。UMI總代理英尚微電子可提供樣品及測試。

2020-08-06 10:12:00 3377

3377

FPGA System Planner解決了設(shè)計一個或多個工程師時遇到的挑戰(zhàn)PCB板上的更多大引腳數(shù)FPGA。

2021-03-16 16:56:15 24

24 FPGA支持信息

2021-03-23 13:27:01 2

2 本手冊概述了使用硬件描述語言(HDLs)設(shè)計Fiedld可編程門陣列(FPGAs)的概況。它包括為HDL新手用戶提供的設(shè)計提示,以及為第一次設(shè)計FPGAs的經(jīng)驗豐富的用戶提供的設(shè)計提示。

2021-03-28 11:09:59 14

14 最近在學(xué)習(xí)小馬哥的Cadence課程,該系列課程為學(xué)習(xí)筆記:使用Cadence Allegro繪制小馬哥DragonFly四軸飛行器(STM32F4主控)PCB四層板教程。1. 準(zhǔn)備工作

2021-11-17 15:21:02 36

36 orcad_library_builder制作cadence的BGA元器件符號

2022-05-31 16:02:07 0

0 Xilinx FPGA pcb設(shè)計

2023-05-29 09:11:36 0

0 OrCAD Express for Windows是一個32位的Windows的應(yīng)用軟件,它包含在圖板和其它設(shè)備上設(shè)計時,你所需要的一切,包含并支持FPGAs和復(fù)雜的可編程邏輯裝置CPLDs

2023-08-18 14:33:07 1294

1294 OrCAD X Platform ,這是一款支持云的系統(tǒng)設(shè)計解決方案,易于使用,性能強大,提供自動化和協(xié)作功能,是名副其實的設(shè)

2023-09-14 13:40:02 4082

4082

PCB板厚,看似微小卻承載著巨大的意義。在電子產(chǎn)品設(shè)計中,選擇合適的板厚至關(guān)重要。 今天就讓捷多邦小編來帶大家了解,pcb板厚度一般是多少才合適 一般而言,PCB板厚度常見的是1.6mm,這個尺寸

2023-09-15 10:22:14 10414

10414 新版Allegro與OrCAD使用多階段預(yù)發(fā)布的方式確保內(nèi)容與質(zhì)量能夠符合客戶的需要。來自北美、歐洲、亞洲和日本的20多家客戶參與了多階段測試計劃。參與測試計劃的客戶與Cadence的合作伙伴包括

2023-10-17 14:55:31 1894

1894 FPGA開發(fā)板是一種基于FPGA(現(xiàn)場可編程門陣列)技術(shù)的開發(fā)平臺,它允許工程師通過編程來定義和配置FPGA芯片上的邏輯電路,以實現(xiàn)各種數(shù)字電路和邏輯功能。FPGA開發(fā)板通常包括FPGA芯片、時鐘模塊、電源模塊、輸入輸出接口等組件,并提供相應(yīng)的編程軟件和開發(fā)工具,方便工程師進(jìn)行電路設(shè)計和調(diào)試。

2024-03-14 18:20:29 4535

4535 FPGA(現(xiàn)場可編程門陣列)和PCB(印刷電路板)在電子系統(tǒng)設(shè)計中各自扮演著重要的角色,并且它們之間存在著密切的關(guān)聯(lián)。

2024-03-15 14:59:34 3049

3049 通過使用開放式 FPGA 堆棧 (OFS) ,BittWare 在其 FPGA 解決方案上提供對 oneAPI 的支持。

2024-03-29 14:57:03 1389

1389

來都來了,我們就來好好講講為什么萬能的FPGA如此青睞FMC?WhyFMC?FMC即FPGAMezzanineCard(FPGA中間層板卡),由子板模塊和載卡兩部分構(gòu)成。FMC載卡:為子板模塊提供

2025-04-14 09:52:40 1404

1404

Cadence SPB(Silicon Package Board)是一套電子設(shè)計自動化(EDA)軟件套件,主要用于集成電路、封裝和PCB的設(shè)計、仿真和驗證。它提供了一整套從設(shè)計到生產(chǎn)的工具,支持

2025-05-22 16:45:12 31

31 FPGA 開發(fā)板的核心芯片主要分為兩大類:純 FPGA 芯片和 SoC(System on Chip)芯片。

2025-09-17 16:56:06 1395

1395

電子發(fā)燒友App

電子發(fā)燒友App

評論