基于eFPGAsim的電機硬件在環(huán)測試系統(tǒng),是面向電驅(qū)HIL測試的高精度FPGA的解決方案,利用最新的eHS (Electric Hardware Solver)技術實現(xiàn),在獲得基于FPGA片上仿真

2017-08-09 10:52:21 3639

3639

FPGA調(diào)試時硬件設計中及其重要的一步,本文就在FPGA調(diào)試過程中存在3種常見的誤解,進行一些討論....

2018-09-19 09:27:50 4748

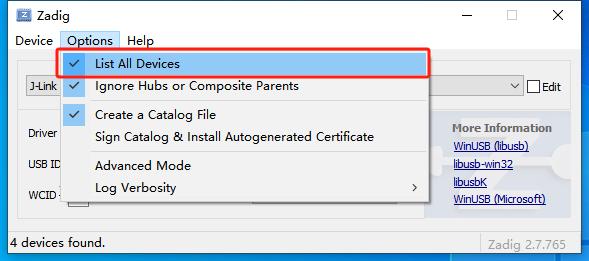

4748 日常的FPGA開發(fā)常常會遇到“編碼與上機調(diào)試使用各自的電腦”的場景,解決方法一般如下。

2023-05-25 14:36:44 4304

4304

上篇主要是分享了Vivado編譯軟件遠程調(diào)試的方法。杰克使用Vivado軟件進行遠程連接,主要是用于固化程序以及FPGA(PL端)的異常排查。而本篇主要內(nèi)容是對使用Vitis軟件遠程調(diào)試的方法進行總結(jié)和分享。

2023-05-25 14:36:58 4231

4231

在調(diào)試FPGA電路時要遵循必須的原則和技巧,才能降低調(diào)試時間,防止誤操作損壞電路。通常情況下,參考以下步驟執(zhí)行 FPGA硬件系統(tǒng)的調(diào)試。

2019-10-17 06:15:47

FPGA硬件系統(tǒng)的調(diào)試方法在調(diào)試FPGA電路時要遵循一定的原則和技巧,才能減少調(diào)試時間,避免誤操作損壞電路。一般情況下,可以參考以下步驟進行FPGA硬件系統(tǒng)的調(diào)試。(1)首先在焊接硬件電路時,只焊接

2012-08-12 11:52:54

`基于FPGA的在線系統(tǒng)調(diào)試概述本文節(jié)選自特權(quán)同學的圖書《FPGA設計實戰(zhàn)演練(邏輯篇)》(特權(quán)同學版權(quán)所有)配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCttFPGA

2015-09-02 18:39:49

的代碼有更深刻體會;FPGA調(diào)試,解決bug問題和軟件調(diào)試過程一樣嗎,還是和硬件一樣完全黑盒調(diào)試(很多情況都是摸索,看看是不是電阻電容問題,干擾問題.....),解決bug的方式區(qū)別是什么???據(jù)說

2012-11-25 02:10:05

系統(tǒng)的設計技巧 2.4 FPGA硬件系統(tǒng)的調(diào)試方法 2.5 典型實例1:在Altera的FPGA開發(fā)板上運行第一個FPGA程序 2.6 典型實例2:在Xilinx的FPGA開發(fā)板上運行第一個

2012-02-09 15:45:32

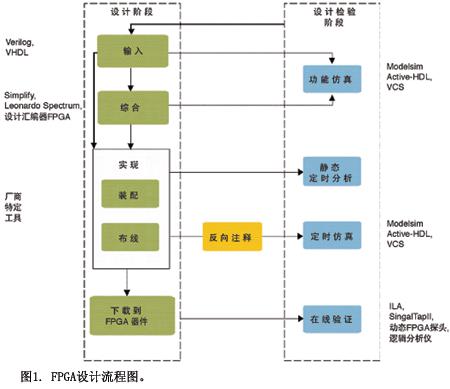

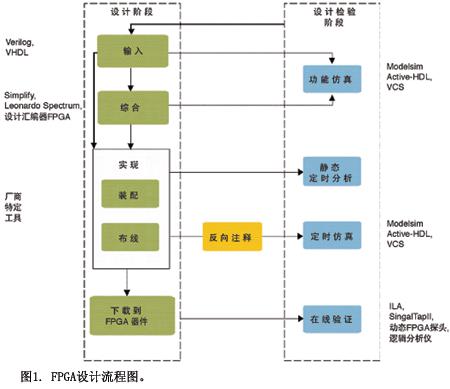

FPGA是可編程芯片,因此FPGA的設計方法包括硬件設計和軟件設計兩部分。硬件包括FPGA芯片電路、存儲器、輸入輸出接口電路以及其他設備,軟件即是相應的HDL程序以及最新才流行的嵌入式C程序。硬件

2015-11-30 15:28:41

飛凌干貨分享--攻城獅手把手帶你認識硬件調(diào)試方法

2021-01-15 07:30:26

在此硬件系統(tǒng)設計中,經(jīng)常會遇到需要大容量的數(shù)據(jù)存儲的情況,我們將針對FPGA中內(nèi)部BlockRAM有限的缺點,提出了將FPGA與外部SRAM相結(jié)合來改進設計的方法,并給出了部分VHDL程序。

2021-05-06 06:01:46

本文就調(diào)試FPGA系統(tǒng)時遇到的問題及有助于提高調(diào)試效率的方法,針對Altera和Xilinx的FPGA調(diào)試提供了最新的方法和工具。

2021-04-29 06:30:56

調(diào)試底層硬件模塊的邏輯是什么?怎樣在基于FPGA的嵌入式硬件設計添加一個debug的硬件模塊?

2021-12-24 06:37:53

android系統(tǒng)識別不同硬件版本方法是什么?

2022-03-02 06:17:49

摘要:為了實現(xiàn)對非相干雷達的接收相參處理,基于數(shù)字穩(wěn)定校正(DSU)的原理,采用ALTERA公司的StratixⅡ系列芯片和VHDL編程語言,設計了一種基于FPGA的DSU硬件實現(xiàn)方法。實驗結(jié)果表明

2019-06-28 08:27:33

使得設計調(diào)試和檢驗變成設計周期中最困難的流程。本文重點介紹在調(diào)試FPGA系統(tǒng)時遇到的問題及有助于提高調(diào)試效率的技術,通過邏輯分析儀配合FPGA View軟件快速有效的觀測FPGA內(nèi)部節(jié)點信號。最后提供了FPGA具體的調(diào)試過程和方法。

2019-06-25 07:51:47

單片機的系統(tǒng)硬件調(diào)試,通常有靜態(tài)調(diào)試和動態(tài)調(diào)試兩種不同,前者是通過目測、萬能表測試、加電檢查、聯(lián)機檢查的方法,在加電于樣機之前.對樣機的型號規(guī)格,以及安裝要求等進行核對,同時檢查 電源 系統(tǒng).防止

2025-12-03 06:10:27

請教各位,基于FPGA的硬件控制系統(tǒng)該如何去設計?

2021-04-28 07:01:25

摘要:簡要介紹了軟硬件協(xié)同仿真技術,指出了在大規(guī)模FPGA開發(fā)中軟硬件協(xié)同仿真的重要性和必要性,給出基于Altera FPGA的門級軟硬件協(xié)同仿真實例。 關鍵詞:系統(tǒng)級芯片設計;軟硬件協(xié)同仿真

2019-07-04 06:49:19

本文基于Viitex-5 LX110驗證平臺的設計,探索了高性能FPGA硬件系統(tǒng)設計的一般性方法及流程,以提高FPGA的系統(tǒng)性能。

2021-04-26 06:43:55

與modelsim聯(lián)合仿真的方法;掌握Quartus ii軟件提供的眾多免費IP的使用方法;掌握Quartus ii軟件提供的若干在線調(diào)試工具的使用方法;學習若干簡單的綜合實驗的設計方法 FPGA 教程規(guī)劃

2015-06-15 22:01:45

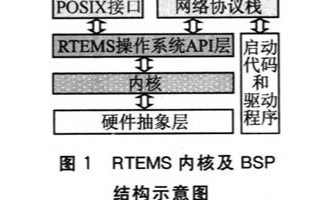

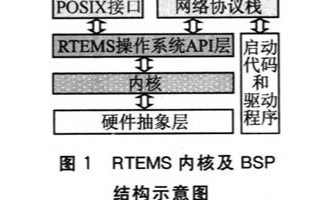

相對于軟件調(diào)試而言,使用硬件調(diào)試器可以獲得更強大的調(diào)試功能和更優(yōu)秀的調(diào)試性能。硬件調(diào)試器的基本原理是通過仿真硬件的執(zhí)行過程,讓開發(fā)者在調(diào)試時可以隨時了解到系統(tǒng)的當前執(zhí)行情況。目前嵌入式系統(tǒng)開發(fā)中最

2017-03-10 10:44:09

嵌入式系統(tǒng)交叉調(diào)試方法一般分為兩種,一種是基于JTAG的片上調(diào)試方法,一種是基于調(diào)試代理的遠程調(diào)試方法。JTAG是一種國際標準芯片測試協(xié)議,目前大多數(shù)CPU體系都支持JTAG。基于JTAG的片上調(diào)試

2017-12-18 10:55:39

/O也許是有限的。新類型的包還限制訪問FPGA引腳。系統(tǒng)速度也是個問題,因為探針的連接可能會引起性能或者噪聲信號降低。 最后,推動FPGA調(diào)試方法改變的關鍵因素是有了新的工具,這些工具采用內(nèi)部或者

2010-01-08 15:05:27

隨著嵌入式系統(tǒng)的發(fā)展,迫切需要在嵌入式系統(tǒng)開發(fā)階段對嵌入式系統(tǒng)進行離線測試與分析,以保證系統(tǒng)的軟件應用程序、硬件具有兼容性、高可靠性和高可用性,迅速發(fā)現(xiàn)并準確定位系統(tǒng)中存在的問題。本文結(jié)合上海貝爾阿爾卡特股份有限公司開發(fā)的寬帶交換系統(tǒng),討論離線單板硬件測試方法和系統(tǒng)測試方法。

2019-07-05 07:24:18

邏輯設計方法; 3、深入理解ASIC/FPGA生命周期及開發(fā)流程,深入理解和掌握高可靠性FPGA開發(fā)、鑒定方法; 4、熟練使用硬件調(diào)試儀表(如示波器、萬用表、邏輯分析儀)的基本功能及IDE工具的試用,如

2016-11-14 15:33:13

請教一下大牛,嵌入式系統(tǒng)交叉調(diào)試原理和方法是什么呀?大家都說嵌入式系統(tǒng)交叉調(diào)試方法一般分為兩種,一種是基于JTAG的片上調(diào)試方法,一種是基于調(diào)試代理的遠程調(diào)試方法。是對的嗎?

2021-03-05 07:55:30

潤和Hi3861V100芯片迷你無線仿真USB Open OCD調(diào)試板多功能調(diào)試器

2023-03-28 13:07:10

主要介紹基于S3C4510B的硬件系統(tǒng)的詳細設計步驟、實現(xiàn)細節(jié)、硬件系統(tǒng)的調(diào)試方法等,通過對本章的閱讀,可以使絕大多數(shù)的讀者具有根據(jù)自身的需求、設計特定應用系統(tǒng)的能力。

2008-09-09 14:56:59 0

0 FPGA調(diào)試工具chipscope,學習與使用FPGA必用的工具。。

2009-03-23 09:45:00 86

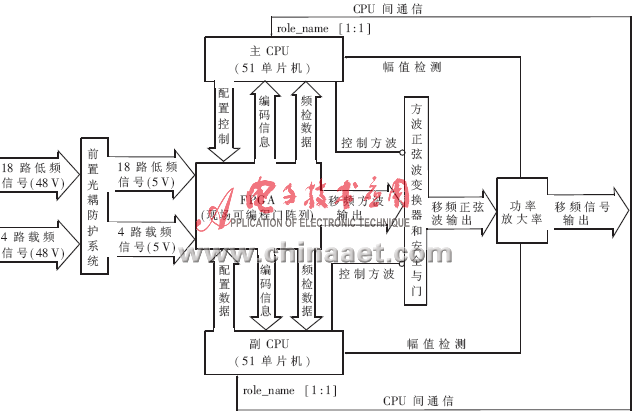

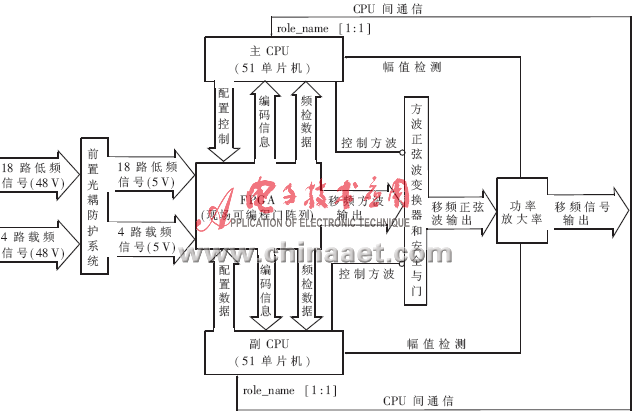

86 根據(jù)電力監(jiān)控系統(tǒng)的要求,提出一種基于FPGA技術的多路交流信號采集與處理系統(tǒng)的設計方法。分析整個系統(tǒng)的結(jié)構(gòu),并討論FPGA內(nèi)部硬件資源的劃分和軟件的設計方案,以及各個功能

2009-05-16 14:47:58 27

27 混合CPU_FPGA系統(tǒng)的調(diào)試方法:

2009-07-23 10:44:07 7

7 該文闡述了現(xiàn)場可編程邏輯器件FPGA的主要特點,應用FPGA芯片和VHDL硬件描述語言設計的模擬示波器數(shù)字信號顯示系統(tǒng)的設計原理和設計方法。現(xiàn)場可編程邏輯門陣列(Field Programmab

2009-08-17 10:36:11 19

19 本文介紹了DSP 和FPGA 在數(shù)字電子設計中的優(yōu)勢,并結(jié)合雷達模擬系統(tǒng)的硬件設計實例,重點闡述了相應的硬件與軟件實現(xiàn)方法。關鍵詞:DSP FPGA 數(shù)字電路設計雷達模擬系統(tǒng)

2009-08-25 14:33:01 15

15 TLA邏輯分析儀原理與應用硬件調(diào)試基礎教程:數(shù)字系統(tǒng)的調(diào)試過程– 首先啟動硬件電路– 調(diào)試硬件的設計錯誤– 調(diào)試部局或結(jié)構(gòu)錯誤 短路, 開路, 連接錯誤等

2009-10-17 17:33:59 19

19 實用FPGA的調(diào)試工具—ChipScope Pro

ChipScope Pro應用于FPGA調(diào)試階段,它具有傳統(tǒng)邏輯分析儀的功能,可以觀察FPGA內(nèi)部的任何信號,觸發(fā)條件,數(shù)據(jù)寬度和深度等的設

2010-02-09 15:10:46 95

95 介紹了基于ARM和FPGA的端到端重配置終端的硬件平臺設計方法。給出了系統(tǒng)設計的硬件結(jié)構(gòu)和重要接口, 提出了由ARM微處理器通過JTAG在系統(tǒng)配置FPGA的方法, 以滿足重配置系統(tǒng)中軟件

2010-09-14 16:40:09 21

21 隨著 FPGA 的設計速度、尺寸和復雜度明顯增長,使得整個設計流程中的實時驗證和調(diào)試成為當前FPGA 系統(tǒng)的關鍵部分。獲得FPGA 內(nèi)部信號有限、FPGA 封裝和印刷電路板(PCB)電氣噪聲,這一

2011-06-10 15:42:28 28

28 縱觀數(shù)字集成電路的發(fā)展歷史,電子產(chǎn)品的市場正在逐漸細分。本書主要重點介紹相關問題和技巧,幫助您在調(diào)試 FPGA 系統(tǒng)是提高您的工作效率。希望對您的工作學習有所幫助!

2011-07-11 16:49:37 406

406 本文就調(diào)試FPGA系統(tǒng)時遇到的問題及有助于提高調(diào)試效率的方法,針對Altera和Xilinx的FPGA調(diào)試提供了最新的方法和工具。

2011-09-27 14:28:39 1197

1197

在調(diào)試FPGA電路時要遵循必須的原則和技巧,才能降低調(diào)試時間,防止誤操作損壞電路。通常情況下,參考以下步驟執(zhí)行 FPGA硬件系統(tǒng)的調(diào)試。 1、在焊接硬件電路前,首先要測試電路板

2013-01-16 11:59:58 6123

6123 座談總結(jié):DSP電路板的硬件設計和系統(tǒng)調(diào)試

2016-01-19 16:56:00 37

37 、各類Flash、硬盤、液晶、網(wǎng)絡接口等)設計做了詳細介紹。本書還結(jié)合硬件設計,給出了大量用于硬件調(diào)試的代碼和驅(qū)動程序的編寫方法。

2016-04-26 11:42:13 2

2 、各類Flash、硬盤、液晶、網(wǎng)絡接口等)設計做了詳細介紹。本書還結(jié)合硬件設計,給出了大量用于硬件調(diào)試的代碼和驅(qū)動程序的編寫方法。

2016-04-26 11:42:13 3

3 、各類Flash、硬盤、液晶、網(wǎng)絡接口等)設計做了詳細介紹。本書還結(jié)合硬件設計,給出了大量用于硬件調(diào)試的代碼和驅(qū)動程序的編寫方法。

2016-04-26 11:42:13 3

3 基于FPGA的高速數(shù)據(jù)采集硬件系統(tǒng)設計.

2016-05-10 17:06:40 48

48 單片機系統(tǒng)軟硬件調(diào)試及維修技術,快來下載吧

2016-09-01 18:17:24 0

0 GOE219硬件調(diào)試常見問題及檢修方法

2016-12-27 16:26:44 0

0 在調(diào)試FPGA電路時要遵循必須的原則和技巧,才能降低調(diào)試時間,防止誤操作損壞電路。通常情況下,能夠參考以下步驟執(zhí)行 FPGA硬件系統(tǒng)的調(diào)試。

2017-02-11 16:18:59 990

990

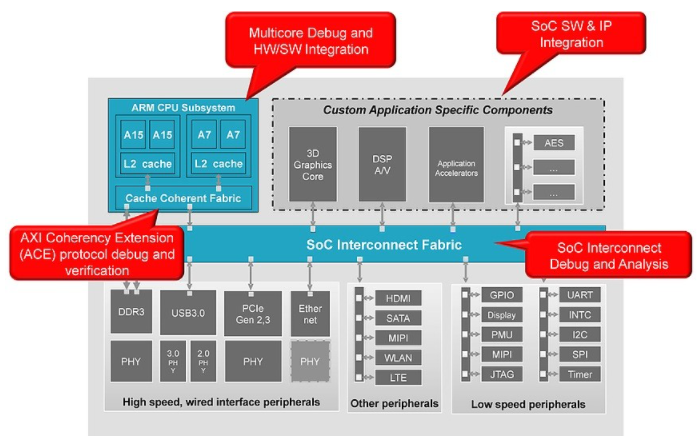

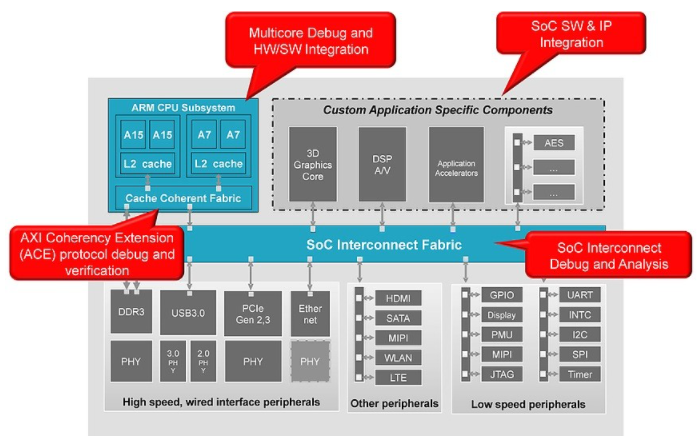

設計了一種基于FPGA的驗證平臺及有效的SoC驗證方法,介紹了此FPGA驗證軟硬件平臺及軟硬件協(xié)同驗證架構(gòu),討論和分析了利用FPGA軟硬件協(xié)同系統(tǒng)驗證SoC系統(tǒng)的過程和方法。利用此軟硬件協(xié)同驗證

2017-11-17 03:06:01 21462

21462

設計了一種基于FPGA的驗證平臺及有效的SoC驗證方法,介紹了此FPGA驗證軟硬件平臺及軟硬件協(xié)同驗證架構(gòu),討論和分析了利用FPGA軟硬件協(xié)同系統(tǒng)驗證SoC系統(tǒng)的過程和方法。利用此軟硬件協(xié)同驗證

2017-11-17 03:06:01 5210

5210

,不利于硬件的開發(fā)進度。面對這一難題,文章從FPGA 的軟硬件協(xié)同測試角度出發(fā),利用PC 機和測試硬件設備的特點,進行FPGA 的軟硬件協(xié)同測試的設計,努力實現(xiàn)FPGA 的軟硬件協(xié)調(diào)測試系統(tǒng)在軟硬件的測試和分析中的應用。

2017-11-18 05:46:28 2323

2323 本文以workbench 為平臺,vxworks 為操作系統(tǒng),chipscope 為分析工具,介紹了完整的ARINC429 協(xié)議和422協(xié)議的FPGA 硬件調(diào)試,通過硬件調(diào)試發(fā)現(xiàn)modelsim

2017-11-18 08:56:01 23632

23632

FPGA的設計速度、尺寸和復雜度明顯增加,使得整個設計流程中的驗證和調(diào)試成為當前FPGA系統(tǒng)的關鍵部分。獲得FPGA內(nèi)部信號有限、FPGA封裝和印刷電路板電氣噪聲,這一切使得設計調(diào)試和檢驗變成

2018-07-19 14:19:00 14271

14271

本文檔內(nèi)容介紹了基于chipscope使用教程以及FPGA在線調(diào)試的方法,供參考

2018-03-02 14:09:49 9

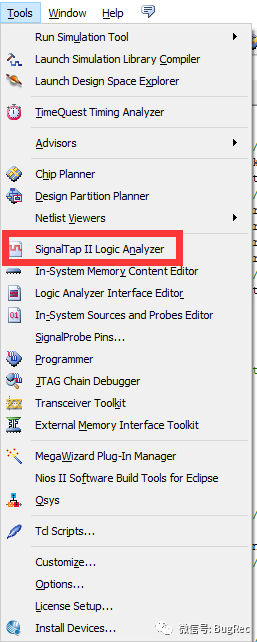

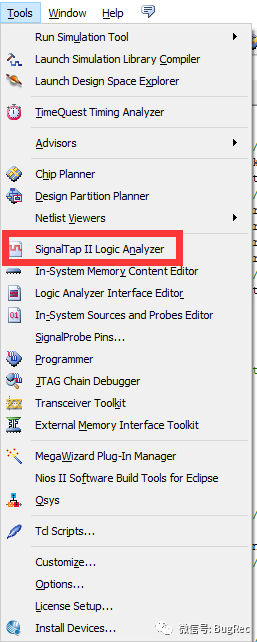

9 相信每一個電子工程師在項目開發(fā)的過程中都不可避免的要進行方案的調(diào)試,除了模擬調(diào)試我們還必須進行真機調(diào)試才能確保功能的正常,通常我們采用的調(diào)試方法分為兩種:第一種是使用硬件邏輯分析儀,第二種是采用嵌入邏輯分析IP。

2018-03-13 13:54:41 7565

7565

設計一個完整的PLC應用系統(tǒng)一般包括項目分析、PLC硬件選型、程序設計和調(diào)試等幾個步驟。

2018-05-13 10:40:41 10002

10002 本文重點介紹在調(diào)試FPGA系統(tǒng)時遇到的問題及有助于提高調(diào)試效率的技術,針對Altera和Xilinx的FPGA調(diào)試提供了最新的方法和工具。

2018-11-28 08:43:00 3254

3254

在Altera Cyclone II 平臺上采用“自頂向下”的模塊化設計思想及VHDL 硬件描述語言,設計了串行通信控制系統(tǒng)。在Quartus II 軟件上編譯、仿真后下載到FPGA 芯片

2018-11-07 11:18:23 6

6 建立了一個基于FPGA的可實現(xiàn)流水化運行的OFDM系統(tǒng)的硬件平臺,包括模擬前端、基于FPGA的OFDM調(diào)制器和OFDM 解調(diào)器。重點給出了OFDM調(diào)制解調(diào)器的實現(xiàn)構(gòu)架,對FPGA實現(xiàn)方法進行了詳細的描述,介紹了系統(tǒng)調(diào)試方法,并對系統(tǒng)進行了性能評價。

2018-12-13 16:45:51 22

22 本文檔的主要內(nèi)容詳細介紹的是FPGA硬件最小系統(tǒng)設計的詳細資料說明。

2019-02-26 14:43:46 36

36 由于目標芯片或設備在我們的桌面工作環(huán)境中屬于“外來”元素,因此在目標硬件上調(diào)試軟件會面臨一系列不同的挑戰(zhàn)。桌面工作環(huán)境及其操作系統(tǒng)對自身的計算引擎(在一定程度上)有所了解,但通常沒有訪問外部硬件內(nèi)部狀態(tài)的通用方法。

2019-03-26 10:46:19 3606

3606 本文檔的主要內(nèi)容詳細介紹的是FPGA教程之FPGA硬件最小系統(tǒng)設計的詳細資料說明包括了:1.FPGA最小系統(tǒng)概念以及硬件系統(tǒng)的構(gòu)成,2.FPGA主芯片電路設計,3.JTAG下載與調(diào)試接口,4.高速

2019-04-04 17:18:48 110

110 本文檔的主要內(nèi)容詳細介紹的是FPGA教程之FPGA系統(tǒng)設計的主要思路和方法初探資料說明包括了:1.FPGA的適用領域及選型FPGA系統(tǒng)設計典型流程,2.FPGA邏輯設計方法 弓|入ASIC的設計方法,3.FPGA設計的常用技巧,4.FPGA系統(tǒng)設計中的對與錯

2019-04-04 17:19:58 55

55 本文檔的詳細介紹的是FPGA設計有哪些良好的設計方法及誤區(qū)內(nèi)容包括了:1.FPGA的適用領域及選型,2.FPGA系統(tǒng)設計典型流程,3.FPGA邏輯設計良好設計方法一引入ASIC的設計方法,4.FPGA設計的常用技巧,5.FPGA系統(tǒng)設計中的誤區(qū)

2019-04-18 17:30:04 23

23 對于FPGA調(diào)試,主要以Intel FPGA為例,在win10 Quartus ii 17.0環(huán)境下進行仿真和調(diào)試,開發(fā)板類型EP4CE15F17。

2020-03-29 11:37:00 1630

1630 進行硬件設計的功能調(diào)試時,FPGA的再編程能力是關鍵的優(yōu)點。CPLD和FPGA早期使用時,如果發(fā)現(xiàn)設計不能正常工作,工程師就使用“調(diào)試鉤”的方法。先將要觀察的FPGA內(nèi)部信號引到引腳,然后用外部的邏輯分析儀捕獲數(shù)據(jù)。

2020-09-14 15:08:00 909

909

調(diào)試一直是嵌入式系統(tǒng)開發(fā)的難題。開發(fā)者往往直接面對嵌入式開發(fā)硬件進行開發(fā),就算目標嵌入式環(huán)境中引入了操作系統(tǒng),其功能通常也有一定的限制,不能方便地進行調(diào)試。而且,引入嵌入式操作系統(tǒng)的過程中的調(diào)試問題也很棘手。遠程調(diào)試是解決此類問題的首選方案。

2020-09-15 17:42:09 3028

3028

FPGA概述FPGA調(diào)試介紹調(diào)試挑戰(zhàn)設計流程概述■FPGA調(diào)試方法概述嵌入式邏輯分析儀外部測試設備■使用 FPGAVIEW改善外部測試設備方法■FPGA中高速O的信號完整性測試和分析

2020-09-22 17:43:21 12

12 在線調(diào)試也稱作板級調(diào)試,它是將工程下載到FPGA芯片上后分析代碼運行的情況。

2020-11-01 10:00:49 5442

5442

基于FPGA的神經(jīng)網(wǎng)絡硬件實現(xiàn)方法說明。

2021-06-01 09:35:16 51

51 單片機系統(tǒng)硬件的靜態(tài)調(diào)試和動態(tài)調(diào)試綜述

2021-07-18 10:59:14 3

3 下載硬件配置數(shù)據(jù)。啟動程序中的錯誤可能會導致CPU停機。您可以使用模塊信息工具來診斷和消除編程錯誤。 通過執(zhí)行用戶程序來檢查系統(tǒng)的功能,可以在組織塊OB1中逐個調(diào)用各個邏輯塊,逐步調(diào)試程序。對程序的更改應在調(diào)試期間保存。調(diào)試后,保存調(diào)試

2022-01-04 14:08:41 5049

5049 使用Jtag Master調(diào)試FPGA程序時用到tcl語言,通過編寫tcl腳本,可以實現(xiàn)對FPGA的讀寫,為調(diào)試FPGA程序帶來極大的便利,下面對FPGA調(diào)試過程中常用的tcl語法進行介紹,并通過tcl讀FIFO的例子,說明tcl在實際工程中的應用。

2022-02-19 19:44:34 3645

3645 SoC 是一個成熟的嵌入式系統(tǒng),需要硬件仿真來驗證它是否正常工作。借助硬件仿真,開發(fā)團隊可以更有策略地規(guī)劃并實施基于多個抽象級別的調(diào)試方法。

2022-06-19 15:30:17 2425

2425 Debug 有幾個層次,通常構(gòu)建在 Eclipse 等集成開發(fā)環(huán)境 (IDE) 上。用戶需要調(diào)試實際的硬件、操作系統(tǒng)之外的裸機軟件執(zhí)行、硬件和軟件的結(jié)合以及整個系統(tǒng)的性能。

2022-07-09 06:50:00 2257

2257

我們在編寫裸機程序(baremetal)、虛擬化管理程序(hypervisor)和操作系統(tǒng)(OS)時,Debug分析程序是必不可少的。不像linux內(nèi)核,有大量的調(diào)試方法,很多裸機程序、hypervisor沒有完善的調(diào)試分析方法。

2022-10-08 09:40:21 2260

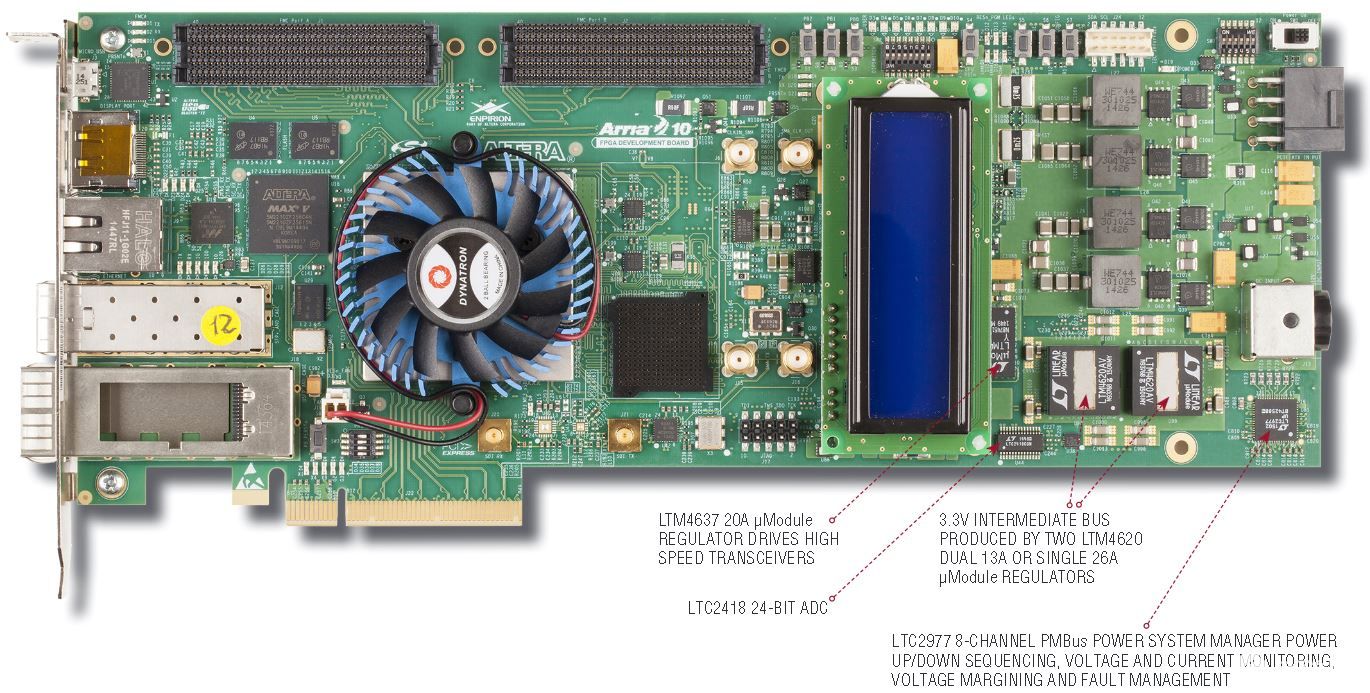

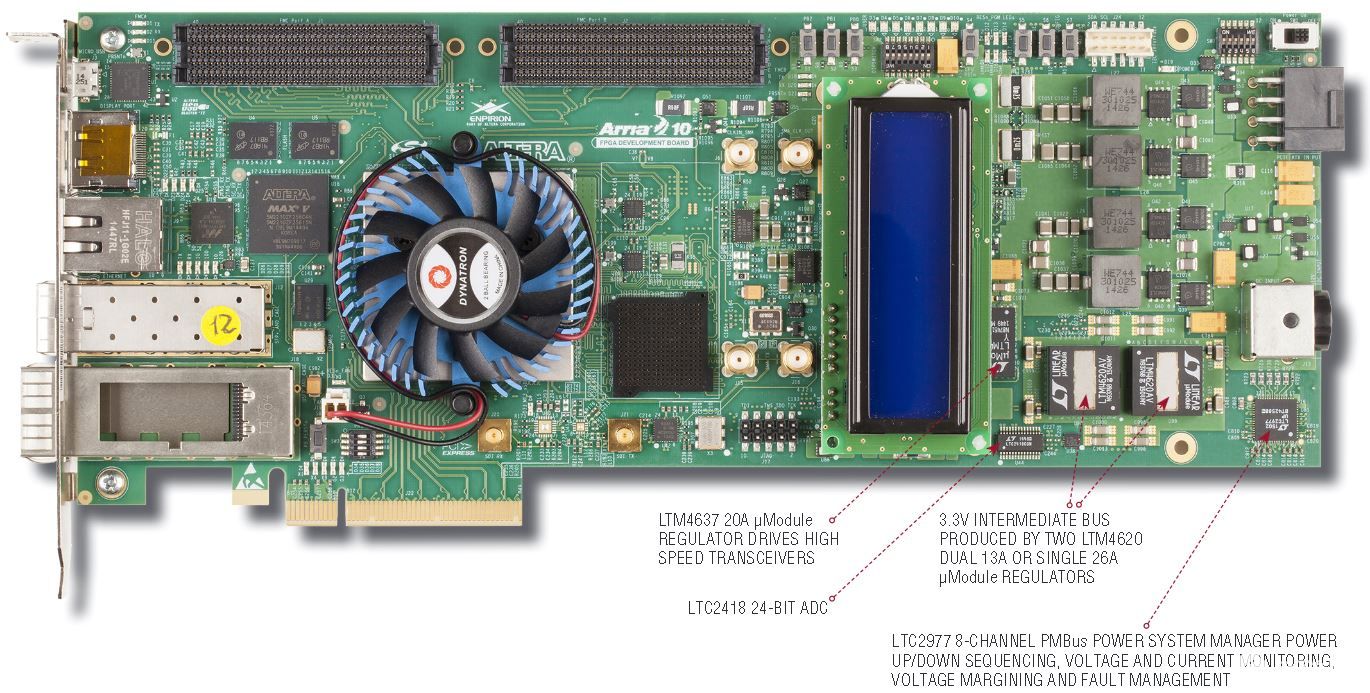

2260 在設計FPGA、GPU或ASIC控制系統(tǒng)時,與數(shù)字設計相關的電源管理和模擬系統(tǒng)相關的設計挑戰(zhàn)數(shù)量相形見絀。然而,假設電源系統(tǒng)設計可以留給“以后”或與數(shù)字設計保持一致是有風險的。即使是電源設計中看似無害的問題也會顯著延遲系統(tǒng)的發(fā)布,因為電源系統(tǒng)調(diào)試周期的任何增加時間都可能停止數(shù)字端的所有工作。

2023-01-06 09:24:07 1866

1866

系統(tǒng)調(diào)試是系統(tǒng)正式投入使用前的必要步驟。與繼電器和接觸器控制系統(tǒng)不同,plc控制系統(tǒng)有硬件調(diào)試和軟件調(diào)試。與

繼電器-接觸器控制系統(tǒng)相比,PLC控制系統(tǒng)的硬件調(diào)試相對簡單,主要是PLC程序的調(diào)試

2023-04-18 09:49:45 11

11 Xilinx被AMD收購的事情把我震出來了,看了看上上一篇文章講了下仿真的文件操作,這篇隔了很久遠,不知道該從何講起,就說說FPGA的在線調(diào)試的一些簡單的操作方法總結(jié)。

2023-06-19 15:52:21 2703

2703

引言Preface隨著芯片設計規(guī)模的增加,傳統(tǒng)基于單顆FPGA的設計調(diào)試方法已經(jīng)不能滿足對大型設計的調(diào)試需求,因此多FPGA聯(lián)合調(diào)試技術應運而生。本次國微思爾芯白皮書《先進多FPGA聯(lián)合深度調(diào)試方法

2022-06-16 10:16:48 1693

1693

之前的文章介紹了FPGA在線調(diào)試的方法,包括選定抓取信號,防止信號被優(yōu)化的方法等等。

2023-06-20 10:38:48 9670

9670

1 推動FPGA調(diào)試技術改變的原因 進行硬件設計的功能調(diào)試時,FPGA的再編程能力是關鍵的優(yōu)點。CPLD和FPGA早期使用時,如果發(fā)現(xiàn)設計不能正常工作,工程師就使用“調(diào)試鉤”的方法。先將要觀察

2023-12-20 13:35:01 1207

1207

在調(diào)試FPGA電路時要遵循必須的原則和技巧,才能降低調(diào)試時間,防止誤操作損壞電路。通常情況下,參考以下步驟執(zhí)行 FPGA硬件系統(tǒng)的調(diào)試。 1、在焊接硬件電路前,首先要測試電路板的各個電源之間,各電源

2023-12-22 16:40:01 1607

1607

FPGA(現(xiàn)場可編程門陣列)和DSP(數(shù)字信號處理器)之間通過SRIO接口進行調(diào)試通常需要以下步驟。

2024-04-19 11:48:46 2570

2570 電子發(fā)燒友網(wǎng)站提供《FPD link系統(tǒng)概念與診斷調(diào)試方法.pdf》資料免費下載

2024-09-27 11:11:06 0

0 硬件調(diào)試是硬件系統(tǒng)設計、開發(fā)和制造過程中不可或缺的一環(huán),旨在對可能出現(xiàn)的問題進行分析和解決。以下是進行硬件調(diào)試的一般步驟和方法: 一、準備階段 熟悉設計文檔:在開始調(diào)試之前,需要詳細閱讀和理解硬件

2024-11-10 10:17:40 2894

2894

摘要: 本文深入探討了 JLink 調(diào)試器在嵌入式系統(tǒng)硬件調(diào)試中的應用,詳細闡述了 JLink 驅(qū)動配置的方法以及硬件調(diào)試技巧。本文以國科安芯的AS32系列MCU芯片為例,通過分析 JLink

2025-06-12 23:20:26 1405

1405

電子發(fā)燒友App

電子發(fā)燒友App

評論