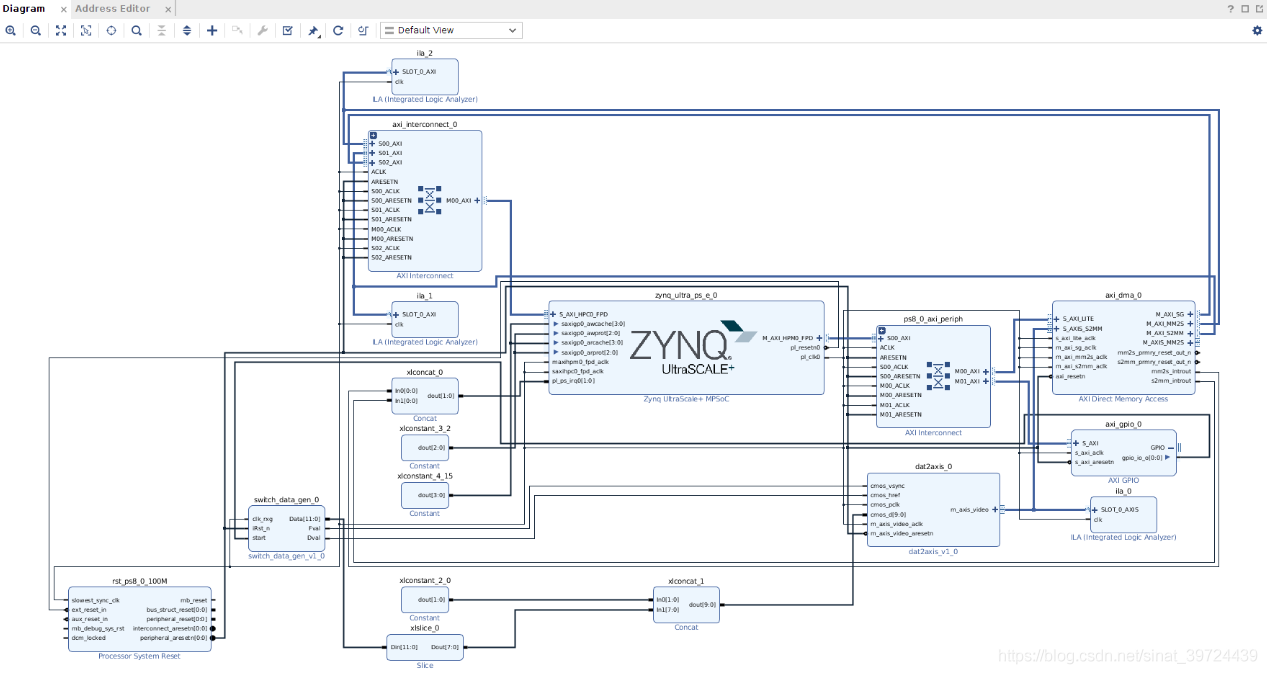

添加Zynq Processing System IP核,配置DDR控制器 和時鐘。7000系列的Zynq可以參考正點原子DMA 回環(huán)測試設(shè)置。

2025-11-24 09:25:50 2891 microblaze和jtag-to-axi (jtag2axi )雖然也提供了訪問axi 總線 的能力,但是依賴于xilinx平臺。而uart-to-axi (uart2axi 4)橋接器并不依賴任何平臺

2025-12-02 10:05:43 1846 AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一種總線 協(xié)議, Xilinx從 6 系列的 FPGA 開始對 AXI 總線 提供支持,目前使用 AXI

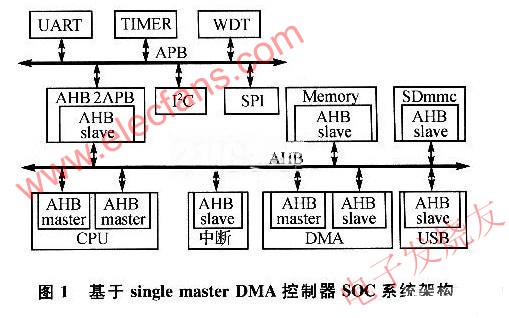

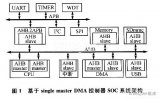

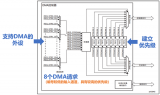

2020-12-04 12:22:44 9055 斷給中斷控制器 ; 5. 擁有8個DMA 觸發(fā)事件并且可以編碼控制 ; 6. 128個(64bit)的MFIFO,在傳輸?shù)臅r候讀寫端可寫入到此FIFO; 7. 支持任意內(nèi)存到內(nèi)存的傳輸; 整個系統(tǒng)中的DMA

2020-12-05 10:17:17 5268 前面一節(jié)我們學(xué)會了創(chuàng)建基于AXI 總線 的IP,但是對于AXI 協(xié)議各信號的時序還不太了解。這個實驗就是通過SDK和Vivado聯(lián)合調(diào)試觀察AXI 總線 的信號。由于我們創(chuàng)建的接口是基于AXI _Lite協(xié)議

2020-12-23 15:32:37 3253 構(gòu)成的傳輸數(shù)據(jù)的通道, 一般由數(shù)據(jù)線、地址線、 控制 線構(gòu)成。?Xilinx從6系列的 FPGA 開始對 AXI 總線 提供支持, 此時 AXI 已經(jīng)發(fā)展到

2020-12-25 14:07:02 6725 一、AXI DMA 介紹 本篇博文講述AXI DMA 的一些使用總結(jié),硬件IP子系統(tǒng)搭建與SDK C代碼封裝參考米聯(lián)客ZYNQ教程。若想讓ZYNQ的PS與PL兩部分高速數(shù)據(jù)傳輸,需要利用PS的HP

2020-12-31 09:52:02 10715 這篇應(yīng)用筆記描述了怎么使用STM32F101xx和STM32F103xx的直接內(nèi)存訪問(DMA )控制器 。STM32F101xx和STM32F103xx DMA 控制器 、Cortex-M3內(nèi)核、先進(jìn)

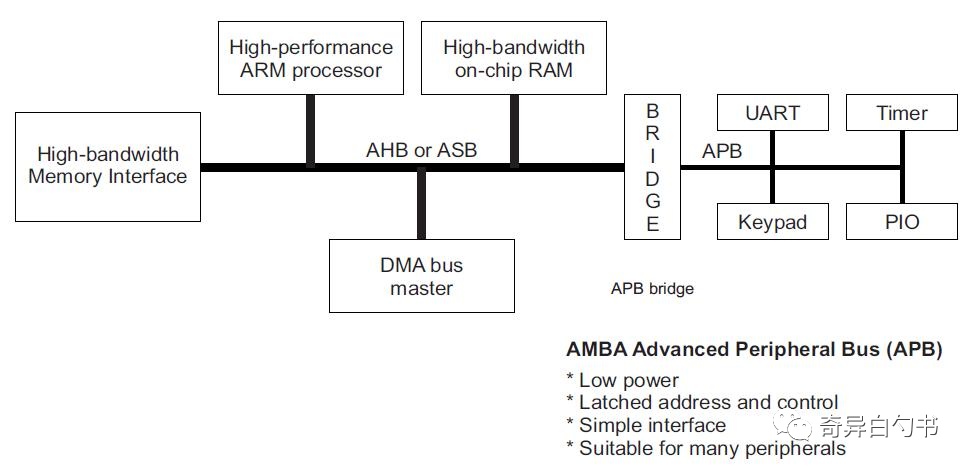

2022-12-23 11:42:28 2048 AMBA(Advanced Micro-Controller Bus Architecture,高級微控制器 總線 架構(gòu))是由ARM公司開發(fā)的片上總線 標(biāo)準(zhǔn)。主要包括APB(Advanced

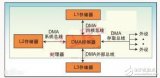

2023-09-19 09:24:49 3281 ,SG)功能還可以將數(shù)據(jù)移動任務(wù)從位于于處理器 系統(tǒng)中的中央處理器 (CPU)中卸載出來。可以通過一個AXI 4-Lite從接口訪問初始化、狀態(tài)和管理寄存器 。如圖4. 8展現(xiàn)了DMA IP的功能構(gòu)成核心。

2025-04-03 09:32:24 2246 本帖最后由 yyeee312 于 2015-11-12 15:17 編輯

DMA 控制器 是一種在系統(tǒng)內(nèi)部轉(zhuǎn)移數(shù)據(jù)的獨特外設(shè),可以將其視為一種能夠通過一組專用總線 將內(nèi)部和外部存儲器 與每個具有DMA

2015-11-04 22:50:56

;獨立的控制 和狀態(tài)流通道,提供相關(guān)的包信息;DMA 的中斷與系統(tǒng)中斷控制器 相連。 (2) AXI Centralized DMA 圖4?41 AXI CDMA 在此系統(tǒng)中,AXI CDMA與處理器

2020-12-23 17:48:04

CoreLink DMA -350是一款具有AMBA?AXI 5接口的直接內(nèi)存訪問控制器 (DMAC),

它提供快速存儲器 到存儲器 、外圍設(shè)備到存儲器 、存儲器 到外圍設(shè)備拷貝,以及

多個通道上的外設(shè)到外設(shè)能力

2023-08-02 08:03:53

EtherCAT總線 運(yùn)動控制器 硬件是如何進(jìn)行接線的?EtherCAT總線 運(yùn)動控制器 有哪些參數(shù)設(shè)置?

2021-07-15 13:02:24

的理解:1)DMA 連接到IP總線 。2)OCRAM連接到AXI 64總線 。3) ITCM和DTCM連接到TCM接口。是否可以將 DMA 緩沖區(qū)放在 OCRAM 中,將任務(wù)的緩沖區(qū)放在 DTCM 或 ITCM

2023-04-04 07:09:50

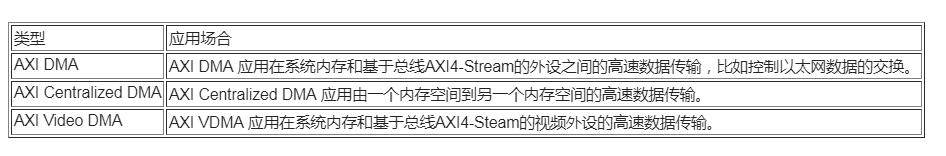

向高速數(shù)據(jù)流傳輸?shù)?b class="flag-6" style="color: red">AXI4-Stream接口。如表1所示展示了三種類型接口的主要特點對比。

表1 三種類型AXI 4接口對比

AXI 4總線 具有讀寫地址、數(shù)據(jù)通道分離的特性,使控制 通道與數(shù)據(jù)通道分離、讀通道

2025-05-17 10:27:56

我已經(jīng)通過AXI 互連將用于PCI Express的DMA 子系統(tǒng)連接到DDR4控制器 IP。然而,這是在塊設(shè)計之外完成的。實際上我沒有使用塊設(shè)計。如果我使用塊設(shè)計,地址編輯器 將出現(xiàn)在一個選項卡中,可以指定每個塊的AXI 地址。但是如果沒有塊設(shè)計,我該如何打開地址編輯器 ?

2020-05-08 07:30:19

的請求,還有一個仲裁器 來協(xié)調(diào)各個DMA 請求的優(yōu)先權(quán)。DMA 控制器 和Cortex-M3核共享系統(tǒng)數(shù)據(jù)總線 執(zhí)行直接存儲器 數(shù)據(jù)傳輸。當(dāng)CPU和DMA 同時訪問相同的目標(biāo)(RAM或外設(shè))時,DMA 請求可能會

2015-01-13 14:02:03

4 Host Controller IP作為一個對PCIe SSD的高性能存儲控制器 ,不但提供對PCIe SSD的配置管理功能,而且提供對PCIe SSD的IO(Page)讀寫以及DMA 讀寫功能。NVMe

2025-11-14 22:40:50

我正在使用ZC706套件和ISE14.4。我在PL中使用XPS生成AXI .DDR控制器 。 AXI .DDR控制器 的S_AXI 總線 通過AXI 互連連接到M_AXI _GP1。當(dāng)我在板上運(yùn)行它時,我看到

2019-09-10 07:58:12

DMA 控制器 的主要特性有哪些?DMA 控制器 通道的配置過程該怎樣去完成呢?

2021-12-13 06:12:53

這篇應(yīng)用筆記描述了怎么使用STM32F101xx 和 STM32F103xx的直接存儲器 訪問(DMA )控制器 。STM32F101xx和STM32F103xx的DMA 控制器 、CortexTM-M3內(nèi)核

2023-10-10 08:20:48

它們?nèi)绾斡糜诮涌赟oC組件。圖6.AXI 互連(AXI 4規(guī)范)結(jié)論在本文中,我們介紹了高級微控制器 總線 體系結(jié)構(gòu)或AMBA。AMBA是一個開放標(biāo)準(zhǔn),概述了SoC上的組件如何快速有效地交換數(shù)據(jù)。AMBA

2020-09-28 10:16:11

的控制 和狀態(tài)流通道,提供相關(guān)的包信息;DMA 的中斷與系統(tǒng)中斷控制器 相連。(2) AXI Centralized DMA 圖4?41 AXI CDMA在此系統(tǒng)中,AXI CDMA與處理器 等設(shè)備通過AXI

2022-10-14 15:23:41

我需要設(shè)計一個Zynq(可能是Zynq-7030)主板,支持ARM處理器 的SATA硬盤驅(qū)動器 。我想知道是否可以用GTX收發(fā)器 實現(xiàn)SATA控制器 并將其連接到芯片中的AXI 總線 。是否有任何參考設(shè)計或評估板支持此功能?

2020-07-29 10:28:58

EtherCAT總線 擴(kuò)展模塊包含哪些?怎樣去使用正運(yùn)動技術(shù)運(yùn)動控制器 EtherCAT總線 ?

2021-09-27 08:34:04

直接存儲器 存取DMACPU太忙了,那DMA 你來幫我吧,這樣很多事情CPU就不用停下來去管了。在DMA 模式下,CPU只須向DMA 控制器 下達(dá)指令,讓DMA 控制器 來處理數(shù)據(jù)的傳送,數(shù)據(jù)傳送完畢再把信息反饋

2021-12-09 06:00:30

eXtensibleInterface)協(xié)議是一種面向高性能、高帶寬系統(tǒng)設(shè)計的總線 協(xié)議,能夠滿足各種高速系統(tǒng)的總線 互聯(lián)。AXI 協(xié)議的主要特點有:●獨立的地址、控制 和數(shù)據(jù)接口●支持使用字節(jié)選通的不對齊數(shù)據(jù)的傳輸

2019-05-06 16:55:32

你好,我正在設(shè)計一個 PMSM 電機(jī)控制器 ,我有一個問題,PMSM控制器 需要直流總線 紋波補(bǔ)償嗎?

2024-01-22 07:56:17

CAN總線 控制器 Verilog代碼

2008-05-20 10:32:12 170 DMA (Direct Memory Access)的概念DMA 方式不用處理器 干預(yù)完成M與I/O間數(shù)據(jù)傳送。DMA 期間系統(tǒng)總線 由其它主模塊控

2008-12-09 11:03:56 50 8237可編程DMA 控制器 資料與程序代碼:核心是在AL8237的VHDL模型英特爾。 8237是4通道的DMA 可編程,控制器 控制 存儲器 內(nèi)存和存儲器 和外設(shè)的數(shù)據(jù)傳輸,提供塊內(nèi)存初始化能力。 特征

2009-04-19 23:28:07 70 本文在PCI2.2 總線 規(guī)范的基礎(chǔ)上,給出了一種PCI 總線 目標(biāo)控制器 的設(shè)計方案。重點從控制 邏輯和數(shù)據(jù)通路的建立上闡述了目標(biāo)控制器 的設(shè)計:用狀態(tài)機(jī)實現(xiàn)總線 訪問操作的復(fù)雜時

2009-12-12 16:58:25 33 本文介紹了一種新型數(shù)字信號控制器 dsPIC33FJ256GP710的性能特點,重點講述了使用其直接存儲器 訪問(DMA )控制器 設(shè)計UART通訊模塊的原理和方法,通過其在車輛電源檢測和故障診斷系統(tǒng)中的

2010-02-24 14:09:17 67 利用單總線 控制器 通訊

本示例的程序采用C 語言編寫,主程序為:“Get Temperature”(獲取溫度),它完成1-Wire 控制器 的初始化,搜索1-Wire 總線 上的所有器件,

2010-03-18 10:05:38 27 引言

DMA (Direct Memory Access,直接存儲器 存取)是一種快速傳送數(shù)據(jù)的機(jī)制。DMA 控制器 能夠有效替代微處理器 的加載/存儲指令,顯著提高系統(tǒng)的并行能力。DMA 是在

2010-09-08 11:08:36 2748 在以SD卡為圖像存儲器件的圖像協(xié)處理器 中,基帶芯片和SD卡控制器 在速度上的差異經(jīng)常會導(dǎo)致數(shù)據(jù)傳輸錯誤。為解決此問題,設(shè)計了一種可適應(yīng)多種時序情況的DMA 控制器 。該DMA 控制器 的狀態(tài)機(jī),一方面對基帶芯片和SD卡控制器 的操作請求進(jìn)行仲裁,在響應(yīng)基帶芯片請

2011-01-15 17:06:20 0 本文所設(shè)計的可適應(yīng)于多種時序情況的DMA 控制器 ,被應(yīng)用于該圖像協(xié)處理器 之中后,能夠很好地解決上述問題。

2011-03-26 11:39:55 3833 針對大數(shù)據(jù)量的串口間通信,在常規(guī)的UART串行數(shù)據(jù)通信的基礎(chǔ)上,結(jié)合Cortex-M3微控制器 中DMA 控制器 的作用,實現(xiàn)DMA 控制 的UART串口數(shù)據(jù)包收發(fā)。設(shè)計鏈表項緩存,最終實現(xiàn)DMA 的分散/聚集

2012-04-20 10:54:07 46 AMBA AXI 總線 學(xué)習(xí)筆記,非常詳細(xì)的AXI 總線 操作說明

2015-11-11 16:49:33 12 基于ISA總線 的同步通信控制器

2017-02-07 18:09:20 11 上周的博客中我們完成了硬件的搭建,并且把硬件部分導(dǎo)入到SDK,見Adam Taylor’s MicroZed Chronicles Part 67: AXI DMA II,下一步通過寫一個簡單的程序

2017-02-08 05:53:11 565 上周的博客中我們學(xué)習(xí)了Zynq SoC的AXI DMA ,我解釋了怎樣利用AXI DMA 控制器 將數(shù)據(jù)從PL搬運(yùn)到PS。在本期博客中我們將學(xué)習(xí)怎樣完成硬件的搭建。 首先我們要更深入的了解一下AXI

2017-02-08 08:10:39 527 本文主要介紹zynq linux AXI DMA 傳輸步驟教程,具體的跟隨小編一起來了解一下。

2018-07-08 05:46:00 32067 DMA 控制器 在外設(shè)與主存之間直接傳送數(shù)據(jù)期間,完全代替 CPU 進(jìn)行工作。

2017-09-19 16:11:03 6 AXI 總線 的MicroBlaze雙核SoPC系統(tǒng)設(shè)計

2017-10-31 08:54:44 8 采用并行DMA 數(shù)據(jù)傳輸可選擇MCU加DMA 芯片和具有內(nèi)部DMA 控制器 的CPU兩種方案,從系統(tǒng)結(jié)構(gòu)和成本以及開發(fā)復(fù)雜度方面考慮,后者更加合理。由于使用硬件DMA 并行傳輸列數(shù)據(jù),將LED顯示屏上

2017-12-06 10:15:32 3917 在某些單片機(jī)應(yīng)用系統(tǒng)中,往往需要解決外部設(shè)備與存儲貯器 之間快速傳送數(shù)據(jù)的問題。為此,本文研究了DMA 控制器 8237與單片機(jī)8031的接口技術(shù)。

2017-12-06 11:28:42 3751 DMA 控制器 是常見的總線 設(shè)備之一,很多廠商都有自己的DMA 控制器 IP核。比如嵌入式處理器 的龍頭ARM公司就有自己的DMA 控制器 解決方案提供給客戶,另外像Freescale,F(xiàn)ujitsu等芯片

2017-12-06 13:41:59 4364 介紹一種基于PCI總線 的高效鏈?zhǔn)?b class="flag-6" style="color: red">DMA控制器 的設(shè)計與實現(xiàn),用于高速寬帶的計算機(jī)外設(shè)接口。利用Altera公司的PCI核——PCI_MT32搭建基于此控制器 的數(shù)據(jù)采集平臺,并成功應(yīng)用在DVB數(shù)據(jù)接收卡中。

2017-12-06 13:56:13 3651 詳細(xì)地分析了PC/AT機(jī)系統(tǒng)的DMA (直接存儲器 存取)控制器 結(jié)構(gòu)及其傳輸方式,并給出了C語言編程實例。

2017-12-06 16:12:57 9663 DMA (Direct Memory Access)

控制器 是一種在系統(tǒng)內(nèi)部轉(zhuǎn)移數(shù)據(jù)的獨特外設(shè),可以將其視為一種能夠通過一組專用

總線 將內(nèi)部和外部存儲

器 與每個具有

DMA 能力的外設(shè)連接起來的

控制器 。它之所以屬于外設(shè),是因為它是在處理

器 的編程

控制 下來 執(zhí)行傳輸?shù)摹?/div>

2017-12-06 19:19:12 4196 DMA 控制器 是一種在系統(tǒng)內(nèi)部轉(zhuǎn)移數(shù)據(jù)的獨特外設(shè),可以將其視為一種能夠通過一組專用

總線 將內(nèi)部和外部存儲

器 與每個具有

DMA 能力的外設(shè)連接起來的

控制器 。它之所以屬于外設(shè),是因為它是在處理

器 的編程

控制 下來 執(zhí)行傳輸?shù)摹?/div>

2017-12-07 08:51:27 3069 為了具體介紹本多通道 DMA 控制器 的設(shè)計方案,下面首先對基于 Crossbar 的多通道 DMA 控制器 的工作原理進(jìn)行詳細(xì)分析,接著具體說明各個模塊的設(shè)計實現(xiàn),然后對設(shè)計進(jìn)行驗證和分析比較實驗結(jié)果,并進(jìn)行總結(jié)。

2017-12-07 09:37:22 5581 DMA 既可以指內(nèi)存和外設(shè)直接存取數(shù)據(jù)這種內(nèi)存訪問的計算機(jī)技術(shù),又可以指實現(xiàn)該技術(shù)的硬件模塊(對于通用計算機(jī)PC而言,DMA 控制 邏輯由CPU和DMA 控制 接口邏輯芯片共同組成,嵌入式系統(tǒng)的DMA 控制器 內(nèi)建在處理器 芯片內(nèi)部,一般稱為DMA 控制器 ,DMAC)。

2017-12-07 10:23:24 18167 DMA (Direct Memory Access)

控制器 是一種在系統(tǒng)內(nèi)部轉(zhuǎn)移數(shù)據(jù)的獨特外設(shè),可以將其視為一種能夠通過一組專用

總線 將內(nèi)部和外部存儲

器 與每個具有

DMA 能力的外設(shè)連接起來的

控制器 。它之所以屬于外設(shè),是因為它是在處理

器 的編程

控制 下來 執(zhí)行傳輸?shù)摹?/div>

2017-12-07 14:24:22 51929 DMA (Direct Memory Access)

控制器 是一種在系統(tǒng)內(nèi)部轉(zhuǎn)移數(shù)據(jù)的獨特外設(shè),可以將其視為一種能夠通過一組專用

總線 將內(nèi)部和外部存儲

器 與每個具有

DMA 能力的外設(shè)連接起來的

控制器 。它之所以屬于外設(shè),是因為它是在處理

器 的編程

控制 下來 執(zhí)行傳輸?shù)摹?/div>

2017-12-07 14:43:14 4158 DMA 控制器 是一種在系統(tǒng)內(nèi)部轉(zhuǎn)移數(shù)據(jù)的獨特外設(shè),可以將其視為一種能夠通過一組專用

總線 將內(nèi)部和外部存儲

器 與每個具有

DMA 能力的外設(shè)連接起來的

控制器 。它之所以屬于外設(shè),是因為它是在處理

器 的編程

控制 下來 執(zhí)行傳輸?shù)摹?/div>

2017-12-07 15:41:09 4064 DMA 既可以指內(nèi)存和外設(shè)直接存取數(shù)據(jù)這種內(nèi)存訪問的計算機(jī)技術(shù),又可以指實現(xiàn)該技術(shù)的硬件模塊(對于通用計算機(jī)PC而言,DMA 控制 邏輯由CPU和DMA 控制 接口邏輯芯片共同組成,嵌入式系統(tǒng)的DMA 控制器 內(nèi)建在處理器 芯片內(nèi)部,一般稱為DMA 控制器 ,DMAC)。

2017-12-07 16:08:38 6075 基于前面對DMA 控制器 工作流程的詳細(xì)分析。運(yùn)用SystemC 語言,建立DMA 控制器 的Cye le-Accurat級參考模型。控制器 由以下幾個模塊組成:寄存器 賦值、狀態(tài)轉(zhuǎn)換。輸出模塊和頂層模塊。具體工作過程可以參考如圖3所示的有限狀態(tài)機(jī)

2017-12-07 16:21:12 3549 1、AXI 總線 通道,總線 和引腳的介紹 AXI 接口具有五個獨立的通道: (1)寫地址通道(AW):write address channel (2)寫數(shù)據(jù)通道( W): write data

2018-01-05 08:13:47 11271 本文實現(xiàn)的基于FPGA的PCIe總線 接口的DMA 控制器 是在Altera PHY IP和Synopsys Core IP的基礎(chǔ)上實現(xiàn)的,利用Synopsys VIP驗證環(huán)境進(jìn)行了功能仿真驗證,并

2018-01-11 10:57:04 14735 直接存儲器 訪問(Direct Memory Access,DMA )控制器 是總線 主模塊,用于無需 CPU 干預(yù)的情況下在不同外設(shè)之間傳輸數(shù)據(jù)。 DMA 傳輸?shù)脑春湍繕?biāo)可以是 PIC32 系列器件中包含

2018-06-06 13:29:00 6 在圖1所示架構(gòu)中,每次DMA 傳輸都要發(fā)起1次讀與1次寫操作。若在DMA 傳輸期間有需要緊急處理的異常響應(yīng),AHB總線 此時又被DMA 控制器 占用,則處理器 只能等DMA 控制器 釋放AHB總線 后才能占用AHB總線 進(jìn)行操作,影響處理器 效率與系統(tǒng)對異步事件的響應(yīng)速度。

2018-08-24 15:34:53 2442 一個DMA 控制器 ,實際上是采用DMA 方式的外圍設(shè)備與系統(tǒng)總線 之間的接口電路,這個接口電路是在中斷接口的基礎(chǔ)上再加DMA 機(jī)構(gòu)組成。習(xí)慣上將DMA 方式的接口電路稱為DMA 控制器 。

2019-04-01 16:08:06 12132 DMA (Direct Memory Access)

控制器 是一種在系統(tǒng)內(nèi)部轉(zhuǎn)移數(shù)據(jù)的獨特外設(shè),可以將其視為一種能夠通過一組專用

總線 將內(nèi)部和外部存儲

器 與每個具有

DMA 能力的外設(shè)連接起來的

控制器 。它之所以屬于外設(shè),是因為它是在處理

器 的編程

控制 下來 執(zhí)行傳輸?shù)摹?/div>

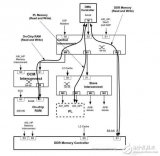

2019-11-15 10:25:56 14180 在ZYNQ中,支持AXI -Lite,AXI 4和AXI -Stream三種總線 ,但PS與PL之間的接口卻只支持前兩種,AXI -Stream只能在PL中實現(xiàn),不能直接和PS相連,必須通過AXI -Lite或

2020-09-24 09:50:30 7203 XDMA是Xilinx封裝好的PCIE DMA 傳輸IP,可以很方便的把PCIE總線 上的數(shù)據(jù)傳輸事務(wù)映射到AXI 總線 上面,實現(xiàn)上位機(jī)直接對AXI 總線 進(jìn)行讀寫而對PCIE本身TLP的組包和解包無感。

2020-12-28 10:17:23 4193 不同類型的DMA GPIO PL general purpose AXI GP AXI utlilizing PS DMAC High performance w/DMA ACP w/DMA 幾種

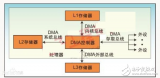

2020-10-09 18:05:57 8939 基于AXI 的DMA 對內(nèi)部寄存器 的讀寫有著相同的方式。在普通傳輸模式下,DMA 內(nèi)部的寄存器 都是由處理器 通過AXI -Lite總線 進(jìn)行讀寫的;但基于AXI 總線 的三種DMA,都增加了S/G傳輸模式,它卸載了

2020-10-10 10:23:37 7887 ZYNQ中DMA 與AXI 4總線 為什么在ZYNQ中DMA 和AXI 聯(lián)系這么密切?通過上面的介紹我們知道ZYNQ中基本是以AXI 總線 完成相關(guān)功能的: 圖4?34連接 PS 和 PL 的 AXI 互聯(lián)

2020-11-02 11:27:51 5033 在 AMBA 系列之 AXI 總線 協(xié)議初探 中,了解到 AXI 總線 交互分為 Master / Slave 兩端,而且標(biāo)準(zhǔn)的 AXI 總線 支持不同的位寬,既然是總線 ,那么必須要支持總線 互聯(lián),多 Master,多 Slave的場景

2022-02-08 11:44:02 18240 在介紹AXI 之前,先簡單說一下總線 、接口以及協(xié)議的含義。總線 、接口和協(xié)議,這三個詞常常被聯(lián)系在一起,但是我們心里要明白他們的區(qū)別。

2021-02-04 06:00:15 10 AXI 是個什么東西呢,它其實不屬于Zynq,不屬于Xilinx,而是屬于ARM。它是ARM最新的總線 接口,以前叫做AMBA,從3.0以后就稱為AXI 了。

2021-04-09 17:10:10 7245 本文介紹了AMBA 3.0 AXI 的結(jié)構(gòu)和特點,分析了新的AMBA 3.0 AXI 協(xié)議相對于AMBA 2. 0的優(yōu)點。它將革新未來高性能SOC總線 互連技術(shù),其特點使它更加適合未來的高性能、低延遲

2021-04-12 15:47:39 28 Petalinux 加速axi-dma 內(nèi)核驅(qū)動緩沖區(qū)讀過程

2022-02-16 16:21:31 5094 AXI (高性能擴(kuò)展總線 接口,Advanced eXtensible Interface)是ARM AMBA 單片機(jī)總線 系列中的一個協(xié)議,是計劃用于高性能、高主頻的系統(tǒng)設(shè)計的。AXI 協(xié)議是被優(yōu)化

2022-10-10 09:22:22 11273 AN3109_用STM32F10x微控制器 的DMA 和DMA 超時仿真通信外設(shè)FIFO

2022-11-21 08:11:29 0 AN4104_STM32F0xx的DMA 控制器 的使用

2022-11-21 08:11:37 2 今天給大俠帶來基于FPGA的CAN總線 控制器 的設(shè)計,由于篇幅較長,分三篇。今天帶來第一篇,上篇,CAN 總線 協(xié)議解析以及 CAN 通信控制器 程序基本框架。話不多說,上貨。

2023-05-18 09:21:30 2346 在zynq開發(fā)過程中,AXI 總線 經(jīng)常遇到,每次看到AXI 總線 相關(guān)的信號時都一頭霧水,仔細(xì)研究一下,將信號分分類,發(fā)現(xiàn)其實也不難。

2023-05-25 11:22:54 1790 從 FPGA 應(yīng)用角度看看 AMBA 總線 中的 AXI 4 總線 。

2023-06-21 15:21:44 3091 可以看到,在AXI 到UART中,是通過寄存器 和FIFO進(jìn)行中介的。因為從AXI 總線 往里看,其控制 的是就是地址上所映射的寄存器 。

2023-06-27 10:12:53 7699 本文開源一個FPGA項目:基于AXI 總線 的DDR3讀寫。之前的一篇文章介紹了DDR3簡單用戶接口的讀寫方式:《DDR3讀寫測試》,如果在某些項目中,我們需要把DDR掛載到AXI 總線 上,那就要通過MIG IP核提供的AXI 接口來讀寫DDR。

2023-09-01 16:20:37 7276 電子發(fā)燒友網(wǎng)站提供《STM32F0xx的DMA 控制器 的使用.pdf》資料免費(fèi)下載

2023-09-21 14:49:49 0 由數(shù)據(jù)線、地址線、控制 線等構(gòu)成。 接口是一種連接標(biāo)準(zhǔn),又常常被稱之為物理接口。 協(xié)議是傳輸數(shù)據(jù)的規(guī)則。 1.簡介 AXI 4總線 協(xié)議是 ARM 公司 提出的AMBA( Ad vanced Microcontroller Bus Archi te cture)3.0協(xié)議中最重要的部分,是一種面向高性能、高帶

2023-12-16 15:55:01 1880 Transaction Layer的所有功能特性,不僅內(nèi)置DMA 控制器 ,而且具備AXI 4用戶接口,提供一個高性能,易于使用,可定制化的PCIe-AXI 互連解決方案,同時適用于ASIC和FPGA。

2024-02-21 15:15:03 2110 Transaction layer的所有功能特性,不僅內(nèi)置DMA 控制器 ,而且具備AXI 4用戶接口,提供一個高性能,易于使用,可定制化的PCIe-AXI 互連解決方案,同時適用于ASIC和FPGA。

2024-02-22 09:15:46 3 Scather Gather DMA ,提供FIFO/AXI 4-Stream用戶接口。

基于PCI Express Integrated Block,Multi-Channel PCIe RDMA

2024-02-22 11:11:55 3199 直接存儲器 訪問 ( DMA )控制器 ,可以在內(nèi)存和/或外設(shè)之間傳輸數(shù)據(jù),而不需要 CPU 參與每次傳輸。合理利用 DMA 控制器 ,可以減輕CPU的負(fù)擔(dān)。

2024-03-28 09:41:01 1618 AXI 總線 由一些核心組成,包括AXI 主處理器 接口(AXI 4)、AXI 處理器 到協(xié)處理器 接口(AXI 4-Lite)、AXI 主外設(shè)接口(AXI 4)、AXI 外設(shè)到主處理器 接口(AXI 4-Lite)等。

2024-04-18 11:41:39 2500 CAN總線 控制器 (Controller Area Network Bus Controller)是CAN總線 通信系統(tǒng)中的核心部件,它扮演著接收、處理并轉(zhuǎn)發(fā)CAN總線 數(shù)據(jù)的關(guān)鍵角色。下面將從CAN總線 控制器 的定義、功能、結(jié)構(gòu)、工作原理以及應(yīng)用等方面進(jìn)行詳細(xì)闡述。

2024-09-03 14:16:17 3267 CAN(Controller Area Network,控制器 局域網(wǎng))總線 控制器 的工作原理涉及多個方面,包括消息傳輸、沖突檢測與解決、總線 仲裁等關(guān)鍵機(jī)制。以下是對CAN總線 控制器 工作原理的詳細(xì)解析,旨在全面闡述其工作原理和機(jī)制。

2024-09-30 11:33:12 3095 Xilinx官方也提供有一些DMA 的IP,通過調(diào)用API函數(shù)能夠更加靈活地使用DMA 。 1. AXI DMA 的基本接口 axi dma IP的基本結(jié)構(gòu)如下,主要分為三個部分,分別是控制 axi dma 寄存器

2025-01-06 11:13:54 3774 NVMe需要用AXI 總線 進(jìn)行高速傳輸。而AXI 總線 是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)協(xié)議中的重要組成部分,主要面向高性能、高帶寬、低延時的片內(nèi)互連需求。這里簡要介紹AXI 總線 區(qū)別,以及讀寫架構(gòu)基本原理

2025-05-21 09:29:51 658 已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評論