半導體領域正經歷快速變革,尤其是在人工智能(AI)爆發式增長、對更高處理性能及能效需求持續攀升的背景下。傳統的片上系統(SoC)設計方案在尺寸與成本方面逐漸觸及瓶頸。此時,Multi-Die設計應運而生,將SoC拆分為多個稱為芯粒的芯片,并集成到單一封裝內,成功突破了上述限制。

基于芯粒的設計方案具備多項優勢:在AI與高性能計算(HPC)應用中,通過將計算、存儲與輸入輸出(I/O)功能解耦,助力提升計算能力;在汽車與邊緣AI應用場景下,將大型芯片拆分為尺寸更小、更適配量產的元器件,從而提高生產良率與產品可靠性;借助對封裝內部芯粒組合的靈活重構,能夠快速推出新產品,縮短產品迭代周期。

芯粒設計最佳實踐

對于考慮采用芯粒設計方案的開發者,以下是八項最佳實踐:

從合理的系統分區入手

首先將系統設計拆解為計算、存儲、I/O等功能模塊,并明確哪些功能應作為獨立芯粒存在。針對高性能元器件,選擇先進的工藝節點;而對于性能要求較低的模塊,則選用技術成熟、性價比高的工藝節點。在此過程中,需精心平衡速度、功耗與系統整體效率之間的權衡關系。此外,還應考慮系統的可擴展性,選擇能夠支持未來升級或功能變更的標準與接口。

為每個芯粒選擇合適的工藝節點

并非所有功能皆可從最新技術中獲得同等程度的提升。例如,存儲器的微縮效率通常不及邏輯電路,因此在較成熟的工藝節點上制造存儲器芯粒,既能降低成本,又不會影響性能。在集成芯粒時,需考慮芯粒應采用3D堆疊結構(以實現更低延遲與功耗),還是2.5D并排布局(以簡化實現流程)。

精心規劃Die-to-Die連接

選擇合適的接口對芯粒間實現無縫通信至關重要。UCIe等行業標準在Die-to-Die連接領域的應用正日益廣泛。設計時需確保連接帶寬與系統所需的數據吞吐量相匹配,同時兼顧主數據與邊帶控制數據的傳輸需求。此外,還需精心規劃封裝內芯粒的布局與互連方式來優化物理結構,確保設計符合目標尺寸與形狀要求。根據物理布局的不同,Die-to-Die接口可用的“邊緣區域”(beachfront)面積會有所差異,可能需要采用不同的接口配置。切勿忽視熱管理的重要性,單一封裝內的多個芯粒可能產生熱點,因此必須在設計中融入充足的冷卻與散熱方案。

了解先進的封裝方案

選擇合適的封裝技術是實現設計目標的關鍵。封裝方案涵蓋從傳統有機基板到支持更高密度與性能的先進中介層等多種類型。設計時需綜合考慮外形尺寸與整體成本:先進封裝方案通常具備更強的性能,但實施成本更高、復雜度也更大。要確保開發時間表預留足夠時間用于全面測試與良率管理。每個芯粒都應單獨測試,確保僅選擇“已知合格芯粒”(KGD)進行最終組裝。在Die-to-Die接口中加入冗余與修復功能,有助于提升組裝、測試及量產階段的封裝良率。此外,需密切監控供應鏈,確保所有芯粒組件與封裝材料的采購穩定可靠。

設計時融入安全考量

安全應作為所有基于芯粒的系統的基礎要素。需確保每個芯粒都通過信任根(RoT)進行認證與錨定,以防止未授權訪問,并安全管理密鑰(尤其在多租戶環境中)。通過加密技術與安全通信協議保護芯粒間傳輸的數據。同時,需規劃安全啟動流程,從硬件與軟件兩個層面防范篡改行為。

投入開展系統級設計與驗證

盡早且高頻率地開展系統級仿真與硬件輔助驗證,有助于在硬件制造前發現集成問題,節省寶貴的時間與資源。采用軟硬件協同設計模式,可加速開發進程,縮短產品上市時間。為單個芯粒與最終封裝系統制定完善的測試計劃也至關重要,這是確保可靠性與性能的關鍵。分級測試等新方法可用于評估單個芯粒,并驗證其在Multi-Die設計中組裝后的性能。此外,還需投入資源開展系統級熱建模與串擾分析,以準確評估最終產品中的Multi-Die相互作用。

聚焦控制與管理系統

許多芯粒(尤其在數據中心環境中)可受益于專用的控制與管理系統。這類系統配備CPU,負責管理初始化、低速外設以及RoT等安全功能。通過收集、匯總與分發遙測數據,這類系統還能提升芯片的可靠性、可用性與可服務性(RAS)。

借力生態系統合作伙伴與專業技術

由于芯粒技術與方案仍相對較新且在持續演進,與經驗豐富的伙伴合作至關重要。新思科技等行業領導者不僅提供經過硅驗證的IP解決方案,還提供設計服務與封裝指導。這些IP解決方案正與Arm計算子系統(CSS)集成,以進一步加快芯粒開發速度、降低風險。及時了解最新的芯粒標準也同樣關鍵:通用UCIe聯盟、JEDEC等行業組織會提供關于芯粒技術新進展的重要更新與資源;而imec、ASRA等機構則在為汽車行業制定專門的芯粒提案與指導規范。

釋放基于芯粒設計的優勢

基于芯粒的設計方案為打造下一代高性能系統提供了靈活且可擴展的路徑。設計團隊通過遵循上述最佳實踐,能夠從容應對(芯粒設計的)復雜性,充分發揮基于芯粒方案的優勢。若需在整個芯粒開發周期(從概念構思到產品落地)中獲取專業指導,建議與精通從芯片到系統集成全領域的專家展開合作。

-

半導體

+關注

關注

339文章

31115瀏覽量

265971 -

AI

+關注

關注

91文章

40715瀏覽量

302373 -

新思科技

+關注

關注

5文章

974瀏覽量

52978 -

芯粒

+關注

關注

1文章

88瀏覽量

443

原文標題:Multi-Die設計不踩坑指南:經市場認證的八個關鍵點

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

芯粒設計與異質集成封裝方法介紹

Cadence工具如何解決芯粒設計中的信號完整性挑戰

國芯科技榮獲2025年上市公司董事會辦公室優秀實踐案例

長電科技榮獲2025年上市公司可持續發展最佳實踐案例

思瑞浦獲評“2025年上市公司董事會最佳實踐案例”

UCIe協議代際躍遷驅動開放芯粒生態構建

愛芯元智榮獲2025金輯獎最佳技術實踐應用獎

芯粒技術的專利保護挑戰與應對策略

技術資訊 I 基于芯粒(小晶片)的架構掀起汽車設計革命

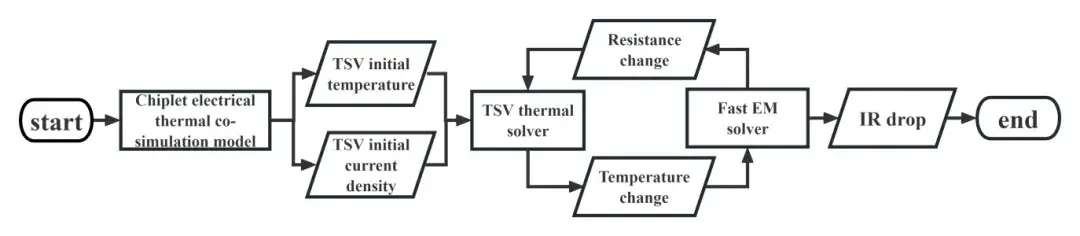

微電子所在芯粒集成電遷移EDA工具研究方向取得重要進展

行芯科技亮相第三屆芯粒開發者大會

奎芯科技登場 COMPUTEX 2025,聚焦芯粒互連解決方案

面向芯粒設計的最佳實踐

面向芯粒設計的最佳實踐

評論