本文翻譯轉(zhuǎn)載于:Cadence Blog

作者:Sigrity

在芯粒設(shè)計(jì)中,維持良好的信號(hào)完整性是最關(guān)鍵的考量因素之一。隨著芯片制造商不斷突破性能與微型化的極限,確保組件間信號(hào)的純凈性與可靠性面臨著前所未有的巨大挑戰(zhàn)。對(duì)于需要應(yīng)對(duì)信號(hào)完整性與電源完整性復(fù)雜問(wèn)題的工程師而言,深入理解這些挑戰(zhàn)的細(xì)微差異,是設(shè)計(jì)出高效、可靠芯粒方案的核心前提。

閱讀全文,可詳細(xì)了解芯粒中的信號(hào)完整性及其在芯片設(shè)計(jì)中的關(guān)鍵作用、芯粒技術(shù)帶來(lái)的獨(dú)特挑戰(zhàn),以及 Cadence 的先進(jìn)工具如何為工程師重新定義設(shè)計(jì)可能性。

理解芯粒中的信號(hào)完整性

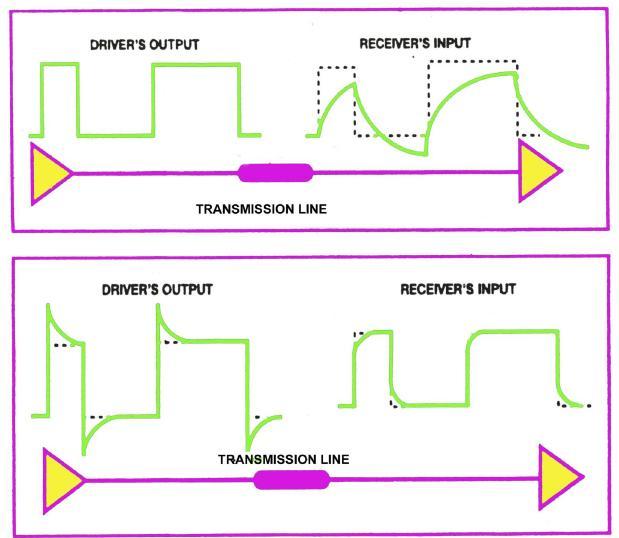

信號(hào)完整性指的是電信號(hào)在系統(tǒng)組件間傳輸時(shí)的質(zhì)量。對(duì)于集成電路封裝設(shè)計(jì)和印刷電路板而言,維持信號(hào)完整性意味著確保信號(hào)不受噪聲、反射、串?dāng)_和損耗的影響而發(fā)生劣化。

芯粒使這一過(guò)程變得更為復(fù)雜。傳統(tǒng)的單芯片將所有組件集成在單一裸片上,而芯粒則是尺寸更小、單獨(dú)制造的組件,通過(guò)互聯(lián)形成集成系統(tǒng)。盡管這種模塊化方案具有顯著的可擴(kuò)展性和靈活性,但也帶來(lái)了新的信號(hào)完整性問(wèn)題。

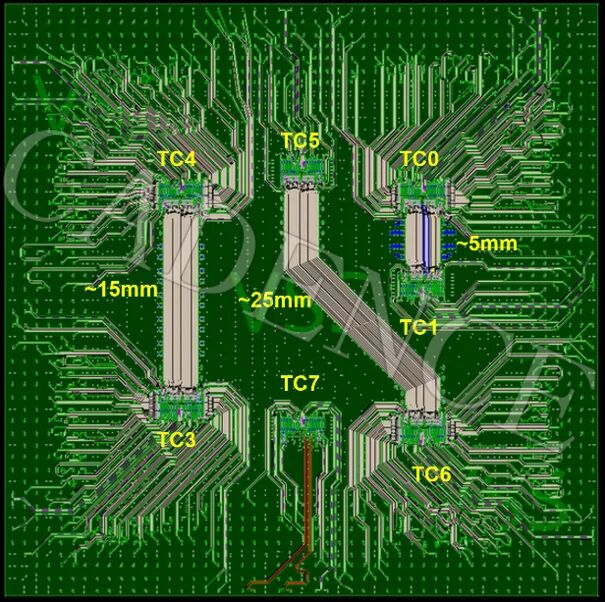

圖 1:包含三條不同長(zhǎng)度芯粒間鏈路的 UCIe 測(cè)試封裝

為什么信號(hào)完整性至關(guān)重要

保持可靠的信號(hào)傳輸是芯片性能的關(guān)鍵要素,因?yàn)榧幢阈盘?hào)質(zhì)量出現(xiàn)微小偏差,都可能影響性能、增加功耗并降低可靠性。確保信號(hào)完整性不僅能保證高性能,還能保障芯片設(shè)計(jì)的可靠性與能效。

芯粒設(shè)計(jì)中的信號(hào)完整性挑戰(zhàn)

熱與電耦合:鑒于芯粒的高度集成特性,組件間的熱電交互成為維持電源完整性和信號(hào)完整性的重要考量因素。

高速數(shù)據(jù)傳輸:現(xiàn)代應(yīng)用(如 AI 工作負(fù)載或高帶寬數(shù)據(jù)中心運(yùn)算)的復(fù)雜性日益提升,對(duì)數(shù)據(jù)傳輸速率提出了更高要求。尤其在高頻場(chǎng)景下,信號(hào)路徑中的損耗與反射問(wèn)題會(huì)更為顯著。

互連密度:為優(yōu)化性能,芯粒間的互連必須高度密集排列,這會(huì)增加串?dāng)_(相鄰線路的信號(hào)干擾)和電磁耦合的風(fēng)險(xiǎn)。

復(fù)雜封裝:芯粒通常需要 2.5D 或 3D 集成等先進(jìn)封裝技術(shù),這類(lèi)封裝方案的設(shè)計(jì)更為緊湊,進(jìn)一步加劇了信號(hào)劣化的風(fēng)險(xiǎn)。

電源傳輸噪聲:芯粒復(fù)雜的電源傳輸網(wǎng)絡(luò)(PDN)可能向系統(tǒng)引入噪聲,影響信號(hào)完整性與電源完整性。確保低阻抗的電源傳輸路徑,是避免干擾的關(guān)鍵。

應(yīng)對(duì)信號(hào)完整性問(wèn)題的解決工具

應(yīng)對(duì)這些挑戰(zhàn)需要借助能夠進(jìn)行全面信號(hào)完整性分析的先進(jìn)技術(shù)與工具。因此,工程師們常選用行業(yè)領(lǐng)先的解決方案,例如 Cadence 的 Sigrity X 和 Clarity 3D Solver 平臺(tái)。

Sigrity X

Cadence 的 Sigrity X 信號(hào)完整性分析技術(shù)采用集成化的強(qiáng)大方案,可應(yīng)對(duì)信號(hào)完整性與電源完整性挑戰(zhàn),其核心功能包括:

端到端的信號(hào)完整性與電源完整性(SI/PI)分析,能在印刷電路板和集成電路封裝設(shè)計(jì)中實(shí)現(xiàn)精細(xì)化、電源感知的信號(hào)完整性及電源傳輸網(wǎng)絡(luò)分析。該功能有助于及早識(shí)別潛在問(wèn)題,確保達(dá)成成本、性能與可靠性目標(biāo)。

先進(jìn)的設(shè)計(jì)內(nèi)互連建模,可模擬信號(hào)路徑并優(yōu)化阻抗,從而減少反射與損耗,對(duì)于芯粒特有的高密度布局設(shè)計(jì)也同樣適用。

串?dāng)_分析功能,通過(guò)評(píng)估和抑制高密度互連中的串?dāng)_,最大限度降低干擾風(fēng)險(xiǎn)。

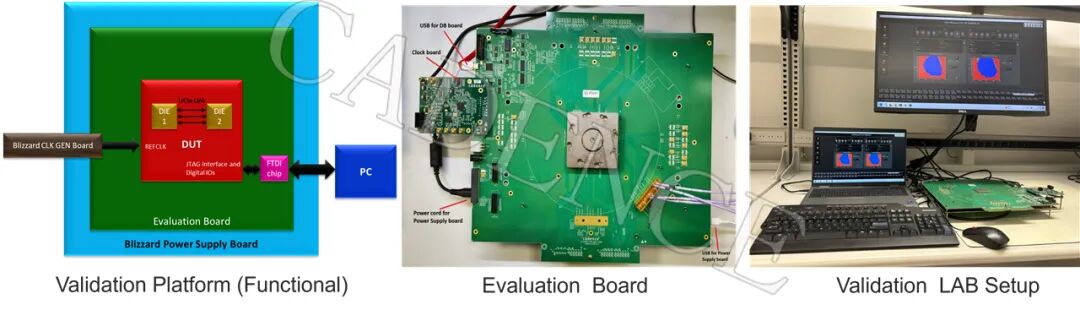

圖 2:Cadence UCIe-Link【IP + 封裝】芯粒間驗(yàn)證平臺(tái),用于關(guān)聯(lián) Sigrity X 信號(hào)完整性仿真結(jié)果

Clarity 3D Solver

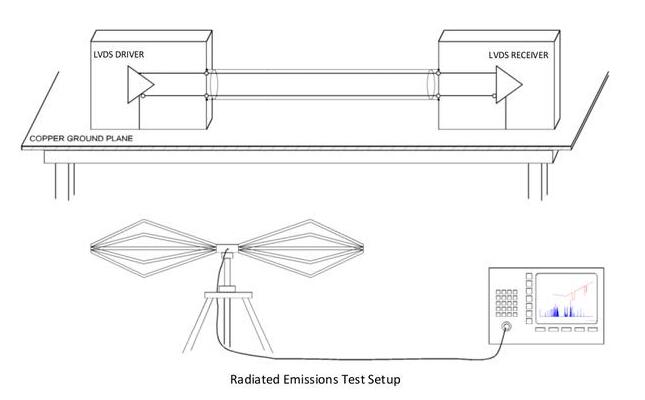

Cadence 的 Clarity 3D Solver 專(zhuān)為高保真度分析設(shè)計(jì),通過(guò)提供針對(duì)硅片、封裝和印刷電路板的 3D 電磁提取能力,與 Sigrity X 的信號(hào)完整性/電源完整性(SI/PI)分析形成互補(bǔ)。其優(yōu)勢(shì)包括:

可分析堆疊封裝或 2.5D/3D 設(shè)計(jì)中的耦合效應(yīng)、熱問(wèn)題及電磁場(chǎng)(EM)行為。

Clarity 3D Solver 與 Cadence 設(shè)計(jì)生態(tài)系統(tǒng)的無(wú)縫集成,使團(tuán)隊(duì)能在統(tǒng)一高效的環(huán)境中協(xié)作。該工具提供宏觀與微觀雙重視角以應(yīng)對(duì)信號(hào)相關(guān)挑戰(zhàn),助力在緊張的進(jìn)度內(nèi)完成高性能設(shè)計(jì)。

增強(qiáng)芯粒信號(hào)完整性強(qiáng)化技巧

除工具外,采用最佳實(shí)踐也能顯著提升信號(hào)完整性的維持能力。以下是可采取的具體措施:

采用電源感知設(shè)計(jì):利用電源感知型信號(hào)完整性分析,考量同步開(kāi)關(guān)噪聲(SSN),確保電源傳輸網(wǎng)絡(luò)的穩(wěn)健性。

優(yōu)化互連阻抗:在整個(gè)信號(hào)路徑中保持受控阻抗,以減少反射并將信號(hào)損耗降至最低。

注重布局與布線技巧:遵循印刷電路板(PCB)布局的最佳實(shí)踐,例如縮短 stub 長(zhǎng)度、合理使用去耦元件、將敏感走線與強(qiáng)干擾信號(hào)分離,從而抑制串?dāng)_并減少噪聲傳播。

盡早且頻繁仿真:在設(shè)計(jì)流程的每個(gè)階段對(duì)潛在的信號(hào)完整性與電源完整性問(wèn)題進(jìn)行仿真,以便及早發(fā)現(xiàn)并解決問(wèn)題。

采用先進(jìn)封裝技術(shù):扇出型晶圓級(jí)封裝(FOWLP)、具有嚴(yán)格控制設(shè)計(jì)參數(shù)的中介層等解決方案,有助于確保電熱穩(wěn)定性。

信號(hào)完整性帶來(lái)的競(jìng)爭(zhēng)優(yōu)勢(shì)

芯粒的信號(hào)完整性不僅是一項(xiàng)技術(shù)挑戰(zhàn),更蘊(yùn)藏著發(fā)展機(jī)遇。通過(guò)主動(dòng)掌控這些復(fù)雜性,你能夠?qū)崿F(xiàn)系統(tǒng)的更高性能、更快上市速度和更強(qiáng)可擴(kuò)展性。 Cadence 的 Sigrity X 與 Clarity 等工具為你提供有力支持,助你從容應(yīng)對(duì)芯粒設(shè)計(jì)的復(fù)雜難題,同時(shí)確保方案的穩(wěn)健性與可靠性。

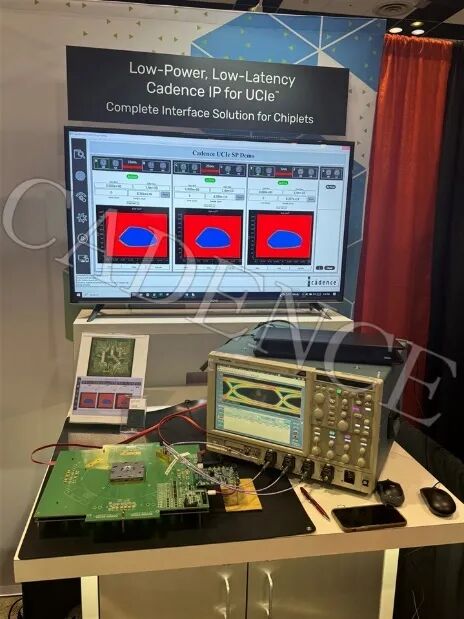

圖 3:Cadence UCIe-Link【IP + 封裝】芯粒間信號(hào)質(zhì)量演示

了解更多關(guān)于信號(hào)完整性的信息

如需深入了解 Cadence 如何幫助工程師解決最復(fù)雜的信號(hào)完整性挑戰(zhàn),可訪問(wèn) Cadence 官網(wǎng)網(wǎng)站瀏覽。Cadence Sigrity X 信號(hào)與電源完整性頁(yè)面請(qǐng)點(diǎn)擊“閱讀原文”進(jìn)行了解。

? 2025 Cadence Design Systems, Inc. 版權(quán)所有。在全球范圍保留所有權(quán)利。Cadence、Cadence 徽標(biāo)和 www.cadence.com/go/trademarks 中列出的其他 Cadence 標(biāo)志均為 Cadence Design Systems, Inc. 的商標(biāo)或注冊(cè)商標(biāo)。

-

Cadence

+關(guān)注

關(guān)注

68文章

1022瀏覽量

147236 -

信號(hào)完整性

+關(guān)注

關(guān)注

68文章

1490瀏覽量

98210 -

芯粒

+關(guān)注

關(guān)注

1文章

88瀏覽量

443

原文標(biāo)題:多物理場(chǎng)系統(tǒng)分析博客 | 理解芯粒設(shè)計(jì)中的信號(hào)完整性

文章出處:【微信號(hào):gh_fca7f1c2678a,微信公眾號(hào):Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

如何解決信號(hào)完整性問(wèn)題

信號(hào)完整性分析與設(shè)計(jì)

關(guān)于信號(hào)完整性的問(wèn)題

何為信號(hào)完整性?信號(hào)完整性包含哪些

信號(hào)完整性原理分析

在高速設(shè)計(jì)中,如何解決信號(hào)的完整性問(wèn)題?

信號(hào)完整性分析

利用Cadence工具進(jìn)行板級(jí)電路信號(hào)完整性仿真

利用Cadence Allegro進(jìn)行PCB級(jí)的信號(hào)完整性仿真

基于Cadence的信號(hào)和電源完整性設(shè)計(jì)與分析

如何在不知情的情況下解決信號(hào)完整性設(shè)計(jì)問(wèn)題

信號(hào)完整性對(duì)EMC的影響有哪些

在高速設(shè)計(jì)中,如何解決信號(hào)的完整性問(wèn)題?

聽(tīng)懂什么是信號(hào)完整性

Cadence工具如何解決芯粒設(shè)計(jì)中的信號(hào)完整性挑戰(zhàn)

Cadence工具如何解決芯粒設(shè)計(jì)中的信號(hào)完整性挑戰(zhàn)

評(píng)論