在芯片技術從 “做大單片” (單片SoC)向 “小芯片組合” (芯粒式設計)轉型的當下,一套統一的互聯標準變得至關重要。UCIe協議便是一套芯粒芯片互聯的 “通用語言”。

2025年8月,UCIe聯盟正式發布UCIe 3.0規范。UCIe 3.0為支持64 GT/s速率的高速芯粒互聯標準,是一年前推出的UCIe 2.0規范所提供32 GT/s帶寬的兩倍。

UCIe 3.0的發布標志著芯粒互聯技術向更高性能和更成熟的生態演進。其不僅解決了不同廠商芯粒的兼容問題,還在帶寬、能效、系統管理性和可靠性上實現重要突破。在AI、HPC及汽車電子這些算力與互聯要求極高的領域,UCIe 3.0帶來了更高效的異構集成解決方案,并將產生深遠影響。

芯粒的性能優勢與生態需求

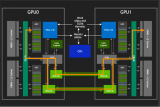

在先進半導體架構領域,采用多芯粒(Multi-Die)異構集成方案以構建大規模計算系統,正成為提升系統經濟性與擴展性的重要技術路徑。該模式通過將復雜功能分解為多個模塊化芯粒,并在芯片封裝層級進行高密度互聯與集成,已在多個主流商業產品中得到廣泛應用,包括消費級CPU、服務器CPU及GPGPU等。

(圖:2021~2030年,芯粒式設計處理器核心的復合年增長率CAGR高達44%)

推動芯粒封裝集成的核心動因涵蓋性能、良率與復用等多重維度。

提升良率&成本控制

巨型單體芯片的良率隨面積增大而指數下降,成本急劇攀升。芯粒式設計通過將尺寸較大的硅片進行切割為多個小芯粒,單個芯粒的良率更高,并可以根據芯粒的功能采用匹配的制程,整體成本得以控制。

突破光罩限制

為滿足日益提升的計算性能需求,單芯片尺寸持續擴大,部分設計已接近甚至超出光罩尺寸極限(例如集成數百核心的多核CPU或高端口數交換網絡芯片)。芯粒提供了一種突破光罩尺寸對算力限制的途徑:將多個大尺寸硅片合封在一起,提供遠超單一硅片能實現的單芯片算力。

跨產品的芯粒復用

芯粒架構支持功能單元的跨市場與跨產品復用,相同的基礎功能芯粒(如IO單元、內存控制器等)可經不同組合集成,跨適配從邊緣計算到超算中心的多樣化應用場景,這種復用和組合靈活性帶來的成本分攤充分體現芯粒設計的價值。

最后,多個相同Die的集成封裝能夠適用于大規模的應用場景,可有效實現算力的線性擴展,同時保持優異的功耗與信號完整性表現。

(圖:芯粒設計在領先工藝節點上較大型SoC可降低30%+總擁有成本。來源:Alphawave Semi)

如今,芯粒供應商的生態系統不斷擴大,客戶希望能根據架構、供應鏈、經濟性等多種因素,靈活混合搭配不同供應商的產品。這種需求使得芯粒之間快速、可靠且安全的通信變得前所未有的重要。

UCIe協議正是為解決這一問題而生:它定義了裸片到裸片連接的通用接口,實現了跨供應商解決方案和工藝節點的互操作性。

UCIe協議及其演替歷程

UCIe協議的建立及核心作用

UCIe(Universal Chiplet Interconnect Express)標準是芯粒異構集成領域的核心互聯規范,其核心作用在于定義了跨工藝節點、跨供應商的裸片間(Die-to-Die)通用互聯接口,實現了封裝級異構集成的標準化與互操作。

該標準由英特爾、AMD、臺積電、高通、谷歌、微軟、Meta等行業內頭部企業共同推動,旨在構建開放、多供應商的芯粒生態系統,推動形成規模化、可復用的芯粒市場。自2022年聯盟成立以來,UCIe聯盟成員已從初始的120余家全球企業擴展至140余家,涵蓋芯片設計、制造、封裝、系統集成及云服務等全產業鏈環節。

作為國內最早一批加入UCIe聯盟的成員之一,奇異摩爾深度參與到芯粒生態系統的建設與發展中。奇異摩爾AI網絡全棧式解決方案均基于芯粒架構,整合片內-片間-網間互聯三大維度進行產品布局,旨在打造通用開源的芯粒互聯互通系統。

關鍵演進(UCIe 1.0/1.1/2.0/3.0)

(圖:UCIe 1.0 →1.1→ 2.0 → 3.0 演進)

UCIe各代協議的演進過程顯示出芯粒技術正在從“可用”走向“高效與規模化應用”的階段。

1首次確立芯粒通用互聯協議

UCIe 1.0,2022年

涵蓋了物理層、協議棧、軟件模型和一致性測試,支持PCIe、CXL等多協議以確保互操作性,實現了跨工藝、跨廠商芯粒在封裝級互聯的標準化。

2為流式傳輸提供可靠性

UCIe 1.1,2023年

引入針對流式傳輸協議的“Flit模式”,為流式傳輸協議提供鏈路級可靠性保障(如AMBA CHI能夠利用UCIe D2D適配器內建的CRC和重傳邏輯)。顯著簡化了非原生協議的集成復雜度,增強了UCIe的通用性。

3支持3D異構集成

UCIe 2.0,2024年

擴展支持3D堆疊異構集成,提供垂直互聯標準化方案,顯著提升互聯密度并降低功耗。同時將單通道速率提升至32 GT/s,并增強電源管理及安全功能,推動技術走向規模化產業落地。

4

支持更高速率

UCIe 3.0,2025年

在2D/2.5D異構集成中支持64 GT/s高速率,引入運行時動態鏈路重校準與擴展邊帶管理機制,優化大規模多芯粒系統在功耗、信號完整性及熱管理方面的系統級可部署性。該版本在顯著提升帶寬密度的同時,兼顧能效與兼容性,還著重解決了大規模芯粒系統在實際部署中的關鍵問題,推動了芯粒生態從單純追求連接速度向構建高效、可靠且易于集成的方向發展。

(圖:UCIe 3.0性能指標)

(圖:UCIe的層級化協議和多種封裝類型)

(圖:UCIe支持的不同形式:封裝級集成或是使用不同媒介的非封裝的連接(例如光、毫米波、電纜))

UCIe協議的應用

芯粒技術的發展正重塑AI硬件生態。與傳統單片SoC相比,模塊化設計可將系統分解為計算、IO、存儲等專用單元,通過UCIe等協議實現異構集成。該模式使芯片良率提升30%-50%,開發周期縮短40%,同時通過工藝組合優化降低系統功耗25%-50%。

(圖:通過UCIe連接的芯片封裝示意圖)

UCIe具有明顯的優勢,包括可擴展性、互操作性和靈活性。UCIe的典型應用有CPU-GPU互聯、內存與計算芯片接口。此外,UCIe也推動了光電共封CPO的發展。相較于運用私有Die2Die協議實現光引擎(OE)和計算Die/Switch芯片共封,遵循開放Die2Die協議UCIe進行互聯,成本更低的同時靈活度更高,可以靈活實現標準封裝或先進封裝下的CPO。

基于UCIe協議的xPU-CPO案例

Ayar Labs于2025年3月宣布推出符合UCIe規范的光互連芯粒TeraPHY。這一物理層芯片采用該公司16波長SuperNova光源,可提供8Tbps帶寬,集成UCIe電氣接口以實現同其它制造商芯粒的兼容與互操作性。這便于客戶向定制SoC集成光學IO,加速了數據中心互聯從電到光的過渡,讓物理上分隔的xPU可“無縫”通信。

(圖:Ayar Labs TeraPHY光學IO芯片)

Lightmatter公司在2025 Hot Chips大會上發布Passage M1000超大光學中介層平臺。該設計結合了UCIe IP和激光通信技術,通過在中介層直接集成光學IO,滿足垂直堆疊的芯片復合體對互聯帶寬的需求。相比電氣互連,光學鏈路具有帶寬密度高、損耗低和跨距更長的優勢。這使得M1000能夠提供114Tbps的總帶寬(每方向57Tbps),并成為未來邁向200Tbps級xPU與400Tbps級交換機的第一步。

(圖:Lightmatter光學互連平臺Passage M1000)

總結以上,UCIe構建了以開放生態為核心的技術體系,為聯盟內廠商提供了平滑的升級路徑與豐富的IP復用基礎。在算力渴求無止境的AI時代,UCIe以開放生態打破互連壁壘,成為芯粒集成的“通用語言”。

UCIe協議與CPO的深度融合,正重塑計算邊界——通過封裝內高速互聯與芯片級光IO的協同,將硅光引擎直接“對話”計算芯粒,實現了從電到光的范式躍遷。這種架構級創新,不僅突破了帶寬瓶頸與功耗高墻,更以模塊化設計開啟了“樂高式”系統集成,為下一代智算中心構建了可擴展、高效率的算力基座。

(圖:D2D接口標準對比分析,UCIe協議具備開放性、可擴展性、互操作性和靈活性優勢)

奇異摩爾作為UCIe開放生態的深度參與者,憑借其在AI互聯與芯粒集成領域的技術積累,具備顯著的發展潛力。公司產品線中,除Kiwi UCIe D2D IP、Kiwi Central IO Die外,Kiwi G2G IO Die亦為基于UCIe協議設計產品,具備UCIe更高性能、更具靈活性和可靠性的優勢。

下周ICCAD 2025大會上,奇異摩爾將展示面向AI超節點的創新互聯硬件方案——Scale Up超節點互聯芯粒Demo。

該方案為基于奇異摩爾G2G IO芯粒的GPU/xPU互聯系統,具體通過UCIeD2D協議實現G2G IO芯粒與GPU/xPU計算芯粒互聯。產品實現通過UCIe接口與多層網絡協議棧硬件化,結合Scale Up網絡交換機及CBFC、PFC、LLR流控機制,為大模型訓練等場景提供高帶寬、低延遲的超節點互聯能力,是芯粒架構在AI算力集群規模化應用的關鍵驗證載體。

(圖:奇異摩爾Scale Up超節點互聯芯粒Demo)

UCIe 3.0 規范的發布為半導體行業帶來了新的發展機遇和變革動力。未來,隨著UCIe在AI加速器、超節點、數據中心及智能駕駛領域規模化落地,奇異摩爾有望通過契合標準演進的高靈活性產品,為客戶提供具備確定性能優勢的互聯方案,推動開放芯粒生態走向成熟,成為下一代算力基礎設施的關鍵貢獻者。

關于我們

AI網絡全棧式互聯架構產品及解決方案提供商

奇異摩爾,成立于2021年初,是一家行業領先的AI網絡全棧式互聯產品及解決方案提供商。公司依托于先進的高性能RDMA 和Chiplet技術,創新性地構建了統一互聯架構——Kiwi Fabric,專為超大規模AI計算平臺量身打造,以滿足其對高性能互聯的嚴苛需求。我們的產品線豐富而全面,涵蓋了面向不同層次互聯需求的關鍵產品,如面向北向Scale-out網絡的AI原生超級網卡、面向南向Scale-up網絡的GPU片間互聯芯粒、以及面向芯片內算力擴展的2.5D/3D IO Die和UCIe Die2Die IP等。這些產品共同構成了全鏈路互聯解決方案,為AI計算提供了堅實的支撐。

-

半導體

+關注

關注

339文章

31062瀏覽量

265711 -

封裝

+關注

關注

128文章

9302瀏覽量

148928 -

UCIe

+關注

關注

0文章

53瀏覽量

2025 -

芯粒

+關注

關注

1文章

87瀏覽量

442

原文標題:后摩爾時代的高性能算力基石:UCIe代際躍遷驅動開放芯粒生態構建

文章出處:【微信號:奇異摩爾,微信公眾號:奇異摩爾】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

芯粒設計與異質集成封裝方法介紹

聲智科技亮相2026瑞芯微AI軟件生態大會

開放協作,共筑生態——思爾芯參與上海開放處理器產業創新中心開業儀式暨RISC-V專利聯盟專利池入池儀式

萬物共芯,生生不息:此芯科技2025生態大會共創開放智能未來

新思科技助力UCIe 3.0快速落地

為什么說uCentral是構建開放網絡的開源利器?

Arm加速構建汽車開放芯粒生態

喜訊|昊芯RISC-V DSP榮獲“中國芯”RISC-V生態推廣獎

電商API接口開放平臺的生態構建與運營策略

面向芯粒設計的最佳實踐

借助Arm芯粒技術構建計算未來

奇異摩爾助力OISA全向智感互聯IO芯粒技術白皮書發布

UCIe協議代際躍遷驅動開放芯粒生態構建

UCIe協議代際躍遷驅動開放芯粒生態構建

評論