在今日舉行的2025開放數(shù)據(jù)中心委員會(ODCC)峰會期間,中國移動主導(dǎo)的《OISA全向智感互聯(lián)IO芯粒技術(shù)白皮書》正式發(fā)布,并榮獲2025 ODCC 年度卓越成果獎。作為AI網(wǎng)絡(luò)全棧式互聯(lián)解決方案提供商,奇異摩爾憑借其在芯粒領(lǐng)域的深厚技術(shù)積累與產(chǎn)業(yè)實踐,多方位貢獻(xiàn)于該白皮書的撰寫與關(guān)鍵技術(shù)路徑的梳理工作。

自O(shè)ISA 1.0技術(shù)體系提出,再到OISA 2.0協(xié)議的發(fā)布,奇異摩爾持續(xù)跟進(jìn)并深度參與其技術(shù)體系的演進(jìn)與迭代,在GPU互聯(lián)領(lǐng)域多個關(guān)鍵方向貢獻(xiàn)前瞻性建議。公司專注于以芯粒為基礎(chǔ)的高性能互聯(lián)全棧解決方案,推動開放、標(biāo)準(zhǔn)化互聯(lián)生態(tài)的構(gòu)建。

此外,公司還作為主編單位,深度參與了中國移動牽頭編制的《人工智能加速器互聯(lián)芯粒技術(shù)要求》標(biāo)準(zhǔn)制定工作,為構(gòu)建自主可控的超節(jié)點互聯(lián)體系提供了關(guān)鍵技術(shù)支持。

半導(dǎo)體行業(yè)正處于一個根本性轉(zhuǎn)折點,傳統(tǒng)的SoC正戰(zhàn)略性地轉(zhuǎn)向芯粒式設(shè)計。這一轉(zhuǎn)型遵循從微觀到宏觀的技術(shù)演進(jìn)路徑,本文也由微觀至宏觀進(jìn)行展開梳理,對《OISA全向智感互聯(lián)IO芯粒技術(shù)白皮書》中的關(guān)鍵內(nèi)容,沿著芯粒級、芯片級到系統(tǒng)級,最后囊括生態(tài)級的全棧技術(shù)路徑進(jìn)行解讀。

一、 芯粒級:戰(zhàn)略轉(zhuǎn)型與核心益處

數(shù)十年來,摩爾定律通過驅(qū)動性能、功耗、面積和成本(PPAC)的同步優(yōu)化,成為半導(dǎo)體行業(yè)技術(shù)進(jìn)步與經(jīng)濟模型的核心支柱。

然而,在先進(jìn)工藝節(jié)點(7nm及以下),摩爾定律正面臨雙重挑戰(zhàn):一方面,非經(jīng)常性工程(NRE)成本呈指數(shù)增長,大幅提高了芯片開發(fā)的門檻和風(fēng)險;另一方面,物理限制如光刻掩模版尺寸極限(“光刻墻”)阻礙了單芯片面積的持續(xù)擴展。在經(jīng)濟可行性與物理規(guī)律的雙重約束下,行業(yè)正被迫從傳統(tǒng)單片系統(tǒng)級芯片(SoC)轉(zhuǎn)向新的架構(gòu)范式——以芯粒為基礎(chǔ)的分解式系統(tǒng)設(shè)計,以延續(xù)算力增長。

在芯粒的設(shè)計理念下,形成了兩種主要的集成策略,分別為同構(gòu)集成和異構(gòu)集成。其中異構(gòu)集成將不同工藝節(jié)點、功能甚至可能來自不同制造商的芯粒進(jìn)行優(yōu)化并組合集成于同一封裝,可視為“超越摩爾定律”(More than Moore)的真正體現(xiàn)。

芯粒范式最強大的地方在于它賦予了系統(tǒng)架構(gòu)師對PPAC四個維度進(jìn)行“解耦”和獨立優(yōu)化的能力,從而帶來了多方面的戰(zhàn)略優(yōu)勢:

1良率提升與成本控制

2異構(gòu)集成帶來的成本優(yōu)化

3加速產(chǎn)品上市時間

這種戰(zhàn)略上的靈活性,使得芯粒架構(gòu)成為應(yīng)對后摩爾時代挑戰(zhàn)、延續(xù)半導(dǎo)體行業(yè)創(chuàng)新活力的核心驅(qū)動力。

二、芯片級:IO芯粒演變?yōu)橄到y(tǒng)樞紐

從行業(yè)應(yīng)用來看,領(lǐng)先AI芯片廠商產(chǎn)品中已融入了計算Die與IO Die解耦設(shè)計和性能提升的思路:華為昇騰Ascend 910芯片采用了Side IO Die設(shè)計、英偉達(dá)下一代AI GPU產(chǎn)品Rubin將導(dǎo)入多制程節(jié)點芯粒設(shè)計。

IO芯粒作為芯粒設(shè)計理念中最具影響力的實踐之一,是將IO功能從核心計算單元中分離出來,形成一個獨立的專用芯片。通過芯粒技術(shù)實現(xiàn)IO功能與計算功能的分離,可為系統(tǒng)設(shè)計和商業(yè)模式帶來多方面的決定性優(yōu)勢:

1解耦開發(fā)生命周期,加速核心創(chuàng)新

2芯粒可復(fù)用顯著降低成本

3可配置的互聯(lián)帶寬與產(chǎn)品線擴展

在此背景下,IO芯粒已從昔日簡單的物理接口(PHY)裸片,演變成一個高度復(fù)雜的復(fù)雜多芯粒系統(tǒng)的集成與管理中心。

根據(jù)《人工智能加速器互聯(lián)芯粒技術(shù)要求》等規(guī)范性文件的定義,一個典型的IO芯粒包含清晰的層次化架構(gòu)和多個核心功能模塊:

分層架構(gòu):IO芯粒的內(nèi)部邏輯遵循標(biāo)準(zhǔn)的網(wǎng)絡(luò)三層模型(協(xié)議層、數(shù)據(jù)鏈路層、物理層),確保了功能的模塊化和清晰的職責(zé)劃分,這與全向智感互聯(lián)(OISA)協(xié)議棧的結(jié)構(gòu)相呼應(yīng)。

核心功能模塊:IO芯粒內(nèi)部集成了接口管理與協(xié)議轉(zhuǎn)換模塊、數(shù)據(jù)傳輸與緩存模塊、電源管理模塊、安全與加密模塊,以能夠分別實現(xiàn)不同協(xié)議之間的轉(zhuǎn)換處理、數(shù)據(jù)在芯粒內(nèi)外的流動管理、精細(xì)化的功耗控制策略、數(shù)據(jù)的完整性和隱私保護(hù),以保證實現(xiàn)芯粒級復(fù)雜的功能。

此外,IO芯粒提供一套標(biāo)準(zhǔn)化的核心接口(例如:緩存一致性與I/O一致性內(nèi)存流量接口、地址轉(zhuǎn)換服務(wù)接口、中斷處理與系統(tǒng)控制接口)確保與計算芯粒的無縫集成和整個系統(tǒng)的穩(wěn)定運行,這也使其成為一個名副其實的“系統(tǒng)網(wǎng)絡(luò)集線器”。

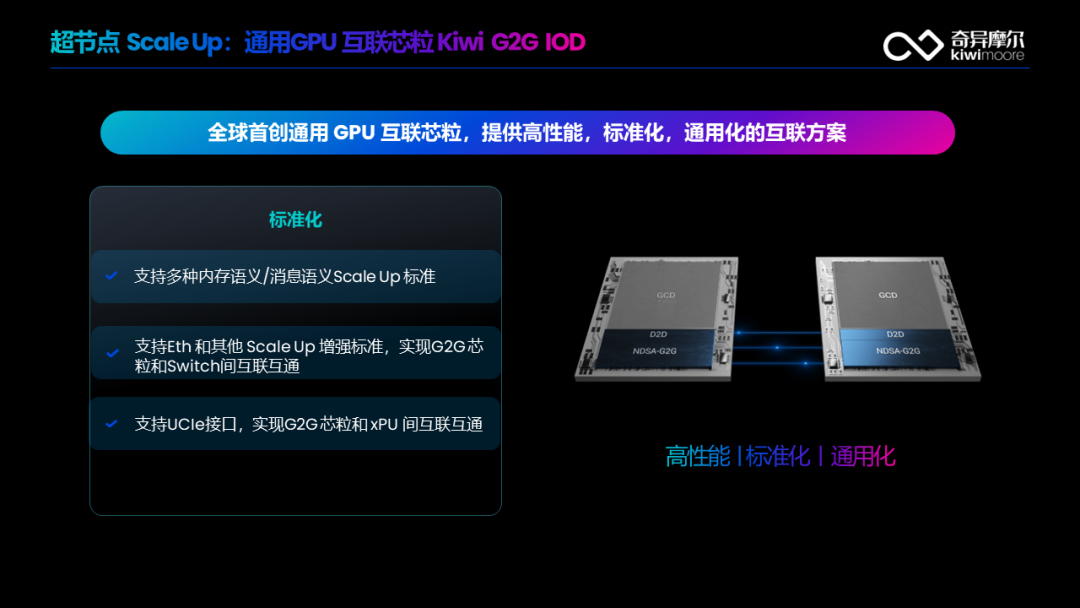

從行業(yè)應(yīng)用角度,奇異摩爾的超節(jié)點互聯(lián)芯粒 Kiwi G2G IOD是行業(yè)內(nèi)目前唯一一種基于芯粒架構(gòu)和開放生態(tài)方案。Kiwi G2G IOD支持高帶寬、集成多種復(fù)雜協(xié)議,并且有多語義支持,具備UCIe接口,兼顧高性能和客戶靈活性,可滿足不同廠商不同場景的需求,在百花齊放的Scale-Up生態(tài)系統(tǒng)中支持多協(xié)議類型及其升級方案,從而降低持續(xù)研發(fā)難度和開發(fā)成本。

三、互聯(lián)網(wǎng)絡(luò):協(xié)議與物理層

芯粒集成技術(shù)是實現(xiàn)高性能、高能效異構(gòu)計算架構(gòu)的關(guān)鍵路徑,而其核心基礎(chǔ)在于芯粒之間的“通用語言”——高性能互聯(lián)協(xié)議。

在D2D通信領(lǐng)域,存在核心架構(gòu)選擇,從根本上決定了芯粒間交互的效率、靈活性和應(yīng)用場景。目前互聯(lián)協(xié)議的演進(jìn)呈現(xiàn)出兩種路徑分化:

1協(xié)議無關(guān)的流式傳輸(Agnostic Streaming)

以UCIe為代表的“通用適配器”——致力于通過協(xié)議無關(guān)的流式傳輸,能兼容如PCIe、CXL等多種協(xié)議,適合異構(gòu)集成,可構(gòu)建一個最廣泛、最開放的互操作生態(tài)系統(tǒng);

2原生內(nèi)存語義(Native Memory Semantics)

以O(shè)ISA、NVLink等為代表的“領(lǐng)域?qū)S镁W(wǎng)絡(luò)”——通過原生內(nèi)存語義和網(wǎng)絡(luò)內(nèi)計算等深度優(yōu)化,適合需要高效通信的場景,為AI/HPC等特定工作負(fù)載提供極致性能。

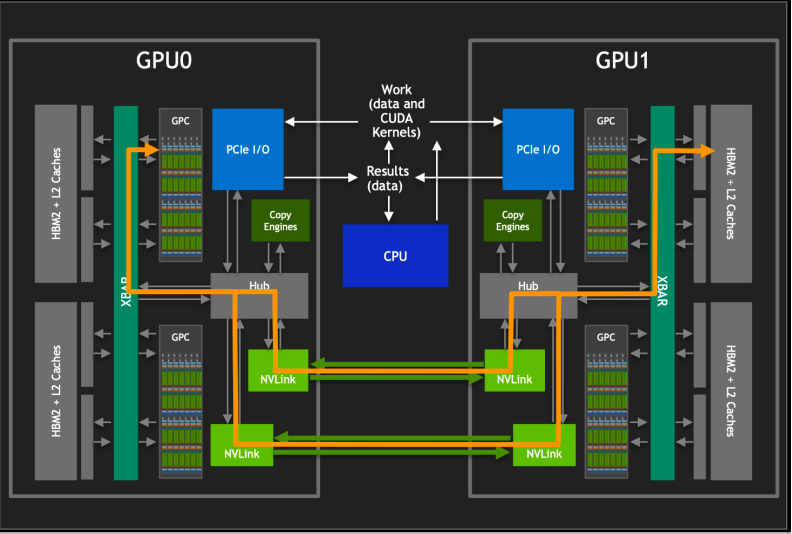

(圖:英偉達(dá)NVLink)

兩種路線的選擇取決于具體的應(yīng)用場景,不存在絕對的優(yōu)劣。

然而,構(gòu)建世界上最強大的AI超級計算機需要一個與處理單元(GPU)和主要工作負(fù)載(分布式訓(xùn)練)深度協(xié)同設(shè)計的互連網(wǎng)絡(luò)。為結(jié)合蓬勃發(fā)展的需求、提升AI訓(xùn)練和推理的性能,定義和采用關(guān)于AI超級計算機“超級節(jié)點”這一應(yīng)用場景最適合的互聯(lián)協(xié)議也成為了迫在眉睫的業(yè)內(nèi)難題。

四、系統(tǒng)級:集成與協(xié)同

支撐萬億參數(shù)模型訓(xùn)推的關(guān)鍵基礎(chǔ)設(shè)施正在轉(zhuǎn)向新的架構(gòu)范式“超級節(jié)點”(Super Node)

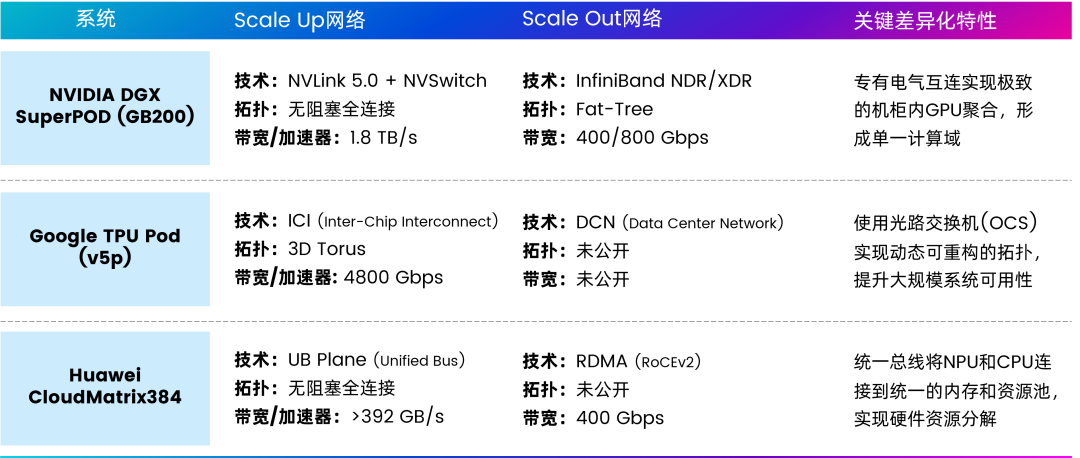

定義“超級節(jié)點”:這不再是傳統(tǒng)意義上的單個服務(wù)器,而是一個邏輯上的、緊密耦合的計算單元。它由數(shù)十個乃至數(shù)百個加速器(GPU/NPU)組成,這些加速器在一個機柜或少數(shù)幾個機柜內(nèi),通過一個超高帶寬、超低延遲的“Scale Up”網(wǎng)絡(luò)緊密地連接在一起,形成一個巨大的、統(tǒng)一的計算和內(nèi)存資源池。這與傳統(tǒng)集群僅依賴“Scale Out”網(wǎng)絡(luò)進(jìn)行節(jié)點間通信的模式形成了鮮明對比。超級節(jié)點的設(shè)計目標(biāo)是,讓內(nèi)部的所有加速器能夠像一個單一的巨型加速器一樣協(xié)同工作。

(圖:AI超級節(jié)點互聯(lián)架構(gòu)對比)

Scale Up的意義已經(jīng)不再局限于機柜內(nèi)通信;支持MoE專家并行及張量并行的工作負(fù)載不僅依賴極低延遲的專有“Scale Up”網(wǎng)絡(luò),用于節(jié)點內(nèi)部的緊密耦合通信;同時也依賴一個更標(biāo)準(zhǔn)化的、高性能的“Scale Out”網(wǎng)絡(luò),用于節(jié)點間的通信需要。

“

然而,IO芯粒正是坐落在這個關(guān)鍵的交匯點上。它必須同時包含連接其同級計算裸片的專有Scale-Up網(wǎng)絡(luò)的PHY和協(xié)議邏輯,以及連接外部世界的、基于標(biāo)準(zhǔn)的Scale-Out網(wǎng)絡(luò)的PHY和協(xié)議邏輯。因此,IO芯粒成為了連接兩個不同網(wǎng)絡(luò)世界的橋梁和翻譯官。

另一個層面,為滿足分布式訓(xùn)練中梯度同步和參數(shù)交換對延遲和帶寬的極端要求,原生支持內(nèi)存語義(Native Memory Semantics)的互聯(lián)協(xié)議已成為必然選擇。加上NVIDIA NVLink為私有化垂直解決方案,種種因素共同催生了像OISA這樣專業(yè)的、開放的、基于內(nèi)存語義的互聯(lián)技術(shù)。這些專用互聯(lián)技術(shù)集成了集合通信加速計算(OISA中的CCA,類似NVLink中的SHARP)等功能,對大規(guī)模互聯(lián)的性能至關(guān)重要。

(圖源:奇異摩爾)

中國移動OISA體系的推出,正是為了在中國構(gòu)建這樣一個自主、可控且高性能的AI硬件生態(tài)系統(tǒng)。

OISA協(xié)議具備兩大特點:①集合通信加速(CCA)為核心創(chuàng)新,通過OISA交換芯片內(nèi)嵌計算單元實現(xiàn)網(wǎng)絡(luò)內(nèi)計算,大幅降低All-Reduce操作延遲和GPU負(fù)載;②智能感知技術(shù)(Intelligent Sensing)為先進(jìn)帶內(nèi)互聯(lián)隨路感知技術(shù),實現(xiàn)動態(tài)路由選擇和流量優(yōu)化,保障確定性性能。

OISA不僅是一個技術(shù)規(guī)范,更是一個產(chǎn)業(yè)聯(lián)盟,旨在通過開放協(xié)作,協(xié)同產(chǎn)業(yè)鏈上下游,共同攻克技術(shù)難題,打造具有競爭力的智算基礎(chǔ)設(shè)施。隨著光電IO等下一代技術(shù)的成熟,OISA及其所代表的芯粒互連技術(shù)將繼續(xù)演進(jìn),成為未來計算架構(gòu)中不可或缺的核心基石。

在OISA GPU技術(shù)標(biāo)準(zhǔn)化的過程中,奇異摩爾作為OISA的重要聯(lián)盟成員持續(xù)推進(jìn)OISA芯粒技術(shù)的協(xié)同與適配。盡管如此,通往一個完全開放、即插即用的芯粒市場的道路依然充滿挑戰(zhàn)。這仍需各環(huán)節(jié)緊密協(xié)作,從技術(shù)標(biāo)準(zhǔn)化、生態(tài)協(xié)作與產(chǎn)業(yè)鏈垂直整合三個維度共同突破,使得芯粒技術(shù)真正釋放其潛力,賦能下一代AI超算與異構(gòu)計算架構(gòu)的持續(xù)演進(jìn)。

關(guān)于我們

AI網(wǎng)絡(luò)全棧式互聯(lián)架構(gòu)產(chǎn)品及解決方案提供商

奇異摩爾,成立于2021年初,是一家行業(yè)領(lǐng)先的AI網(wǎng)絡(luò)全棧式互聯(lián)產(chǎn)品及解決方案提供商。公司依托于先進(jìn)的高性能RDMA 和Chiplet技術(shù),創(chuàng)新性地構(gòu)建了統(tǒng)一互聯(lián)架構(gòu)——Kiwi Fabric,專為超大規(guī)模AI計算平臺量身打造,以滿足其對高性能互聯(lián)的嚴(yán)苛需求。我們的產(chǎn)品線豐富而全面,涵蓋了面向不同層次互聯(lián)需求的關(guān)鍵產(chǎn)品,如面向北向Scale-out網(wǎng)絡(luò)的AI原生超級網(wǎng)卡、面向南向Scale-up網(wǎng)絡(luò)的GPU片間互聯(lián)芯粒、以及面向芯片內(nèi)算力擴展的2.5D/3D IO Die和UCIe Die2Die IP等。這些產(chǎn)品共同構(gòu)成了全鏈路互聯(lián)解決方案,為AI計算提供了堅實的支撐。

-

數(shù)據(jù)中心

+關(guān)注

關(guān)注

18文章

5647瀏覽量

75009 -

人工智能

+關(guān)注

關(guān)注

1817文章

50094瀏覽量

265281 -

奇異摩爾

+關(guān)注

關(guān)注

0文章

79瀏覽量

4037

原文標(biāo)題:生態(tài)共建 | 奇異摩爾核心貢獻(xiàn):《OISA全向智感互聯(lián)IO芯粒技術(shù)白皮書》正式發(fā)布

文章出處:【微信號:奇異摩爾,微信公眾號:奇異摩爾】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

華為在MWC 2026聯(lián)合發(fā)布高品質(zhì)萬兆AI園區(qū)建網(wǎng)技術(shù)白皮書

多合一空氣質(zhì)量傳感器對比白皮書

中興通訊重磅發(fā)布超節(jié)點技術(shù)白皮書

奇異摩爾參編人工智能加速器互聯(lián)芯粒技術(shù)要求團體標(biāo)準(zhǔn)發(fā)布

中興通訊聯(lián)合發(fā)布供應(yīng)鏈智能技術(shù)應(yīng)用白皮書

華為聯(lián)合發(fā)布園區(qū)自智網(wǎng)絡(luò)技術(shù)白皮書

奇異摩爾攜手中國移動發(fā)布OISA 2.0協(xié)議

華為聯(lián)合發(fā)布Wi-Fi 7 Advanced技術(shù)白皮書

華為發(fā)布高品質(zhì)萬兆AI園區(qū)建網(wǎng)技術(shù)白皮書

“端云+多模態(tài)”新范式:《移遠(yuǎn)通信AI大模型技術(shù)方案白皮書》正式發(fā)布

華大半導(dǎo)體牽頭發(fā)布汽車安全芯片應(yīng)用領(lǐng)域白皮書

東進(jìn)技術(shù)發(fā)布《后量子密碼技術(shù)白皮書(2025版)》

高通發(fā)布ADAS技術(shù)白皮書,助力中國車企普及先進(jìn)駕駛輔助系統(tǒng)

奇異摩爾助力OISA全向智感互聯(lián)IO芯粒技術(shù)白皮書發(fā)布

奇異摩爾助力OISA全向智感互聯(lián)IO芯粒技術(shù)白皮書發(fā)布

評論