本文由TechSugar編譯自SemiWiki

在半導(dǎo)體行業(yè)中,許多產(chǎn)品由獨立制造和分銷的組件組裝而成,這一特點為商業(yè)專利保護(hù)帶來了特殊考量。而芯粒(Chiplet)的出現(xiàn),則打破了這種傳統(tǒng)模式,它所涉及的專利保護(hù)問題多樣且復(fù)雜。

芯粒技術(shù):后摩爾時代的創(chuàng)新突破

系統(tǒng)級芯片(System-on-a-Chip,簡稱SoC)作為集成電路領(lǐng)域的核心產(chǎn)品,能夠在單一封裝內(nèi)實現(xiàn)完整計算機功能,憑借低功耗、高性能的特性,成為智能手機、高端筆記本電腦、物聯(lián)網(wǎng)設(shè)備等產(chǎn)品的“核心大腦”。

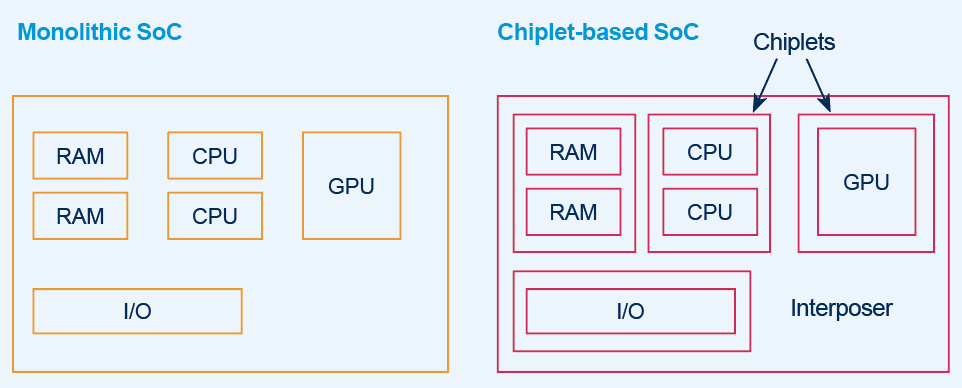

傳統(tǒng)SoC將中央處理器(CPU)、存儲器、輸入/輸出電路等核心功能模塊集成在單一半導(dǎo)體材料(如硅片)上,以完整芯片形式完成制造和分銷。

隨著中央處理器(CPU)、圖形處理器(GPU)、現(xiàn)場可編程門陣列(FPGA)等高性能運算(HPC)芯片性能的持續(xù)提升,以及人工智能(AI)、車聯(lián)網(wǎng)、5G等應(yīng)用相繼興起,各類應(yīng)用場景對高帶寬、高算力、低延時、低功耗的需求愈發(fā)強烈。在此背景下,“后摩爾時代”下的異構(gòu)集成芯片技術(shù)——Chiplet(芯粒)應(yīng)運而生。

芯粒技術(shù)的核心思想是“先分后合”,即將傳統(tǒng)單芯片的功能模塊拆分為獨立制造的微芯片(即芯粒),再通過先進(jìn)封裝技術(shù)將這些芯粒集成封裝,最終形成具備系統(tǒng)級功能的芯片產(chǎn)品。每個芯粒都是承擔(dān)特定功能的基礎(chǔ)模塊,通過模塊化組合實現(xiàn)傳統(tǒng) SoC 的完整功能。

與傳統(tǒng)單芯片系統(tǒng)級芯片(SoC)相比,基于芯粒的系統(tǒng)級芯片(SoC)具有多方面優(yōu)勢,包括:通過對單個芯粒進(jìn)行測試可提高生產(chǎn)良率;芯粒可采用不同制造工藝制作,因此設(shè)計靈活性更高;以及通過組裝現(xiàn)成的芯粒,可簡化系統(tǒng)級芯片(SoC)的設(shè)計流程。

圖1:傳統(tǒng)單芯片系統(tǒng)級芯片(SoC)與基于芯粒的系統(tǒng)級芯片(SoC)

圖1:傳統(tǒng)單芯片系統(tǒng)級芯片(SoC)與基于芯粒的系統(tǒng)級芯片(SoC)

相關(guān)法律規(guī)定

芯粒技術(shù)的普及在推動芯片產(chǎn)業(yè)創(chuàng)新的同時,也帶來了知識產(chǎn)權(quán)保護(hù)的新難題。目前,針對這一新興領(lǐng)域的法律法規(guī)體系尚未完全成熟,專利保護(hù)面臨諸多挑戰(zhàn)。

對于傳統(tǒng)單芯片 SoC 這類整體式設(shè)備,專利侵權(quán)判定邏輯相對清晰:任何人制造、進(jìn)口或銷售包含專利保護(hù)發(fā)明的完整芯片,即構(gòu)成專利侵權(quán)。由于傳統(tǒng)芯片采用一次性整體制造模式,其內(nèi)部功能模塊的劃分不影響侵權(quán)判定——只要芯片整體包含專利權(quán)利要求的全部技術(shù)特征,即從制造環(huán)節(jié)構(gòu)成侵權(quán)。

然而,芯粒技術(shù)的出現(xiàn)打破了這一傳統(tǒng)格局。由于單個芯粒可能涉及多個技術(shù)領(lǐng)域和廠商,知識產(chǎn)權(quán)歸屬呈現(xiàn)碎片化特征,管理難度顯著增加。實踐中,申請人在為SoC相關(guān)發(fā)明(如架構(gòu)改進(jìn)、功能實現(xiàn)技術(shù)等)申請專利時,仍習(xí)慣以傳統(tǒng)單芯片SoC為基礎(chǔ),將權(quán)利要求限定為完整芯片的特征,這種做法極易導(dǎo)致后續(xù)維權(quán)困境。

具體而言,若某專利權(quán)利要求針對的是在基于芯粒的系統(tǒng)級芯片(SoC)中所實現(xiàn)的發(fā)明,其技術(shù)特征可能分散在不同芯粒中,這意味著單個芯粒無法單獨包含該發(fā)明的全部特征。因此,單個芯粒的制造商(或進(jìn)口商、銷售商)可能不構(gòu)成直接侵權(quán)。只有當(dāng)這些芯粒最終組裝成系統(tǒng)級芯片(SoC)時,才可能構(gòu)成專利直接侵權(quán)。而這會導(dǎo)致供應(yīng)鏈中的大部分環(huán)節(jié)處于未受保護(hù)狀態(tài),進(jìn)而削弱專利的商業(yè)價值。

盡管間接侵權(quán)制度可能提供補充保護(hù)路徑——即單個芯粒雖未包含全部專利特征,仍可能被認(rèn)定為對SoC專利的間接侵權(quán),但實踐中證明間接侵權(quán)的難度極大。尤其是在芯粒制造商與下游組裝方分屬不同法域的跨境交易場景中,管轄權(quán)沖突、舉證責(zé)任分配等問題進(jìn)一步加劇了維權(quán)難度。

芯粒時代的專利布局建議

針對芯粒技術(shù)的特點,廠商在專利布局階段需調(diào)整策略,確保專利權(quán)利要求能夠覆蓋“模塊化制造、分布式分銷”的產(chǎn)品形態(tài),實現(xiàn)對直接侵權(quán)行為的有效規(guī)制。在計算機芯片領(lǐng)域,這意味著專利權(quán)利要求應(yīng)盡可能精準(zhǔn)覆蓋單個芯粒,而非局限于完整SoC。

通常情況下,一項發(fā)明的核心創(chuàng)新點往往體現(xiàn)在某一特定子組件(如特定功能芯粒)的技術(shù)特征上。通過精細(xì)化篩選權(quán)利要求的技術(shù)特征,可將保護(hù)范圍聚焦于該核心子組件——使單獨制造、銷售該子組件的行為即構(gòu)成直接侵權(quán)。對于僅為發(fā)明提供技術(shù)背景、對核心創(chuàng)新無實質(zhì)影響的要素,只需在權(quán)利要求中間接提及,無需列為侵權(quán)判定的必要條件。

需要強調(diào)的是,隨著技術(shù)迭代,“整體式產(chǎn)品”的定義正不斷演變,芯粒技術(shù)已深刻改變了SoC的制造范式。因此,建議相關(guān)企業(yè)咨詢熟悉芯片技術(shù)領(lǐng)域的專業(yè)專利代理人,結(jié)合技術(shù)特點與法律實踐,制定適配芯粒時代的專利保護(hù)方案,確保創(chuàng)新成果獲得充分保護(hù)。

-

集成電路

+關(guān)注

關(guān)注

5452文章

12571瀏覽量

374523 -

半導(dǎo)體

+關(guān)注

關(guān)注

339文章

30725瀏覽量

264045 -

chiplet

+關(guān)注

關(guān)注

6文章

495瀏覽量

13601 -

芯粒

+關(guān)注

關(guān)注

1文章

85瀏覽量

424

發(fā)布評論請先 登錄

Cadence工具如何解決芯粒設(shè)計中的信號完整性挑戰(zhàn)

汽車電磁兼容性 法規(guī)07系列(UN/ECE R10)新增內(nèi)容明細(xì)與應(yīng)對策略分析

UCIe協(xié)議代際躍遷驅(qū)動開放芯粒生態(tài)構(gòu)建

電壓暫降發(fā)生后,有哪些應(yīng)對策略?

借助Arm芯粒技術(shù)構(gòu)建計算未來

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導(dǎo)體芯片產(chǎn)業(yè)的前沿技術(shù)

技術(shù)資訊 I 基于芯粒(小晶片)的架構(gòu)掀起汽車設(shè)計革命

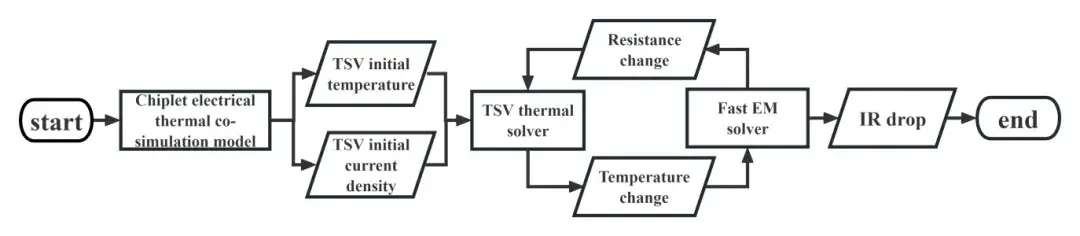

微電子所在芯粒集成電遷移EDA工具研究方向取得重要進(jìn)展

電源噪聲的來源與應(yīng)對策略

行芯科技亮相第三屆芯粒開發(fā)者大會

淺談辰達(dá)MOSFET在USB PD快充電源中的應(yīng)用挑戰(zhàn)與應(yīng)對

晶振偏頻解析:影響因素、檢測方法及應(yīng)對策略

為什么電容屏?xí)?“誤認(rèn)” 水滴為觸控?聚徽解析濕度干擾的底層邏輯與應(yīng)對策略

普通整流橋失效模式大解析:短路、過熱與浪涌沖擊應(yīng)對策略

芯粒技術(shù)的專利保護(hù)挑戰(zhàn)與應(yīng)對策略

芯粒技術(shù)的專利保護(hù)挑戰(zhàn)與應(yīng)對策略

評論