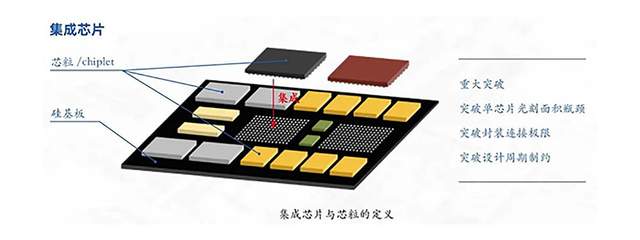

Chiplet會將SoC分解成微小的芯片,各公司已開始產生新的想法、工具和“Chiplet平臺”,旨在將這些Chiplet橫向或縱向組裝成先進的SiP(system-in- package)形式。令人不解的是,Chiplet最初的構想是將SoC分解成類似樂高積木的模塊,而現在似乎又重新回到了集成競賽中。

總部位于加州圣何塞的DreamBig Semiconductor就是其中一家初創公司。該公司參加了上月的CES,并發布了名為MARS的“開放式Chiplet平臺”。

MARS平臺的核心是一個“Chiplet Hub”,該公司將其命名為Deimos Chiplet Hub(DCH)。

工程高級副總裁Steve Majors解釋說,DCH是一個芯片die。它作為一個中樞,將包括CPU、主AI加速器、內存控制器、I/O和高速網絡在內的一系列Chiplet連接成一個完整的SiP設備。

這家初創公司的最大理念是讓客戶專注于他們可以實現差異化的定制化芯片領域。DreamBig的DCH將幫助他們快速構建多種類型的定制SiP設備。

DreamBig與其他Chiplet組裝公司的差異化戰略是搭乘Silicon Box的順風車,后者是由Marvell的前聯合創始人Sehat Sutardja和他的妻子Weili Dai創辦的新加坡Chiplet代工廠。

DCH內部

DCH集成了包括CPU在內的多種功能,并支持將DMA、中斷控制器、PCIe交換機和HBM堆棧等功能集成到Chiplet的die中。

不過,Majors解釋說,DCH內部的CPU是“管理CPU,而不是主CPU,后者位于附加的Chiplet上”。

但是,像DMA和中斷控制器這樣的功能不是已經存在于大多數CPU的die上了嗎?

Majors解釋說:“一旦將CPU分解成Chiplet,就需要對CPU Chiplet的內核和高速緩存進行優化,使其能夠持續擴展到下一個工藝節點或添加特殊指令。”他補充說,DMA和中斷控制器等功能最好在靠近內存和IO的地方分區,由Chiplet Hub提供給所有CPU Chiplet。

內存優先架構

Majors認為DreamBig的關鍵是其Chiplet Hub采用的“內存優先架構”。它使所有Chiplet都能直接訪問高速緩存/內存層,包括堆疊在Chiplet Hub上的低延遲SRAM/3D HBM和Chiplet上的大容量DDR/CXL/SSD。這使得計算、加速器和網絡Chiplet能夠執行高效的數據移動、數據緩存或數據處理。

此外,正如Majors所說,DreamBig還提供了存儲分層的靈活性。它可以從SRAM到HBM再到CXL再到SSD,“從而提供Mega Bytes到Giga Bytes以及Tera Bytes的內存,用于緩存或數據訪問”。

Majors解釋說,總之,一個平臺可以在使用的層級和為每個層級選擇的大小方面“跨范圍”組合。“因此,3D HBM是可選的。Chiplet Hub可進行3D堆疊,但不一定要堆疊。”

拉鋸戰

行業Chiplet專家們也指出,Chiplet供應商可能會重新開始集成競賽,而不是讓Chiplet實現SoC的分解。

盡可能多地集成將符合Chiplet供應商的利益,這樣才能提高利潤率并獲得更好的性能。那么,Chiplet供應商是否會為了誰能集成什么而展開拉鋸戰?系統設計者是否真的能獲得這一概念所承諾的模塊化?

Chiplet仍處于初級階段

Intel的Chiplet專家Ron Wilson指出,盡管形成了一定程度的互聯標準,但Chiplet的潮流還面臨著一些重要的、有爭議的問題。

Wilson問道:系統將如何分區?CPU和GPU等大型模塊是必然的。但這些大塊需要各種輔助功能的支持,如內存控制器、高速緩存和高速緩存控制器、DMA和中斷控制器、總線控制器以及相當于片上網絡硬件的 SiP。傳統上,所有這些東西都由CPU IP供應商提供,并與CPU內核集成在一起。但是,它們應該放在CPU的die上,還是單獨的die上?或者,就像DreamBig似乎建議的那樣,把它們集成到一個單獨的模塊上,然后在整個系統中共享?

至于互聯性,DreamBig試圖覆蓋很多領域。例如,據該公司稱,其DCH平臺提供32到128個D2D(die-to-die)鏈路,每個鏈路64GB/s,用于連接Chiplet。每個鏈路都支持主要的行業標準D2D物理層/鏈路層:通用芯片互連Express(UCIe)流協議和開放計算項目(OCP)BoW(Bunch of Wires)。

基板會如何?

另一組問題涉及芯片下面的基板。顯而易見的選擇是標準封裝基板,Wilson說,“但它在線寬、凸點密度和性能方面存在問題”。

芯片Interposer可以解決所有這些問題,但它們的尺寸有限,而且非常昂貴。使用扇出封裝技術的互連層是另一種可能性,介于普通封裝基板和interposer技術之間。Wilson補充說:“供應鏈中已經有了這方面的基礎設施。”還有玻璃,有些人認為它是未來的基板,能夠像扇出技術一樣在巨大的面板上制造。但它仍未得到證實。

DreamBig的秘密武器似乎是Silicon Box的面板級封裝技術。如圖所示,Silicon Box使用的是600mm的方形面板,而不是傳統的300mm圓形晶片。

Silicon Box聲稱它使用的是“革命性的”RDL(redistribution layer),可以取代昂貴的芯片Interposer。正如Majors解釋的那樣,在Silicon Box工作的一些工程主管是各種扇出封裝方法的發明者。遺憾的是,Silicon Box沒有透露他們使用的RDL的任何細節。

開啟夢想

DreamBig目前在全球擁有200多名員工。據Majors稱,該公司迄今已融資7,000多萬美元。

公司CEO兼創始人是Sohail Syed。在此之前,他曾將自己的公司Questarium賣給了Marvell,當時Sutardja和Dai掌管著這家公司。

值得注意的是,Syed是網絡技術方面的專家,擁有專門的網絡IP。

當他意識到與計算機相比,網絡行業缺乏先進技術時,他便萌生了創辦DreamBig的想法。Sutardja和Dai一致認為,Syed的想法可以與整個Chiplet的愿景相輔相成。

除了開放式Chiplet平臺,DreamBig還提供了兩個“先進的硬件網絡加速器IP”實例。它們是RDMA(remote direct memory access)和算法TCAM(ternary content-addressable memory)。TCAM是一種高速存儲器,可以在一個時鐘周期內搜索其全部內容。

DreamBig的Majors解釋說,RDMA有利于云網絡的使用,如遠程存儲或HPC集群。RDMA還可用于AI擴展,連接大量AI計算/加速器集群。他總結道:“RDMA將所有這些網絡流量從處理器上卸載下來,從而提高了系統的效率和可擴展性。

同時,算法TCAM對于大型虛擬化云網絡中的Match Action處理非常有用,例如微軟SONiC DASH。

Majors強調說:“到目前為止,這些技術只有Nvidia、Intel、AWS等巨頭才有。他聲稱,DreamBig現在首次以IP或芯片的形式向公開市場提供該技術。

審核編輯:劉清

-

交換機

+關注

關注

23文章

2904瀏覽量

104468 -

SoC芯片

+關注

關注

2文章

669瀏覽量

37163 -

PCIe

+關注

關注

16文章

1461瀏覽量

88419 -

中斷控制器

+關注

關注

0文章

63瀏覽量

9819 -

chiplet

+關注

關注

6文章

495瀏覽量

13603

原文標題:Chiplet也走上了集成競賽的道路?

文章出處:【微信號:Astroys,微信公眾號:Astroys】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Chiplet,如何助力HPC?

擁抱Chiplet,大芯片的必經之路

多Chiplet異構集成的先進互連技術

躍昉科技受邀出席第四屆HiPi Chiplet論壇

東莞理工學院“小眼睛科技杯”第四屆集成電路設計與創新應用競賽圓滿落幕

Chiplet與異構集成的先進基板技術

Chiplet封裝設計中的信號與電源完整性挑戰

解構Chiplet,區分炒作與現實

華大九天推出芯粒(Chiplet)與2.5D/3D先進封裝版圖設計解決方案Empyrean Storm

Chiplet與先進封裝設計中EDA工具面臨的挑戰

Chiplet:芯片良率與可靠性的新保障!

Chiplet是否也走上了集成競賽的道路?

Chiplet是否也走上了集成競賽的道路?

評論