以下文章來源于逍遙設計自動化,作者逍遙科技

01現代半導體封裝演進基礎

半導體產業正處在傳統封裝邊界逐步消解的轉型節點,新的集成范式正在涌現。理解從分立元件到復雜異構集成的發展過程,需要審視半導體、封裝和載板基板之間的基本關系在過去十五年中的變化。

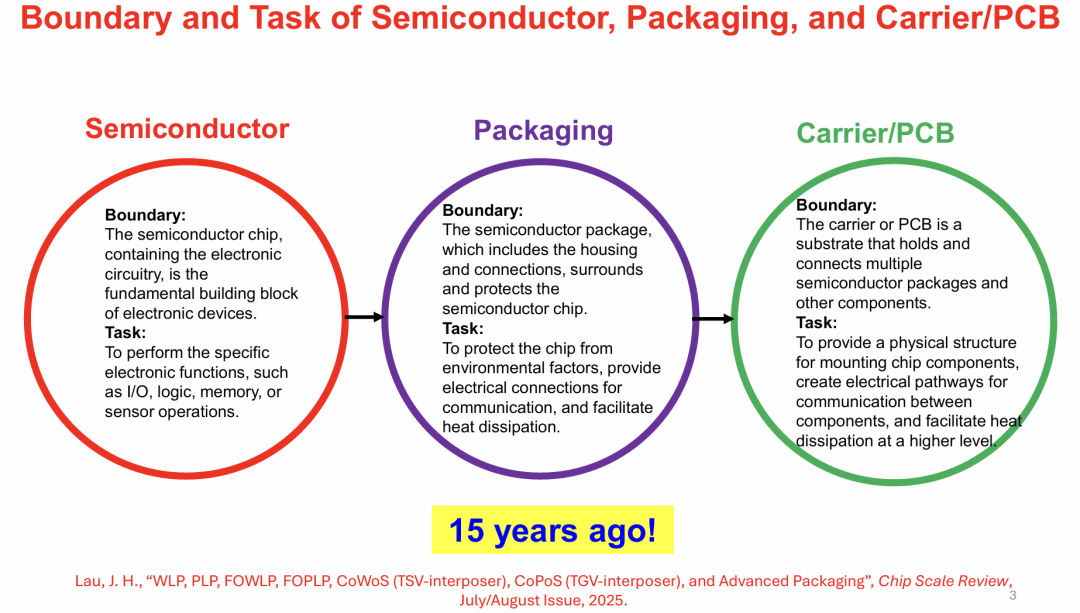

傳統上,半導體產業在明確界定的邊界內運作,每個組件都承擔不同的功能。半導體芯片包含電子線路,執行輸入/輸出操作、邏輯處理、存儲或傳感器操作等特定功能。封裝層,包括外殼和連接器,圍繞并保護芯片,同時提供電氣連接和散熱功能。載板基板或印刷線路板為元件安裝提供物理結構,并在元件之間建立電氣通路。

圖1:十五年前半導體、封裝和載板層之間的傳統功能分離,顯示各層的明確邊界和不同職責

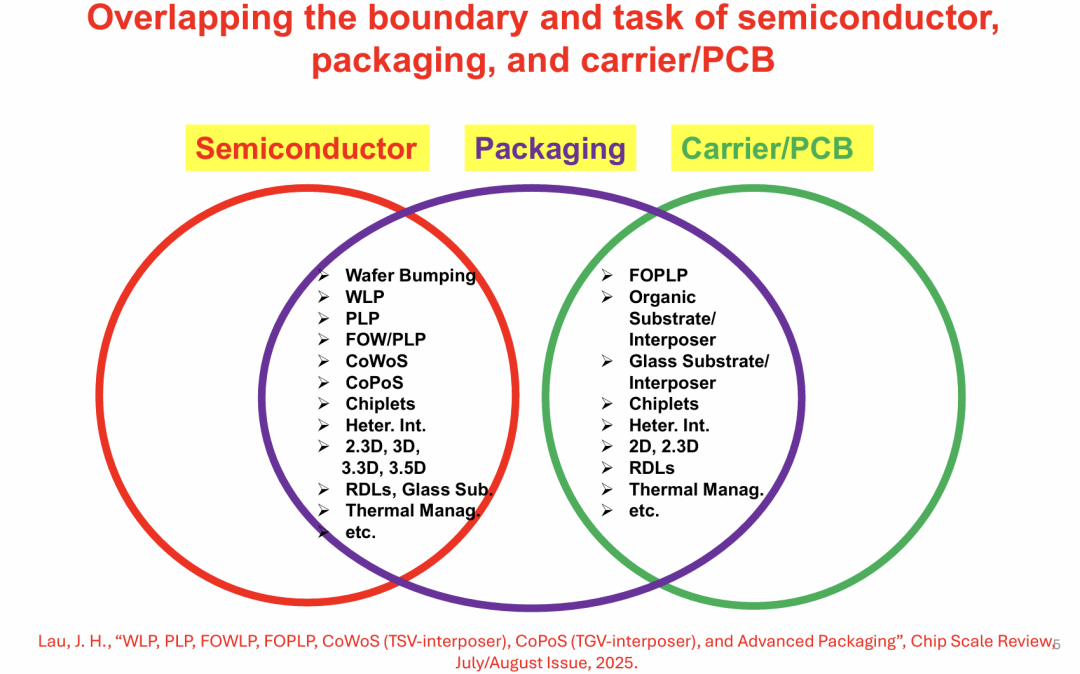

然而,隨著產業不斷推進先進封裝技術的極限,這種清晰的界限已經變得越來越模糊。如今,這些傳統邊界出現顯著重疊,封裝技術融合了晶圓凸點、晶圓級封裝、面板級封裝、扇出晶圓/面板級封裝、芯片-晶圓-基板集成、Chiplet以及包括2.3D、3D、3.3D和3.5D配置在內的各種異構集成形式。

圖2:現代先進封裝如何在傳統獨立域之間創造顯著重疊,展示WLP、PLP、FOWLP、FOPLP、CoWoS、CoPoS和Chiplet等技術跨越多個傳統邊界

02Chiplet概念及其影響

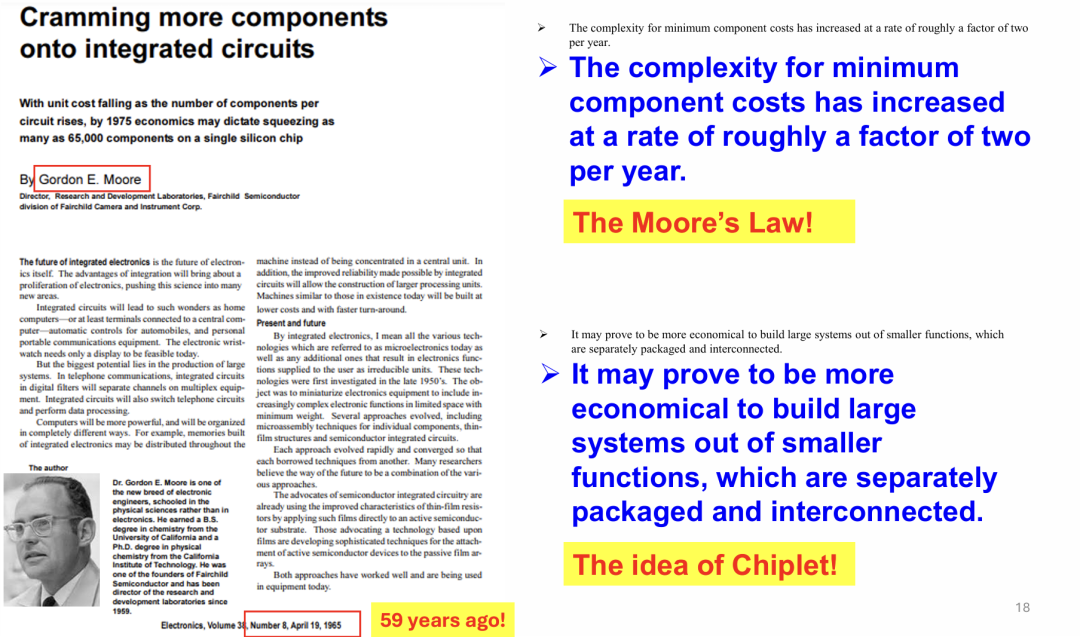

Chiplet概念代表著自集成電路發明以來半導體設計方法學的重大范式轉變。值得注意的是,Chiplet的基本思想早在近六十年前就由戈登·摩爾提出,他觀察到,由較小的、分別封裝并互連的功能模塊構建大型系統可能更加經濟。這一深刻洞察,結合他關于元件復雜度每兩年翻倍的著名觀察,為我們現在所認知的摩爾定律和Chiplet革新奠定了基礎。

圖3:戈登·摩爾在1965年關于從更小的、分別封裝的功能模塊構建系統的原始見解,證明Chiplet概念比其現代實現早了近六十年

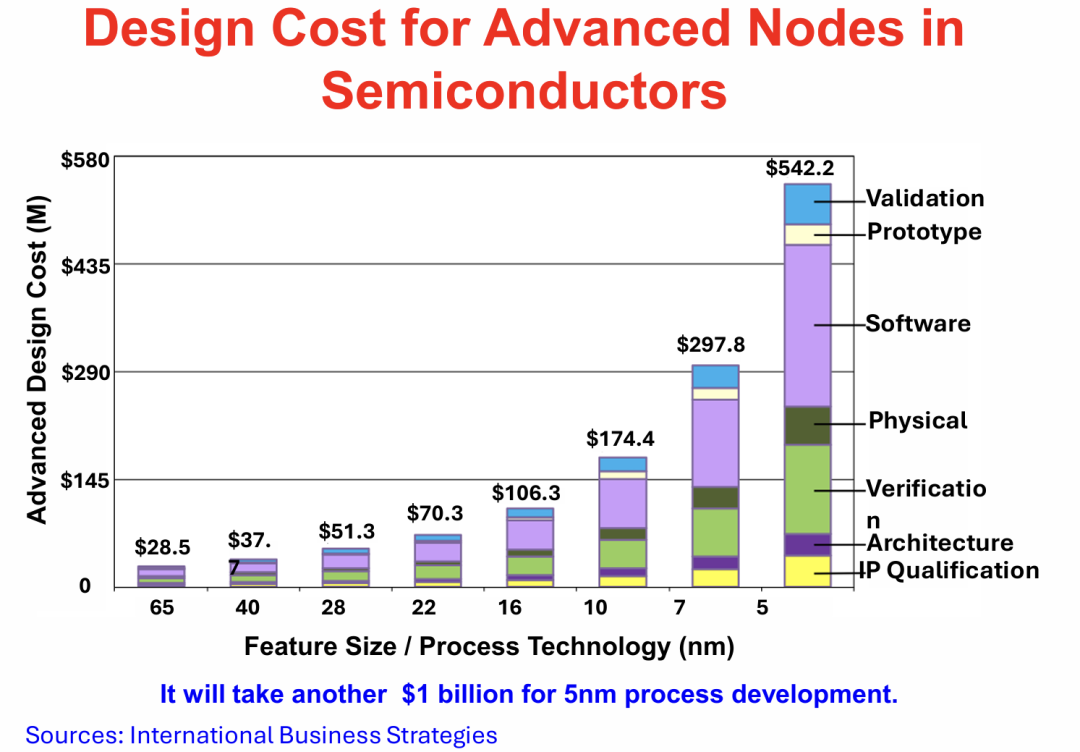

區分Chiplet和異構集成對理解現代半導體架構是關鍵的。Chiplet代表一種芯片設計方法學,涉及將大型單片系統級芯片設計劃分為更小、更易管理的組件。每個Chiplet都可以針對其特定功能進行優化,使用最適合的工藝技術制造,并可能來自不同的代工廠。這種方法解決了半導體產業面臨的幾個關鍵挑戰,特別是隨著特征尺寸繼續縮小和制造成本指數級上升。

圖4:隨著半導體工藝節點的發展,設計成本的急劇增加,顯示成本從65nm的2850萬美元上升到5nm的超過5.4億美元,使Chiplet方法從經濟角度越來越有吸引力

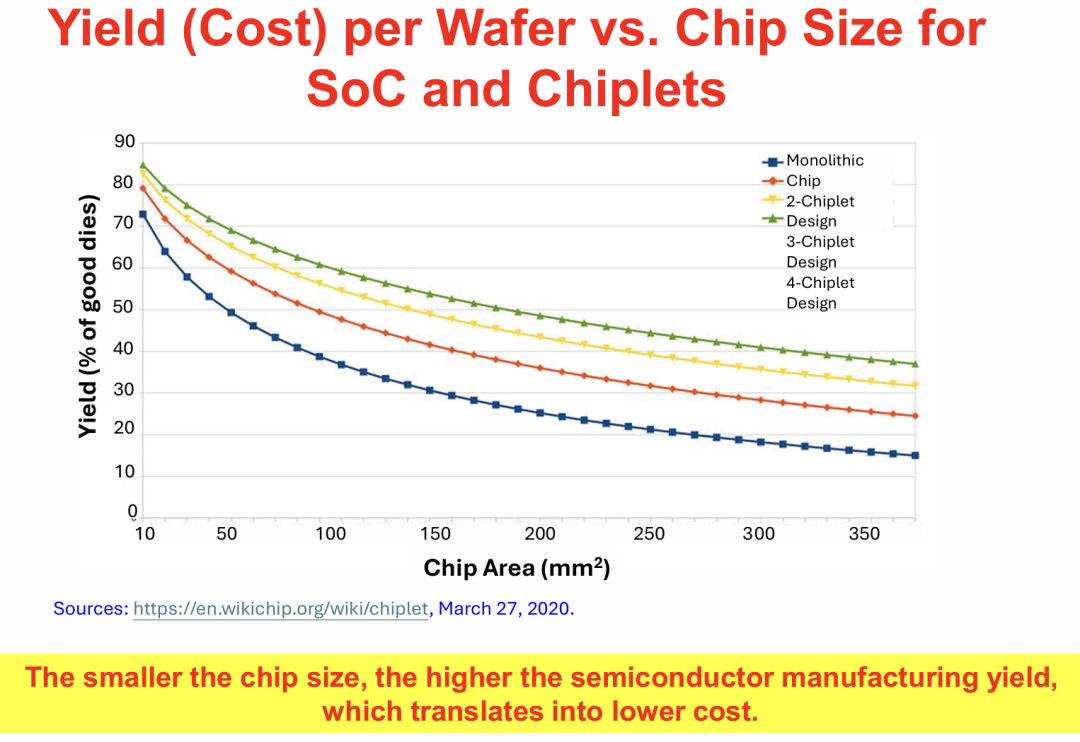

Chiplet采用的經濟驅動因素在檢查不同芯片尺寸的良率特征時變得明顯。較大的單片芯片制造良率較低,因為整個芯片區域內的任何缺陷都會使整個器件無法使用。通過將功能劃分為更小的Chiplet,制造商可以為每個單獨元件實現更高的良率,從而獲得更好的整體成本效率。

圖5:隨著芯片面積增加,單片設計的良率急劇下降,而基于Chiplet的方法通過使用更小的單獨元件保持更高的良率

03集成方法的演進

半導體封裝產業已經發展出復雜的分類法來描述不同層次的集成復雜度。這些范圍從傳統的2D集成方法到日益復雜的3D配置,每種都提供不同的優勢并解決特定的應用需求。

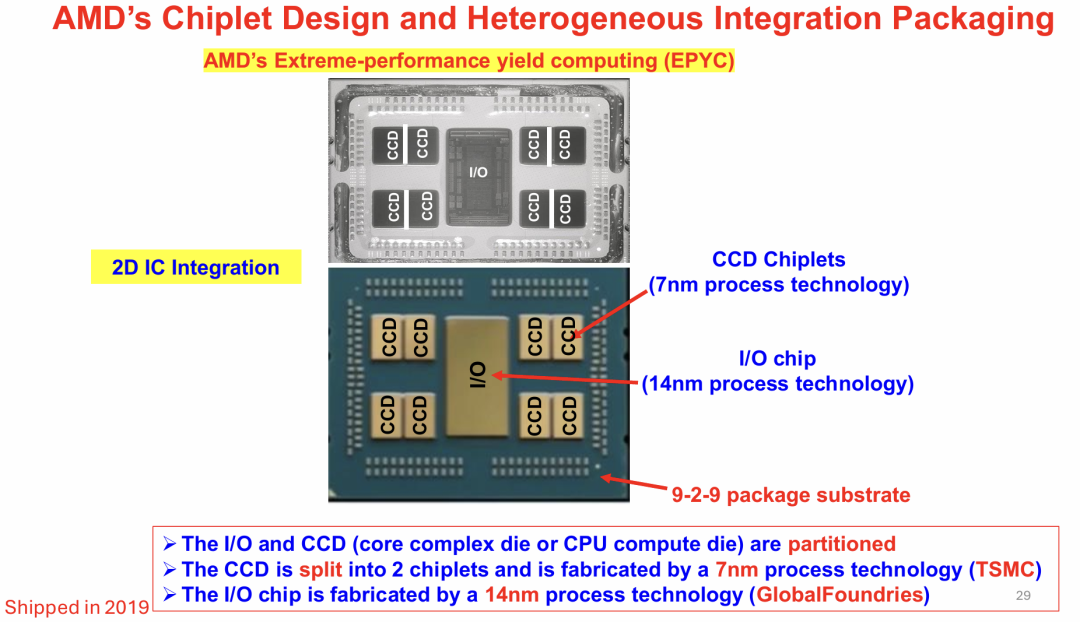

2D集成代表構建更復雜方法的基礎。這涉及將多個芯片并排放置在共同基板上,允許增加功能性,同時保持相對簡單的制造工藝。先進例子包括AMD的EPYC處理器,展示了復雜的2D Chiplet集成,通過將輸入/輸出功能與計算核心復合管芯分離。

圖6:AMD的2D Chiplet集成方法,其中I/O和核心復合管芯被分離并使用不同的工藝技術制造(I/O使用14nm,計算核心使用7nm),然后在共同基板上集成

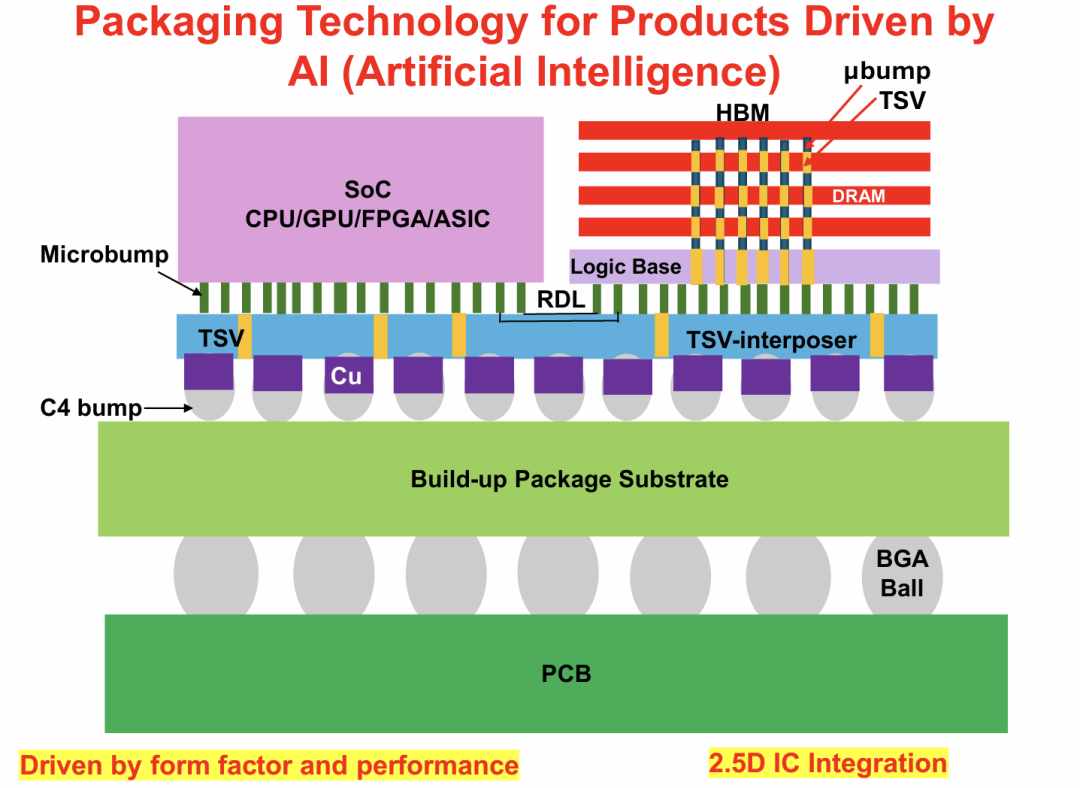

向2.5D集成的進展引入了硅通孔技術和Interposer,允許Chiplet之間更密集的互連,同時保持并排放置的基本概念。這種方法對于人工智能工作負載驅動的高性能計算應用特別有價值,其中處理器和內存之間的帶寬要求超過了傳統封裝方法能夠提供的能力。

圖7:2.5D集成的關鍵組件,包括TSV-Interposer、微凸點、C4凸點,以及邏輯和內存元件在共同Interposer基板上的排列

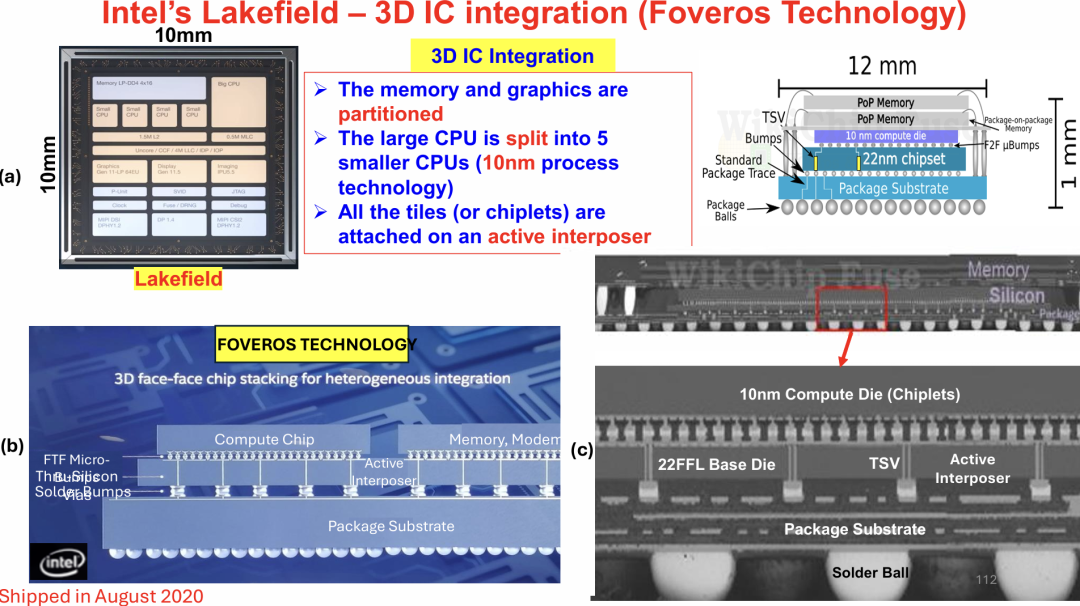

3D集成代表空間高效封裝的終極表達,其中Chiplet垂直堆疊以創建真正的三維系統。英特爾的Foveros技術和Lakefield處理器體現了這種方法,展示計算Chiplet如何堆疊在有源Interposer上以創建緊湊的高性能系統。

圖8:英特爾使用Foveros技術的3D IC集成方法,其中10nm計算Chiplet使用面對面微凸點和硅通孔堆疊在22FFL基礎管芯上

04先進基板技術

支持這些復雜集成方法的基板技術代表電子產業中最先進的制造工藝。這些基板必須不僅提供機械支撐和電氣連接,還要提供熱管理、信號完整性,以及跨多個電壓域和頻率范圍的功率傳輸。

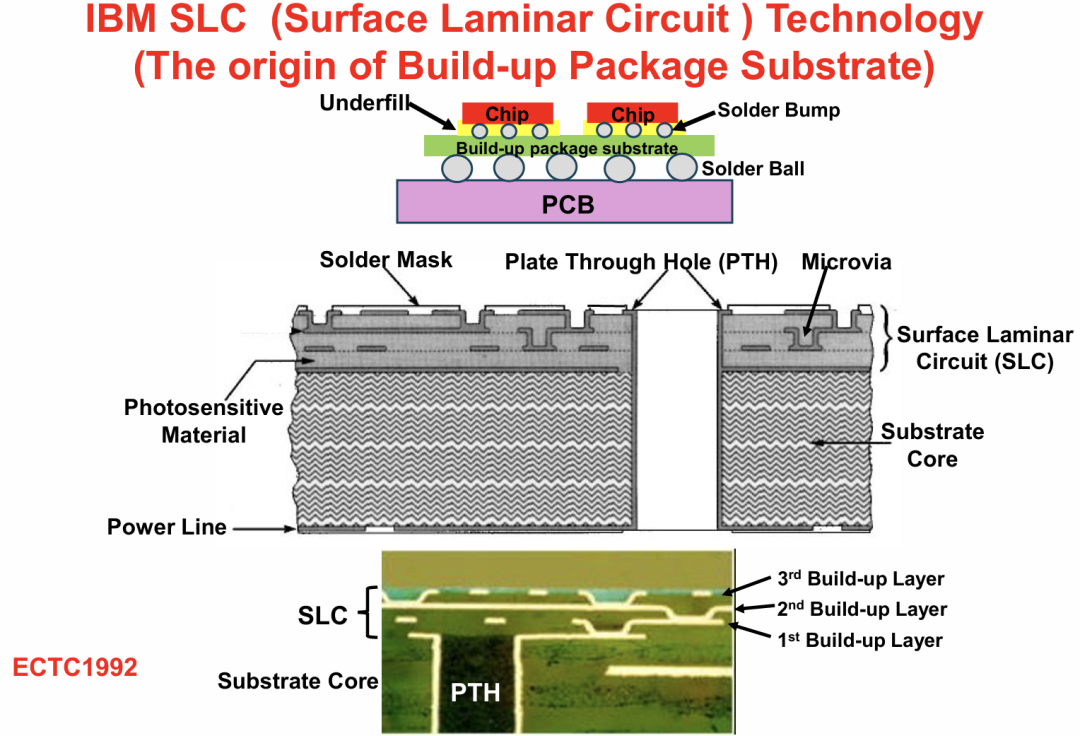

構建封裝基板形成許多先進封裝應用的基礎。這些多層有機基板使用先進材料和制造工藝來實現細間距互連,同時保持可靠運行所需的機械和熱性能。從簡單印刷線路板到具有多個再分布層的復雜構建基板的演進代表了數十年的材料科學和制造工藝發展。

圖9:顯示構建封裝基板的結構,說明實現高密度封裝的多個層、微通孔和通孔互連

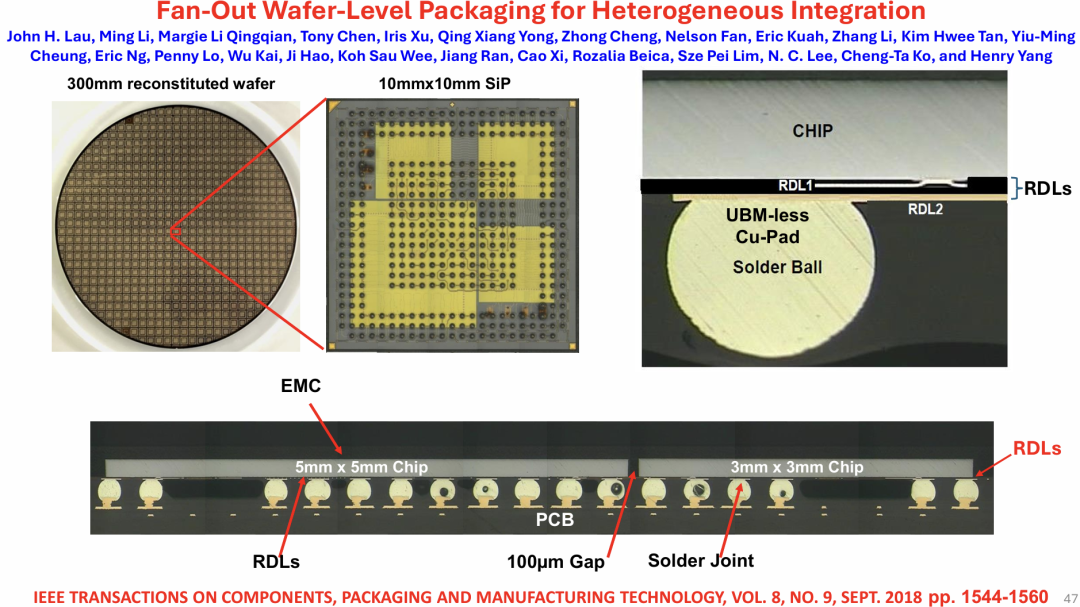

扇出封裝技術代表基板技術的另一個關鍵進展。這些方法使用再分布層將芯片的輸入/輸出能力擴展到其物理邊界之外,實現更高的引腳數和更好的熱性能。從晶圓級到面板級扇出封裝的進展提高了面積效率并降低了成本,同時保持扇出方法的技術優勢。

圖10:扇出晶圓級封裝集成多個不同尺寸的芯片,通過再分布層連接并封裝在環氧模塑化合物中

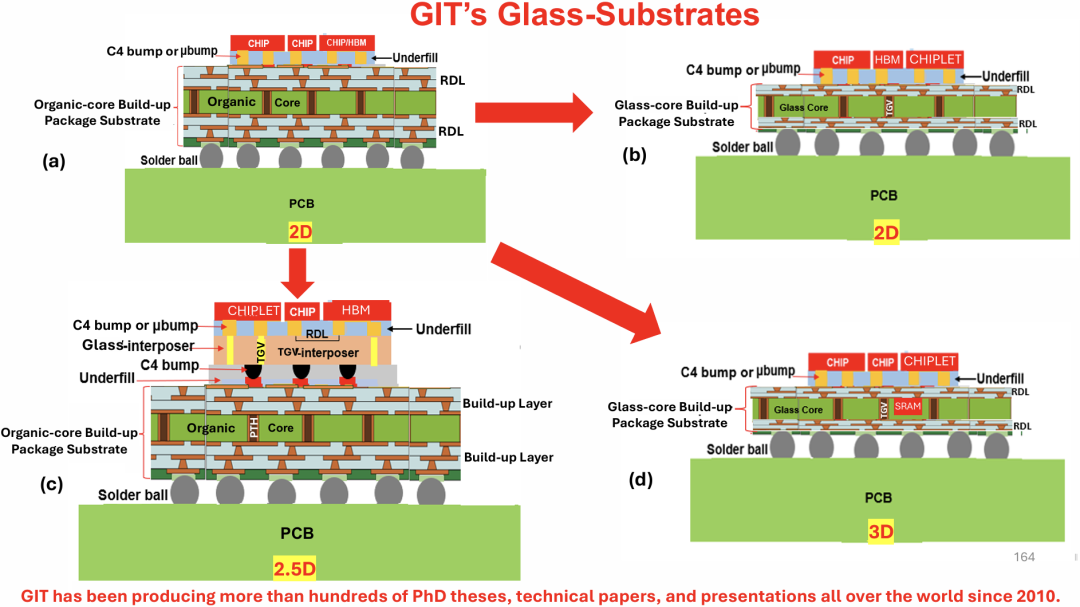

玻璃芯基板代表下一代封裝應用最有前景的新興技術之一。與有機基板相比,這些基板提供卓越的平整度、尺寸穩定性和熱性能,實現更精細間距的互連和更大的封裝尺寸。通玻璃孔技術和兼容處理方法的發展使玻璃基板對高性能應用越來越可行。

圖11:比較玻璃芯和有機芯構建基板,顯示玻璃芯如何實現不同的集成方法,包括2.5D TSV-Interposer和直接芯片貼裝

05混合鍵合和先進互連技術

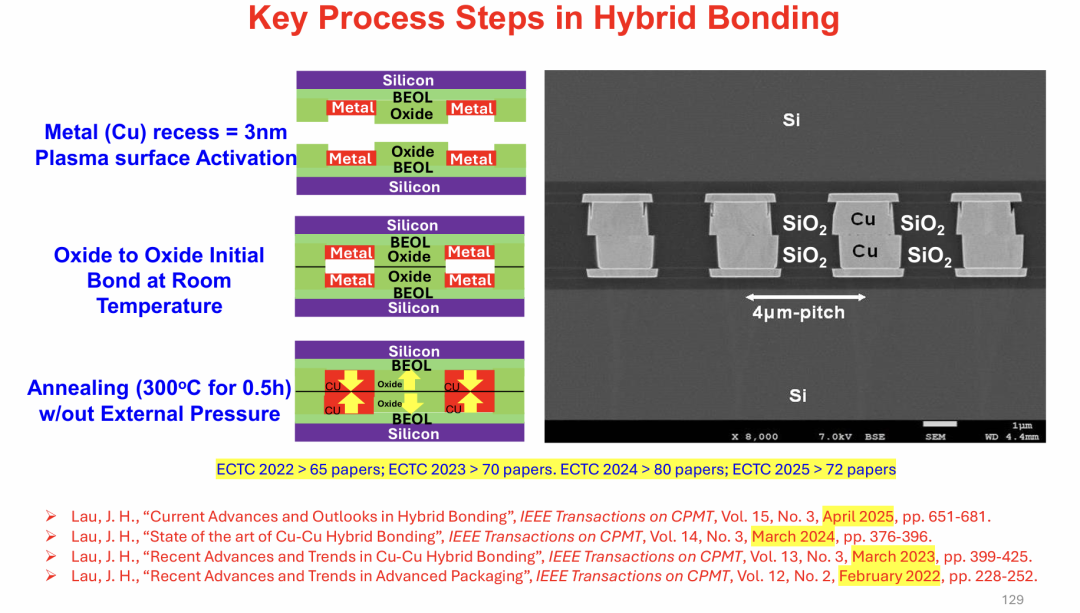

向更精細間距互連的演進推動了混合鍵合技術的發展,消除了對焊料凸點的需求,轉而采用直接金屬對金屬連接。銅對銅混合鍵合代表高密度互連技術的當前最高水平,實現以微米為單位測量的連接間距,而不是傳統焊料基方法典型的數十或數百微米。

圖12:混合鍵合的關鍵步驟,包括室溫下的氧化物對氧化物初始鍵合,然后退火以在無外部壓力的情況下創建金屬對金屬連接

混合鍵合的優勢超出了簡單的間距縮減。消除焊料凸點減少了寄生電感和電容,改善了高頻下的電氣性能。直接金屬連接還提供卓越的熱導率,使高功率Chiplet能夠更好地散熱。這些優勢使混合鍵合對包括高帶寬存儲器集成和高性能計算Chiplet在內的先進應用必不可少。

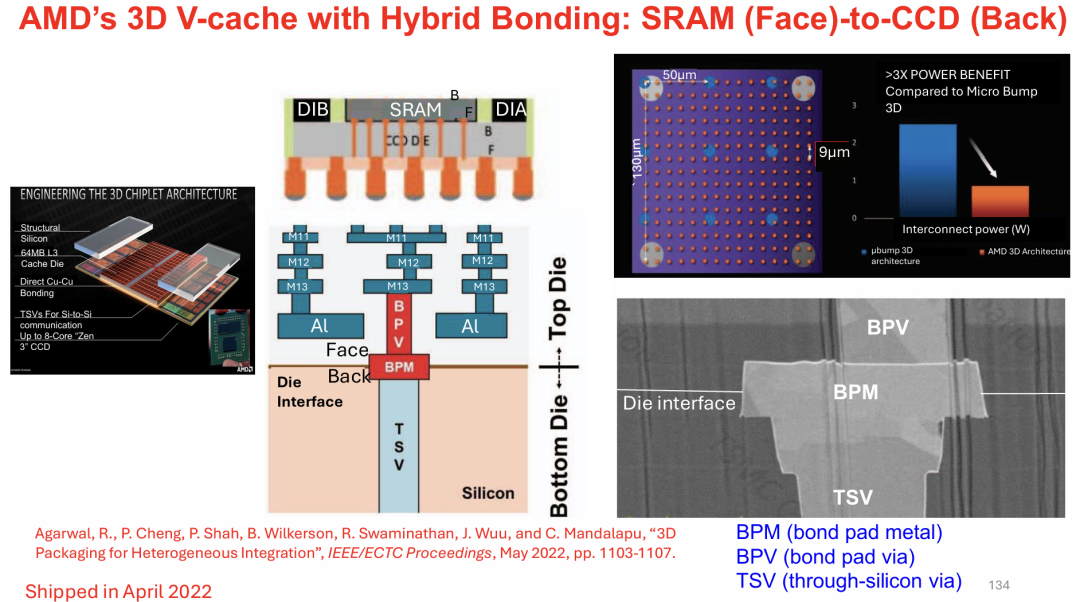

多家公司已成功在生產應用中實施混合鍵合。索尼的CMOS圖像傳感器是最早的商業應用之一,展示了堆疊傳感器架構的晶圓對晶圓鍵合。最近,AMD使用臺積電的混合鍵合技術創建了3D V-cache結構,顯著改善了某些工作負載的處理器性能。

圖13:AMD實施的3D V-cache混合鍵合,其中SRAM緩存管芯與CPU核心面對背鍵合,通過直接銅對銅接口連接

06光電共封裝和光電子技術集成

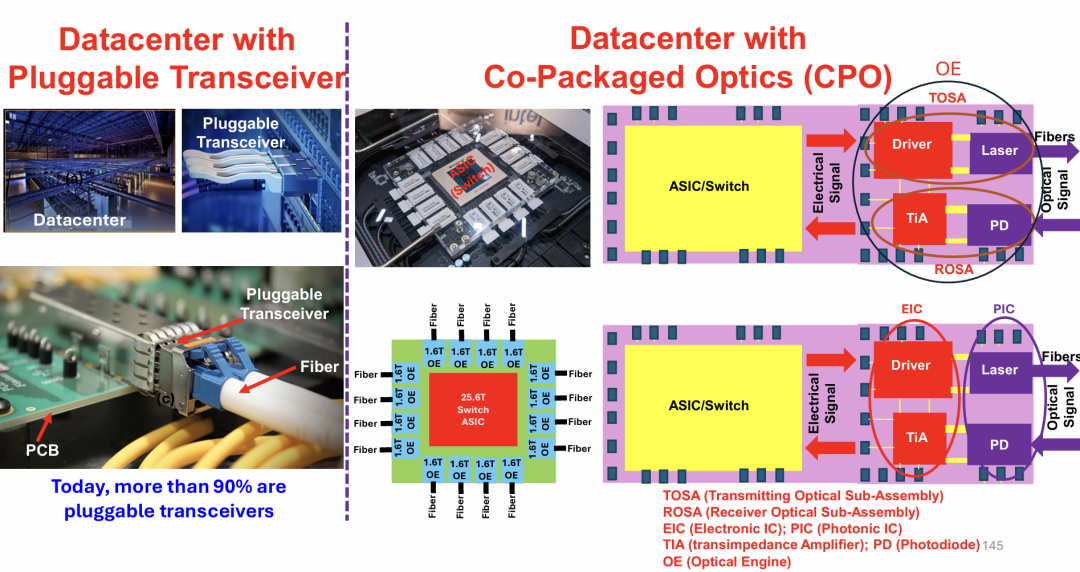

現代數據中心和高性能計算應用不斷增長的帶寬需求推動了光電共封裝技術的發展。這些方法在封裝級別集成光電子技術和電子元件,與傳統可插拔光收發器相比,降低了功耗并改善了性能。

圖14:從可插拔收發器到光電共封裝的演進,說明光引擎如何直接與交換機ASIC集成以降低功耗并改善性能

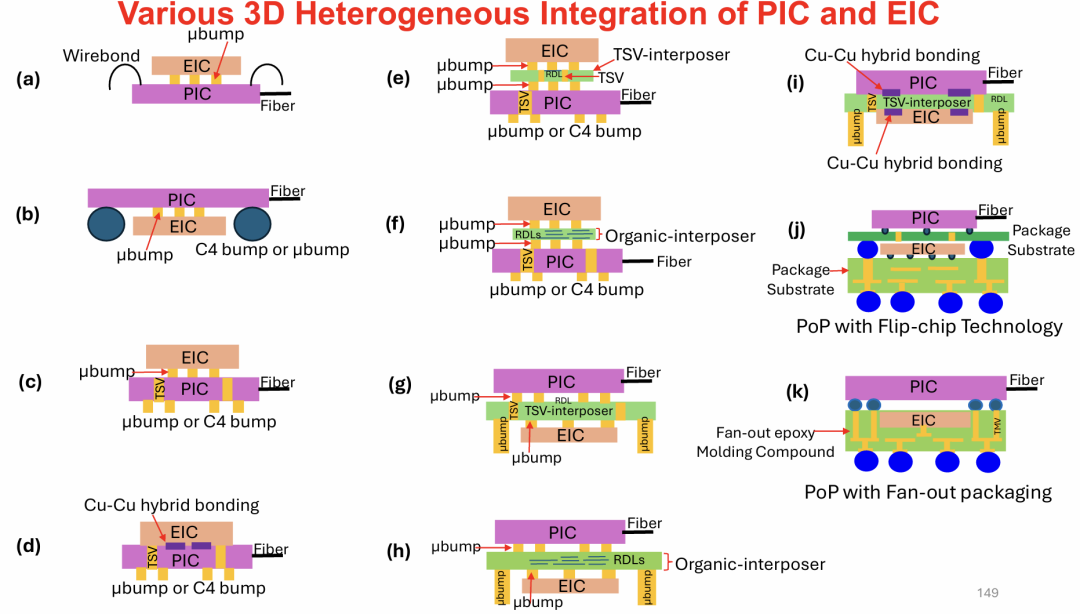

光電子集成芯片和電子集成線路的3D異構集成代表目前產業面臨的最復雜封裝挑戰之一。這些系統必須同時管理高速電信號、光信號、熱耗散和機械穩定性,同時保持光耦合和對準所需的精度。

圖15:集成光電子集成芯片(PIC)和電子集成線路(EIC)的不同方法,包括各種鍵合技術、Interposer方法和堆疊配置

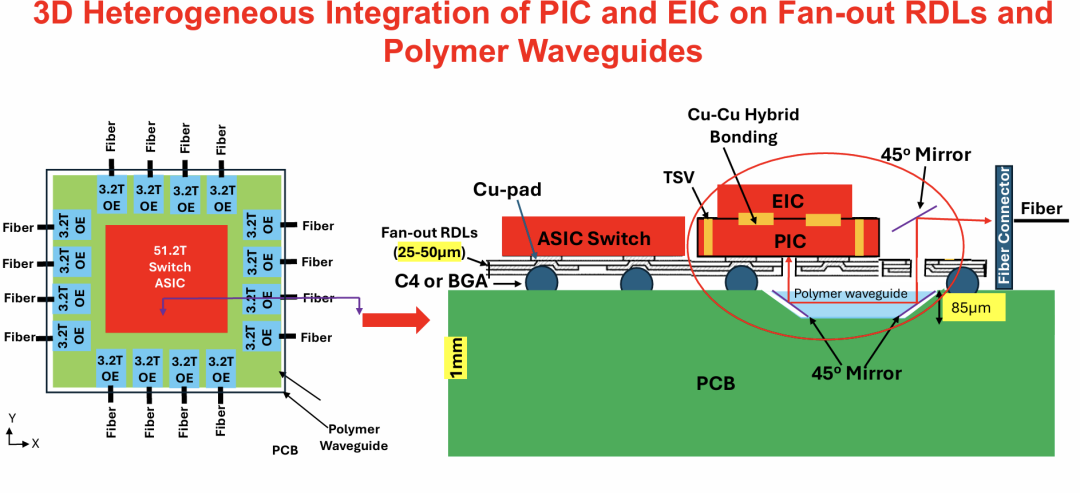

先進的光電共封裝實現融合了復雜的基板技術,包括嵌入式聚合物波導、具有集成光路由的玻璃Interposer,以及多個功能模塊的3D集成。這些方法能夠創建使用分立元件無法實現的系統,同時提供下一代應用所需的性能和功率效率。

圖16:使用嵌入式聚合物波導、45度反射鏡和光電子技術與電子元件3D集成的先進光電共封裝實現

07未來趨勢和新興技術

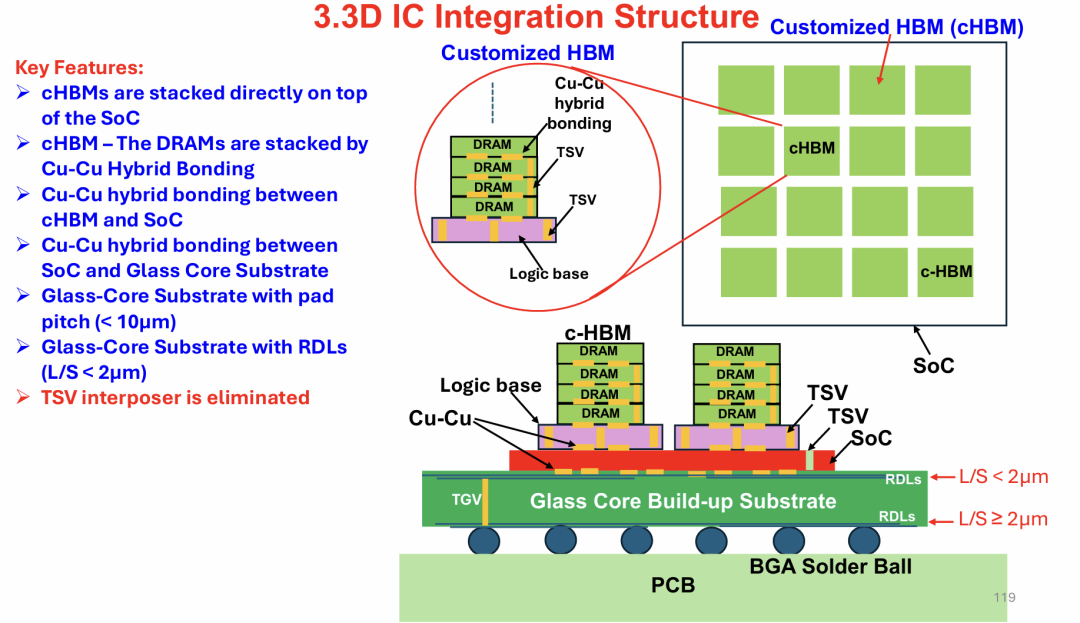

半導體封裝產業持續快速演進,幾個新興趨勢指向更復雜的集成方法。3.3D和3.5D集成技術的發展代表封裝復雜性的下一個前沿,結合Chiplet設計的優勢與先進3D堆疊和混合鍵合技術。

定制高帶寬存儲器代表先進封裝近期最重要的發展之一。這些方法使用混合鍵合技術將DRAM堆疊直接集成到計算Chiplet上,消除對單獨Interposer基板的需求,同時改善性能并降低功耗。

圖17:定制HBM集成的結構,顯示DRAM堆疊如何使用銅對銅混合鍵合直接鍵合到玻璃芯基板上的系統級芯片器件

玻璃基板技術與先進再分布層工藝的集成創造了以前不可能實現的高密度封裝新方法。這些基板提供亞二微米線寬和間距幾何所需的平整度和尺寸穩定性,同時支持3D路由的通玻璃孔技術。

這些技術的持續演進將創建具有集成和性能水平的系統。產業路線圖指向到2030年包含超過一萬億晶體管的封裝,這只有通過Chiplet設計方法學、先進基板技術和3D集成方法的復雜結合才能實現。

隨著這些技術成熟并得到更廣泛采用,將為利用異構集成獨特優勢的新類別應用和系統創造條件。不同工藝技術、Chiplet架構和先進封裝方法的結合為系統設計師提供了在針對特定應用需求優化性能、功耗和成本方面的靈活性。這種靈活性代表Chiplet和先進封裝技術的真正價值,使在傳統單片芯片設計約束下不可能的創新得以實現。

關于我們:

天府逍遙(成都)科技有限公司(Latitude Design Automation Inc.)是一家專注于半導體芯片設計自動化(EDA)的高科技軟件公司。我們自主開發特色工藝芯片設計和仿真軟件,提供成熟的設計解決方案如PIC Studio、MEMS Studio和Meta Studio,分別針對光電芯片、微機電系統、超透鏡的設計與仿真。我們提供特色工藝的半導體芯片集成電路版圖、IP和PDK工程服務,廣泛服務于光通訊、光計算、光量子通信和微納光子器件領域的頭部客戶。逍遙科技與國內外晶圓代工廠及硅光/MEMS中試線合作,推動特色工藝半導體產業鏈發展,致力于為客戶提供前沿技術與服務。

-

半導體

+關注

關注

336文章

30092瀏覽量

259366 -

封裝

+關注

關注

128文章

9160瀏覽量

148058 -

chiplet

+關注

關注

6文章

485瀏覽量

13528 -

異構集成

+關注

關注

0文章

40瀏覽量

2256

原文標題:Chiplet與異構集成的先進基板技術

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

半導體芯片先進封裝——CHIPLET

北極雄芯開發的首款基于Chiplet異構集成的智能處理芯片“啟明930”

chiplet是什么意思?chiplet和SoC區別在哪里?一文讀懂chiplet

先進封裝Chiplet的優缺點與應用場景

Chiplet和異構集成對先進封裝技術的影響

Chiplet和異構集成時代芯片測試的挑戰與機遇

Chiplet主流封裝技術都有哪些?

華芯邦科技開創異構集成新紀元,Chiplet異構集成技術衍生HIM異構集成模塊賦能孔科微電子新賽道

人工智能應用中的異構集成技術

Chiplet與異構集成的先進基板技術

Chiplet與異構集成的先進基板技術

評論