本文轉自:半導體行業觀察

隨著傳統芯片架構在功耗、散熱和空間方面逼近物理極限,一種新型架構正在興起,有望為高性能計算(HPC)開辟一條新的發展道路。這種架構被稱為Chiplet架構(chiplet architecture),它能夠以更低的成本提供比單芯片處理器更高的性能,同時能耗降低高達10倍。這些優勢使得芯片組架構在未來的高性能計算和人工智能(AI)工作負載中具有潛在的優勢。

小芯片架構代表了芯片設計和集成方式的根本性變革。如今,大多數半導體制造商設計大型單片芯片,稱為片上系統 (SoC),將所有必要的組件——例如處理器內核、內存、I/O 驅動器、信號處理器等——集成到單個芯片上。雖然這些組件可能來自不同的供應商,但芯片制造商有責任確保它們能夠協同工作。隨著芯片尺寸的增大,制造成本也會增加,芯片良率則會下降。

為了利用傳統的單芯片進行擴展(或橫向擴展),數據必須離開芯片,通過互連傳輸到其他芯片。如今,隨著人工智能工作負載的不斷增長,客戶在進行人工智能訓練或推理時,必須將大量數據從一個芯片傳輸到另一個芯片。傳輸這些龐大的數據集需要消耗大量電力,并產生巨大的熱量,這兩點都必須通過系統級的電源和冷卻系統來解決。

芯片級互連架構以不同的方式解決尺寸縮放問題。它并非將組件直接焊接在芯片上,而是將這些組件插入埋藏在基板中的標準互連線。通用芯片級互連高速標準 (UCIe)于 2022 年推出,并得到了英特爾、AMD、Arm、谷歌云、Meta、微軟、高通、三星和臺積電的支持。UCIe提供了一種分層架構,可與其他互連標準(例如 PCIe、CXL、NVLink 和 UALink)兼容。

這種芯片組架構帶來了幾個明顯的優勢。首先,它允許用戶將芯片組緊密排列,并通過 UCIe 連接,從而減少數據傳輸(進而降低功耗)。芯片組架構賦予用戶更大的靈活性,允許用戶在系統的特定位置采用特定的處理器,從而更好地平衡性能和成本,而不是被迫使用芯片制造商預先集成到芯片上的組件。

芯片組架構也帶來了制造方面的優勢。較大的芯片尺寸意味著更高的缺陷率,從而降低良率。由于芯片組將各個組件以零散的方式連接起來,因此可以輕松更換有缺陷的組件。這也有助于降低廠商鎖定,使用戶能夠根據自身需求選擇最合適的組件。

Cadence Design Systems公司負責芯片制造商使用的軟件的芯片和 IP 解決方案高級總監 Mick Posner 表示,芯片組的根本優勢在于其封裝級縮放方法。

“任何時候,芯片之間的通信,即使芯片彼此相鄰,都會造成延遲和功耗方面的影響,”波斯納說。“因此,在封裝內部,效率和性能都會大大提高。”

他說,芯片組可擴展性優勢的核心在于它能夠突破光刻掩模的限制。

“實際上,你并不是把一個大型的整體設計分割成更小的部分,”Posner告訴HPCwire。“這在10年前或許是起步階段。但現在,芯片組技術可以實現封裝級的擴展,從根本上來說,它創造出的系統規模遠超單個整體芯片所能容納的。”

Posner 表示,雖然芯片組適用于所有領域,但高性能計算領域正在引領普及,因為他們已經觸及了當前芯片設計的物理極限。

“如今,封裝光罩尺寸的芯片組合在一起,帶來了性能可擴展性和更高的效率,因為不再采用傳統的、功耗高的標準芯片間接口,而是轉向像UCIe這樣的芯片間接口,這種接口的功耗特性要好得多,”Posner說道。“你正在使用一套標準設計的芯片構建模塊來構建系統。”

芯片組技術對于超級計算機來說并不新鮮,目前該概念已被應用于百億億次級系統中。橡樹嶺國家實驗室的 Frontier 超級計算機就采用了基于芯片組的設計,并使用了 AMD EPYC “Trento” CPU;而理研的 FugakuNEXT 超級計算機預計也將采用芯片組技術。

人工智能的蓬勃發展迫使計算機制造商另辟蹊徑,以滿足市場對性能的需求。在半導體領域,像英偉達這樣的制造商一直在突破光刻技術的極限,而光刻技術的極限是由在晶圓上蝕刻電路的光刻機的物理能力決定的。英偉達還設計了“超級芯片”,將兩個GPU和一個CPU集成在單個芯片上,以獲得更強大的處理能力;而其他芯片制造商,例如Cerebras,則開始生產超大尺寸的芯片。

Cadence 產品營銷總監 Mayank Bhatnaga 表示,芯片組架構為 AI 和 HPC 站點提供了另一種提供所需處理能力的方式,而無需像圍繞單一需求那樣完全重新設計系統。

“例如,你想提升GPU的速度,但它的速度不夠快。你可以把它升級到非常昂貴、非常新的工藝,比如2納米和1.4納米工藝,”他告訴HPCwire。“但你的I/O接口可能不需要升級,它可以繼續使用3納米或5納米工藝。或者,你的射頻模塊可能升級后并沒有什么好處,那么為什么要花額外的錢重新設計呢?重新設計?直接沿用現有的就好。”

“現在你不用再設計這些無關緊要的東西了,可以專注于你的獨門秘方,”巴特納加繼續說道。“這樣也能加快產品上市速度。”

如今的芯片組架構也支持三維設計,使組件制造商能夠堆疊組件,從而實現更高的計算密度、更低的數據延遲和更低的功耗。當然,這也帶來了更高的成本、更復雜的結構和更大的散熱需求,但天下沒有免費的午餐。

巴特納加表示:“3D技術離我們并不遙遠。人工智能工廠和人工智能數據中心是這類應用的最大市場,因為只有他們才有能力為這類活動提供資金。任何新技術創新都始于那些有能力且財力雄厚的早期探索者。”

Chiplet本質上是用于構建計算機的樂高積木。標準對于確保A公司生產的產品能夠與B公司生產的產品兼容至關重要。Chiplet社區和市場雖然仍處于發展初期,但其核心力量穩固,發展勢頭強勁。下周,Chiplet社區的大部分成員將齊聚圣克拉拉參加Chiplet峰會。Cadence、開放計算項目(Open Compute Project )、Synopsys和Alphawave Semi(已被高通收購)的高管將發表主題演講。

Bhatnaga表示,采用UCIe是建立芯片組標準的核心,因此也是擴大芯片組社區規模和范圍的關鍵。他還指出,芯片社區中有些人對采用UCIe持謹慎態度。他說,供應商希望確保他們在UCIe上的投資能夠獲得回報。

“UCIe的普及對芯片市場來說確實是一件好事,”Bhatnaga說道。“隨著UCIe的普及,人們相信,如果他們在芯片上使用UCIe,以后也能在其他項目中與其他合作伙伴一起使用。這確實很有幫助。”

來源:編譯自hpcwire

-

芯片

+關注

關注

463文章

54200瀏覽量

467999 -

HPC

+關注

關注

0文章

346瀏覽量

25046 -

chiplet

+關注

關注

6文章

498瀏覽量

13627

發布評論請先 登錄

國產DC-DC電源模塊的SYNQOR兼容性設計與產業化挑戰

碳足跡算不清?全鏈路能源系統,一鍵生成碳排報告

解構Chiplet,區分炒作與現實

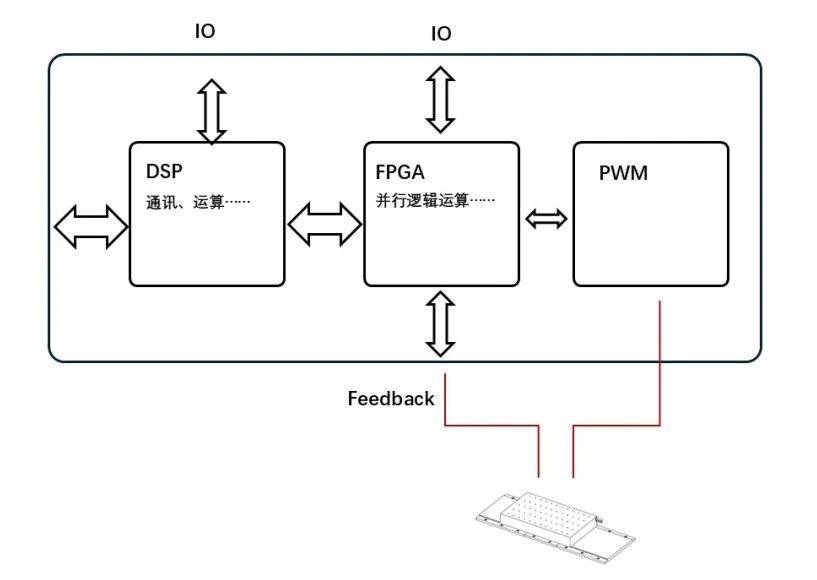

多軸驅動器如何實現高速運行與高精控制雙突破

CMOS 2.0與Chiplet兩種創新技術的區別

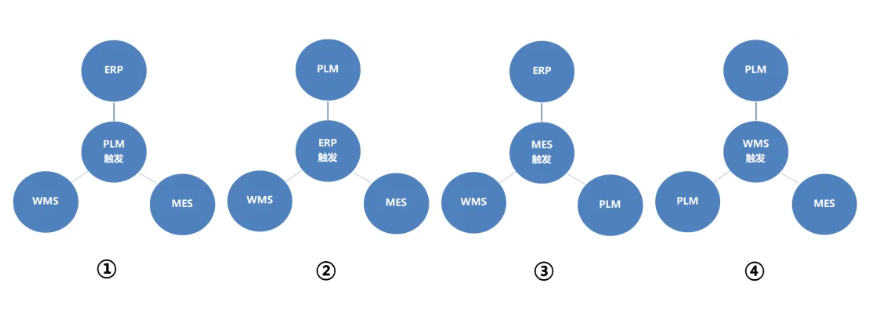

數字化工廠及五大核心系統(ERP、PLM、MES、WMS、QMS)

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

車用虛擬化技術:域控融合的必經之路

芯盾時代零信任安全網關助力智慧校園安全升級

VLA,是完全自動駕駛的必經之路?

MEMS測試設備標準化:降本增效必經之路

從技術封鎖到自主創新:Chiplet封裝的破局之路

Chiplet與先進封裝設計中EDA工具面臨的挑戰

擁抱Chiplet,大芯片的必經之路

擁抱Chiplet,大芯片的必經之路

評論