隨著半導體工藝逐漸逼近物理極限,單純依靠制程微縮已難以滿足人工智能、高性能計算等領域對算力與能效的持續增長需求。在此背景下,Chiplet作為一種“后摩爾時代”的異構集成方案應運而生,它通過將不同工藝、功能的模塊化芯片進行先進封裝集成,成為應對高帶寬、低延遲、低功耗挑戰的核心路徑。

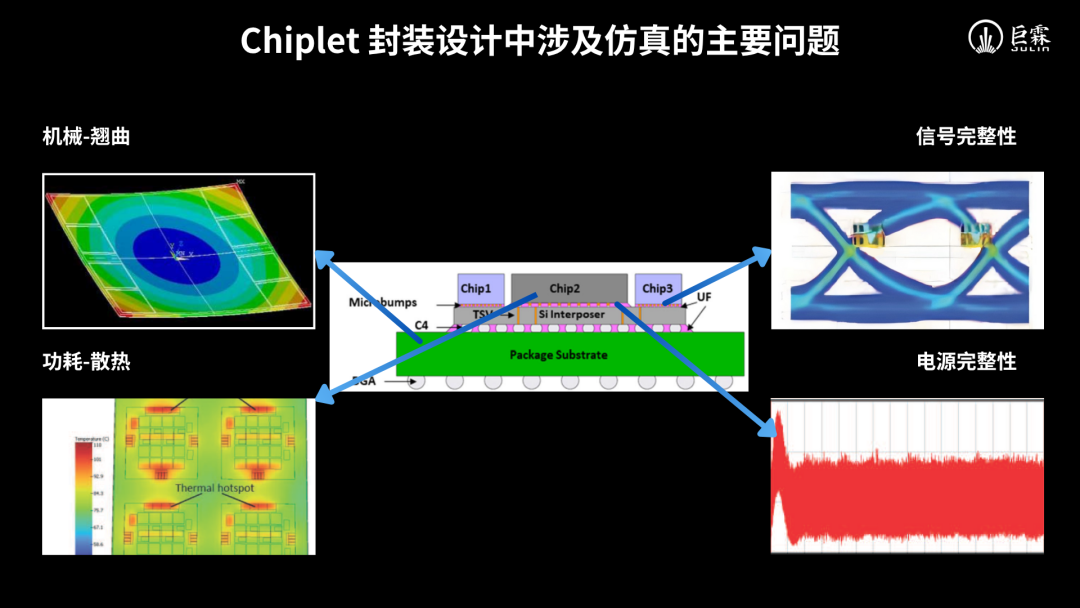

然而,這種架構也將設計的復雜性從單一的硅晶圓擴展至整個封裝系統,使得機械應力、熱管理、信號完整性及電源完整性等多物理場問題相互交織,構成了前所未有的仿真與驗證挑戰。

多物理場問題凸顯封裝設計復雜性

Chiplet的2.5D、3D等先進封裝結構,在提升集成度的同時,也引入了顯著的多物理場耦合效應。

機械翹曲問題因封裝尺寸增大、材料種類繁多及熱應力集中而加劇,其仿真精度高度依賴于對生產工藝和材料屬性的精確建模。

熱管理挑戰則源于多芯片功耗疊加與局部熱密度過高,仿真需精確構建從芯片內部模塊到系統級散熱路徑的完整熱阻網絡。這些機械與熱效應會進一步改變傳輸線的電氣特性,使得純粹的信號分析必須讓位于多物理場協同仿真。

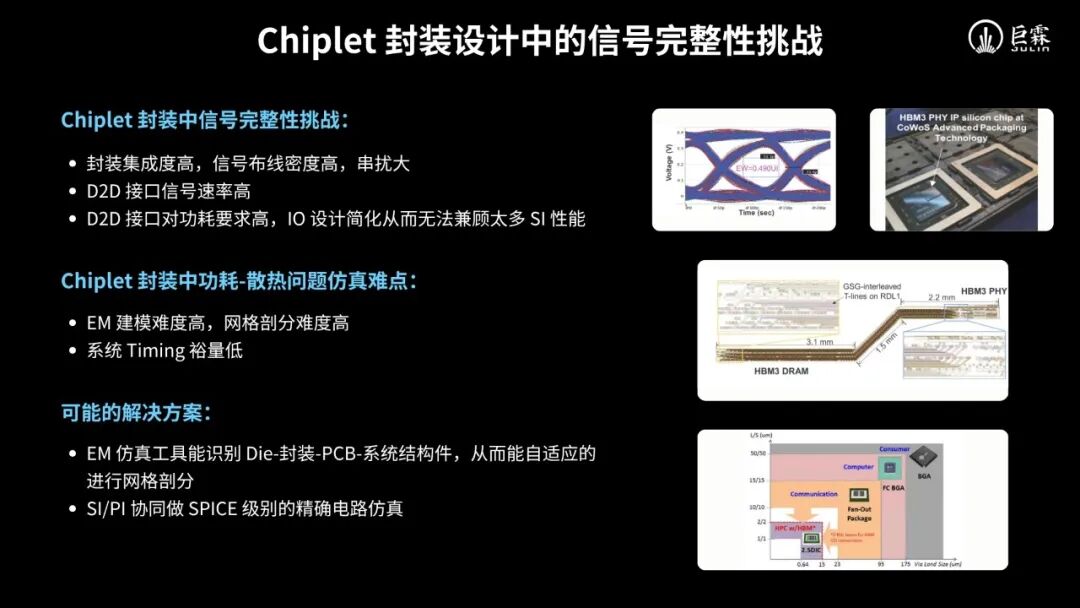

在所有這些挑戰中,信號完整性問題因其直接關系到系統穩定性而尤為關鍵。其首要挑戰在于跨尺度電磁建模難度。同一封裝內,互連結構尺寸從亞微米級別的硅中介層布線,跨越至數十微米級別的有機基板走線,這種尺度差異對電磁仿真工具的網格剖分與算法精度構成了極限考驗。

與此同時,Die-to-Die接口的數據速率正持續攀升。在高布線密度下,嚴重的串擾與傳輸損耗,結合為追求低功耗而簡化的IO設計,使得信號時序裕量被極度壓縮。這要求仿真工具不僅需提供SPICE級別的電路仿真精度,還必須具備SI/PI協同分析能力,以精確評估電源噪聲對敏感時序的影響。

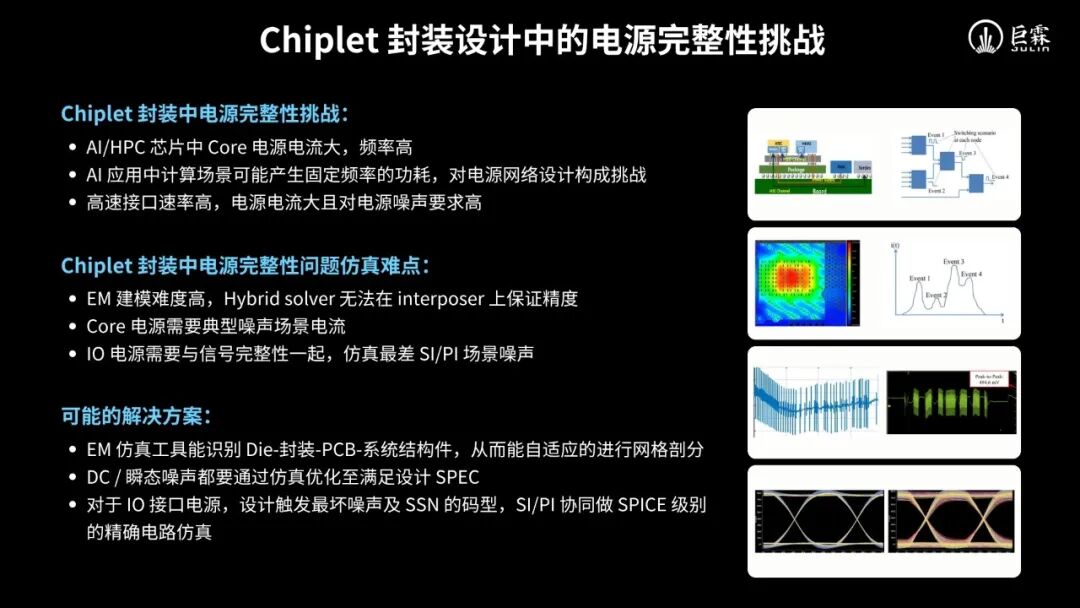

電源完整性同樣面臨嚴峻考驗。AI等應用中的計算單元會產生特定頻率的突發電流,對電源網絡構成周期性沖擊。而高速接口的核心與IO電源則需在承受大電流的同時,維持極低的噪聲水平。

仿真難點在于,電源網絡的電磁建模面臨與信號網絡類似的跨尺度挑戰,且需在時域中模擬最惡劣的工作場景電流。成功的電源完整性仿真依賴于對電源分配網絡頻域阻抗的精準優化,以及通過瞬態仿真對負載突變引發的電壓波動進行充分驗證。

精度與效率的再平衡,驅動工具鏈演進

目前,行業正面臨長瞬態仿真與統計仿真的取舍困境。長瞬態仿真可真實反映物理特性,是精度驗證的基線,但其計算成本隨著信號速率與信道長度的增加而變得難以承受。統計眼圖算法雖能將仿真時間從數周縮短至分鐘級,但其固有的系統性誤差在Chiplet對時序裕量要求極高的背景下已不容忽視。

應對這些挑戰,需要仿真技術棧的整體演進。行業參與者正在探索相應的技術路徑,例如通過高保真電路模型、高精度電磁場模擬及混合求解器來應對跨尺度建模問題。以巨霖科技的SIDesigner平臺為例,通過集成電路級與統計仿真求解器,旨在平衡SI/PI協同仿真時的精度與效率需求,以解決傳統工具在網格剖分適應性與統計眼圖精度等方面的具體痛點。

結語

Chiplet技術將芯片設計的戰場從單一的晶圓擴展到整個封裝系統。在此背景下,信號與電源完整性已不再是孤立的設計環節,而是與機械、熱等因素深度耦合的系統級問題。突破跨尺度電磁建模、實現高效高精度的多物理場協同仿真,已成為推動Chiplet技術持續演進、釋放其全部性能潛力的關鍵所在。業界對新一代EDA工具的期待,正聚焦于其能否在更嚴苛的簽核標準下,真正打通從芯片到封裝乃至系統的全鏈路仿真。

-

仿真

+關注

關注

55文章

4525瀏覽量

138584 -

封裝設計

+關注

關注

2文章

48瀏覽量

12183 -

chiplet

+關注

關注

6文章

499瀏覽量

13635

原文標題:Chiplet封裝設計面臨多維仿真挑戰,信號與電源完整性成關鍵技術瓶頸

文章出處:【微信號:巨霖,微信公眾號:巨霖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

IDT信號完整性產品:解決高速信號傳輸難題

是德DSOX1204A示波器在電源完整性測試中的關鍵優勢

了解信號完整性的基本原理

高頻晶振的信號完整性挑戰:如何抑制EMI與串擾

Samtec虎家大咖說 | 淺談信號完整性以及電源完整性

信號完整性測試基礎知識

Chiplet與先進封裝設計中EDA工具面臨的挑戰

Chiplet封裝設計中的信號與電源完整性挑戰

Chiplet封裝設計中的信號與電源完整性挑戰

評論