優勢

1

EMX 3D Planar Solver 助力客戶實現準確、高容量的 EM 分析,確保硅流片一次成功,加快產品上市

2

EMX 3D Planar Solver 以出色的結果達到三星認證標準

中國上海,2023 年 11 月 15 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布,CadenceEMX3D Planar Solver 現已通過 Samsung Foundry 的 8nm Low Power Plus(LPP)先進制程工藝認證。EMX Solver 是市面上首個獲得此認證的電磁(EM)求解器,成功達到三星的各項認證標準。雙方的共同客戶可以安心使用 EMX Solver 用于先進節點設計,進行高度準確的高容量 EM 分析,避免不良寄生效應和串擾效應。Cadence 和 Samsung Foundry 此次最新合作將助力客戶實現硅流片一次成功,更快將新產品推向市場。

要想順利完成模塊級和芯片級分析及簽核,擁有一個經過代工廠認證的 EM 建模引擎非常重要。精確的 EM 模型是設計前沿應用 IC 的基礎。三星在認證過程中制造并測量了各種配置的電感器,EMX Solver 在所有類別中都表現出了極高的準確度。

有了 EMX Solver,客戶可以仿真大型電路模塊,分析無源元件的 EM 行為特性,并分析片上寄生效應。該求解器可以分析先進節點工藝的制造效果,包括與寬度和間距有關的效果。EMX Solver 與所有 Virtuoso產品一起無縫集成在 Cadence 定制/模擬設計流程中,包括基于 AI 的 Virtuoso Studio,以及 Virtuoso Analog Design Environment 和 SpectreRF Option。

“通過與 Cadence 的長期合作,我們為客戶提供了其所需的強大工具,實現先進節點設計硅流片一次成功,”三星電子代工設計技術團隊副總裁兼主管 Sangyun Kim 說道,“我們之間建立了穩定的合作關系,確保客戶可以使用 EMX 3D Planar Solver 加速完成我們 8nm LPP 制程技術的設計收斂。”

“如今的先進制程節點設計必須能夠克服串擾效應,”Cadence 全球副總裁兼多物理場仿真事業部總經理 Ben Gu 說道,“準確、高容量的 EM 分析非常重要,可以保護這些設計免受不良寄生效應的影響。Cadence EMX 3D Planar Solver 進行的 EM 分析不僅是業界的黃金標準,現在更是通過了三星的認證,因此我們的共同客戶可以繼續信心十足地采用先進技術完成設計。”

EMX 3D Planar Solver 支持 Cadence 智能系統設計(Intelligent System Design)戰略,旨在實現系統級芯片(SoC)卓越設計和系統創新。

有關 EMX 3D Planar Solver 的更多信息,請訪問

www.cadence.com/go/EMXSolverCertification

(您可復制至瀏覽器或點擊閱讀原文打開)

關于 Cadence

Cadence 是電子系統設計領域的關鍵領導者,擁有超過 30 年的計算軟件專業積累。基于公司的智能系統設計戰略,Cadence 致力于提供軟件、硬件和 IP 產品,助力電子設計概念成為現實。Cadence 的客戶遍布全球,皆為最具創新能力的企業,他們向超大規模計算、5G 通訊、汽車、移動設備、航空、消費電子、工業和醫療等最具活力的應用市場交付從芯片、電路板到完整系統的卓越電子產品。Cadence 已連續九年名列美國財富雜志評選的 100 家最適合工作的公司。如需了解更多信息,請訪問公司網站 www.cadence.com。

2023 Cadence Design Systems, Inc. 版權所有。在全球范圍保留所有權利。Cadence、Cadence 徽標和 www.cadence.com/go/trademarks 中列出的其他 Cadence 標志均為 Cadence Design Systems, Inc. 的商標或注冊商標。所有其他標識均為其各自所有者的資產。

往期推薦

Cadence 推出 EMX Designer,在片上無源元件綜合上提供超過 10 倍的性能提升

Cadence 加強其 Tensilica Vision 和 AI 軟件合作伙伴生態,為先進的汽車、移動、消費和物聯網應用提供更好的支持

Cadence 推出 Allegro X AI,旨在加速 PCB 設計流程,可將周轉時間縮短 10 倍以上

? ? ? ? ? ? ? ? ? ? ? ? ? ?

?

?

? ? ? ? ? ? ? ? ? ? ? ? ? ?

?

?

原文標題:Cadence EMX 3D Planar Solver 通過 Samsung Foundry 8nm LPP 工藝技術認證

文章出處:【微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

-

Cadence

+關注

關注

68文章

1011瀏覽量

146905

原文標題:Cadence EMX 3D Planar Solver 通過 Samsung Foundry 8nm LPP 工藝技術認證

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

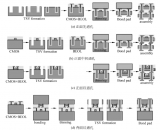

2D、2.5D與3D封裝技術的區別與應用解析

技術資訊 I 多板系統 3D 建模,提升設計精度和性能

SOI工藝技術介紹

Cadence AI芯片與3D-IC設計流程支持臺積公司N2和A16工藝技術

iTOF技術,多樣化的3D視覺應用

3D 共聚焦顯微鏡 | 芯片制造光刻工藝的表征應用

Cadence攜手臺積公司,推出經過其A16和N2P工藝技術認證的設計解決方案,推動 AI 和 3D-IC芯片設計發展

答疑 | 3D打印的模型能當日常餐具使用嗎?這安全嗎?

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實現流片成功

Cadence EMX 3D Planar Solver 通過 Samsung Foundry 8nm LPP 工藝技術認證

Cadence EMX 3D Planar Solver 通過 Samsung Foundry 8nm LPP 工藝技術認證

評論