半導(dǎo)體封裝技術(shù)的發(fā)展始終遵循著摩爾定律的延伸與超越。當(dāng)制程工藝逼近物理極限,先進(jìn)封裝技術(shù)成為延續(xù)芯片性能提升的關(guān)鍵路徑。本文將從技術(shù)原理、典型結(jié)構(gòu)和應(yīng)用場(chǎng)景三個(gè)維度,系統(tǒng)剖析2D、2.5D及3D封裝的技術(shù)差異。

一、傳統(tǒng)2D封裝的平面集成

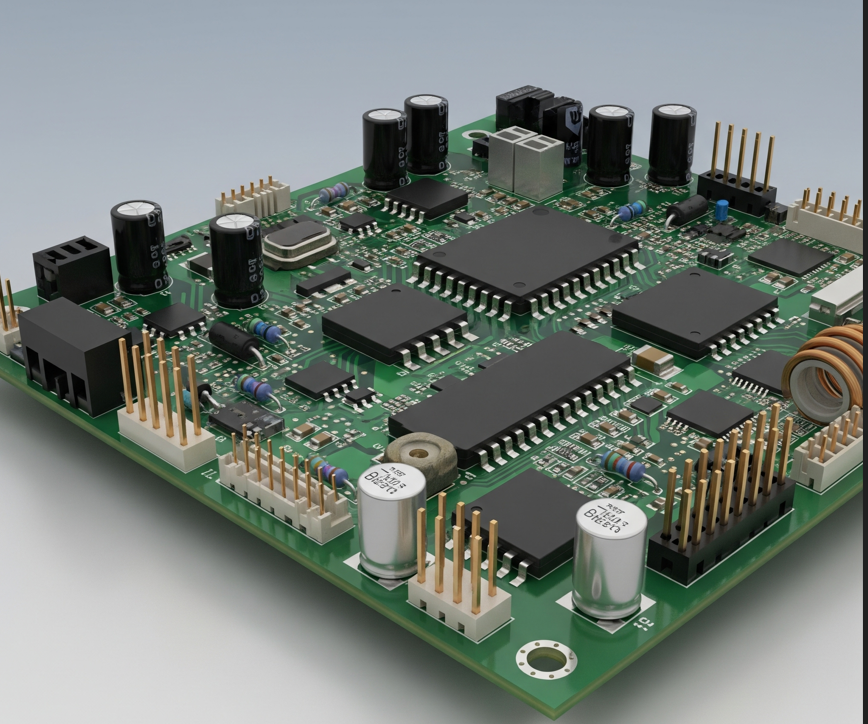

作為最成熟的封裝形式,2D封裝采用引線鍵合(Wire Bonding)或倒裝焊(Flip Chip)方式,將芯片水平排布在基板表面。其核心特征是所有互連都發(fā)生在XY平面內(nèi),通過基板的金屬布線層實(shí)現(xiàn)芯片間通信。以常見的QFP封裝為例,芯片通過金線與外圍引腳連接,最終用環(huán)氧樹脂塑封成型。這種結(jié)構(gòu)優(yōu)勢(shì)在于工藝成熟、成本低廉,但受限于平面布局,當(dāng)集成多顆芯片時(shí)會(huì)導(dǎo)致封裝面積急劇增大,且互連長(zhǎng)度增加帶來信號(hào)延遲和功耗上升問題。目前仍廣泛應(yīng)用于微控制器、功率器件等對(duì)集成度要求不高的領(lǐng)域。

二、2.5D封裝的硅中介層革命

2.5D封裝通過引入硅中介層(Interposer)實(shí)現(xiàn)技術(shù)躍遷。該技術(shù)將芯片并列排布在帶有TSV(硅通孔)的硅中介層上,中介層既提供高密度互連布線,又通過TSV實(shí)現(xiàn)垂直方向的電氣連接。以臺(tái)積電CoWoS(Chip on Wafer on Substrate)為例,其硅中介層布線密度可達(dá)傳統(tǒng)PCB基板的100倍以上,線寬/線距可做到0.4μm/0.4μm。這種結(jié)構(gòu)特別適合HBM高帶寬內(nèi)存與邏輯芯片的集成,例如NVIDIA的GPU通過2.5D封裝將HBM2顯存與GPU核心的互連距離縮短至毫米級(jí),帶寬提升至傳統(tǒng)GDDR方案的5倍以上。但硅中介層的制造需要額外工藝步驟,導(dǎo)致成本比傳統(tǒng)封裝高出30-50%。

三、3D封裝的垂直堆疊突破

3D封裝直接將芯片或芯片層在Z軸方向堆疊,通過TSV實(shí)現(xiàn)垂直互連。三星的V-NAND閃存就是典型代表,其將128層存儲(chǔ)單元垂直堆疊,單元間距僅幾十納米。更復(fù)雜的3D IC如AMD的3D V-Cache技術(shù),采用混合鍵合(Hybrid Bonding)將64MB SRAM緩存堆疊在計(jì)算芯片上方,互連密度達(dá)到每平方毫米10^6個(gè)連接點(diǎn),訪問延遲降低至傳統(tǒng)片外緩存的1/3。這種結(jié)構(gòu)最大優(yōu)勢(shì)是大幅縮短互連長(zhǎng)度,使得數(shù)據(jù)傳輸能耗降低達(dá)90%,但面臨散熱挑戰(zhàn),需要配套開發(fā)微流體冷卻等新型散熱方案。

四、技術(shù)對(duì)比與演進(jìn)趨勢(shì)

從集成密度來看,2D封裝互連密度約102/cm2,2.5D提升至10?/cm2,而3D封裝可達(dá)10?/cm2。在延遲表現(xiàn)上,3D封裝的垂直互連使信號(hào)傳輸路徑縮短至微米級(jí),較2D封裝的厘米級(jí)路徑有量級(jí)提升。成本方面,2D封裝每平方厘米約0.1美元,2.5D因硅中介層升至1-2美元,3D封裝則需3-5美元。當(dāng)前技術(shù)演進(jìn)呈現(xiàn)融合態(tài)勢(shì):Intel的Foveros Direct技術(shù)將2.5D中介層與3D堆疊結(jié)合,實(shí)現(xiàn)40μm間距的面對(duì)面鍵合;臺(tái)積電SoIC技術(shù)則通過晶圓級(jí)鍵合使堆疊間隙小于1μm。未來隨著混合鍵合、光互連等技術(shù)的發(fā)展,封裝技術(shù)將繼續(xù)向異質(zhì)集成、超短距互連方向演進(jìn),推動(dòng)算力密度突破新的物理極限。

審核編輯 黃宇

-

封裝技術(shù)

+關(guān)注

關(guān)注

12文章

602瀏覽量

69339

發(fā)布評(píng)論請(qǐng)先 登錄

臺(tái)積電如何為 HPC 與 AI 時(shí)代的 2.5D/3D 先進(jìn)封裝重塑熱管理

西門子Innovator3D IC異構(gòu)集成平臺(tái)解決方案

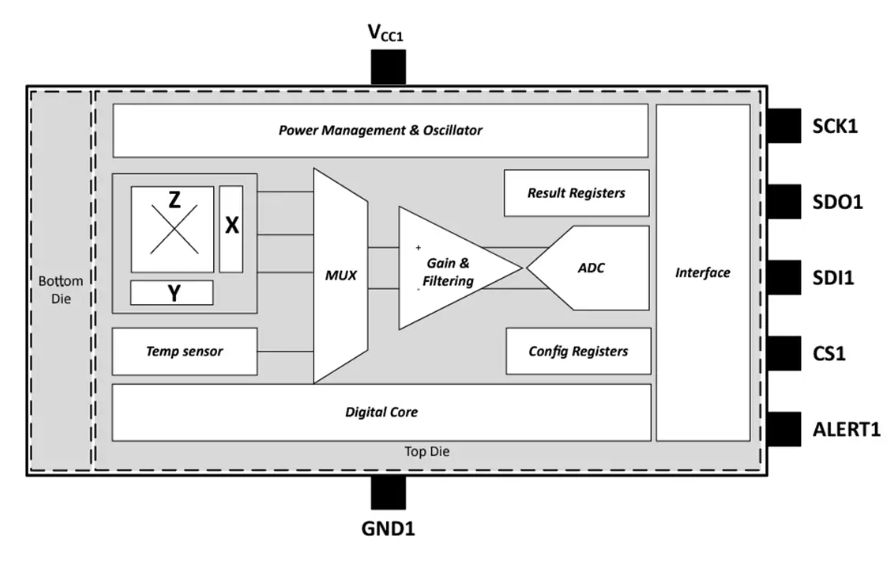

探索TLE493D-P3XX-MS2GO 3D 2Go套件:開啟3D磁傳感器評(píng)估之旅

2025 3D機(jī)器視覺的發(fā)展趨勢(shì)

淺談2D封裝,2.5D封裝,3D封裝各有什么區(qū)別?

Socionext推出3D芯片堆疊與5.5D封裝技術(shù)

玩轉(zhuǎn) KiCad 3D模型的使用

TMAG5170D-Q1 3D線性霍爾效應(yīng)傳感器技術(shù)解析與應(yīng)用指南

iTOF技術(shù),多樣化的3D視覺應(yīng)用

3D封裝的優(yōu)勢(shì)、結(jié)構(gòu)類型與特點(diǎn)

華大九天推出芯粒(Chiplet)與2.5D/3D先進(jìn)封裝版圖設(shè)計(jì)解決方案Empyrean Storm

多芯粒2.5D/3D集成技術(shù)研究現(xiàn)狀

芯原推出面向可穿戴設(shè)備的超低功耗OpenGL ES GPU,支持3D/2.5D混合渲染

HT 可視化監(jiān)控頁(yè)面的 2D 與 3D 連線效果

2D、2.5D與3D封裝技術(shù)的區(qū)別與應(yīng)用解析

2D、2.5D與3D封裝技術(shù)的區(qū)別與應(yīng)用解析

評(píng)論